深海海流计信号处理机硬件平台设计

2020-01-14冯宏

冯宏

(第七一五研究所,杭州,310023)

深海探测技术在海洋技术领域占据重要位置,研究深海海流运动特性,不仅有利于深海探测及海洋资源的开发,而且也能丰富我国的深海海洋数据库,推动我国海洋探测技术领域的快速发展。海流计是对海流的速度及方向等特性进行探测的重要设备之一,目前市场上使用较多的是挪威安德拉公司的Seaguard RCM系列产品,因此研制具有自主知识产权的国产深海海流计对我国海洋仪器的国产化意义重大。本论文依托国家863计划项目研制的6 km级1.5 MHz深海海流计系统。低功耗电子线路设计是深海海流计的关键技术之一,本文重点介绍一种以FPGA+MSP430为架构形式的低功耗信号处理机硬件平台设计。

现场可编程逻辑门阵列FPGA具有丰富的逻辑资源和布线资源、集成度高、功耗低,且并行处理能力强,内部DSP资源丰富,编程简单灵活,运算速度高,广泛应用在高速数字信号实时处理中。微功耗单片机MSP430采用精简指令集结构,具有丰富的寻址方式、简洁的内核指令及大量的模拟指令,处理能力强、运算速度快、功耗超低,且中断源较多,可以任意嵌套,使用灵活方便,非常适合作为低功耗系统的控制单元。

1 总体设计

海流计的基本工作原理是利用声电换能器向海水介质发射声脉冲信号,并接收海水中散射体反射的回波信号,通过分析回波信号的多普勒信息,从而得到海流速度和方向等信息。

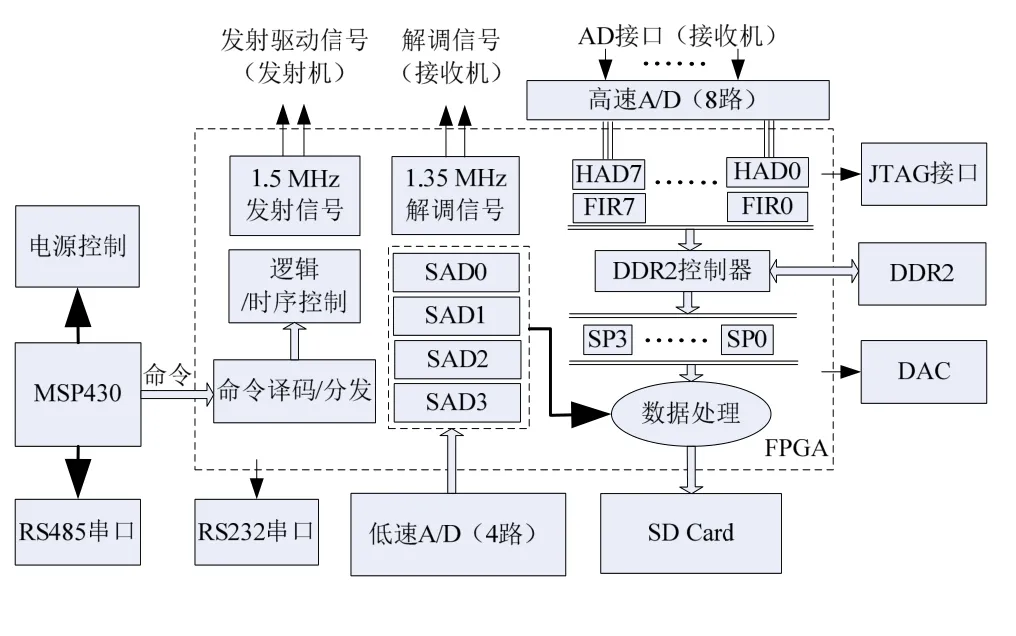

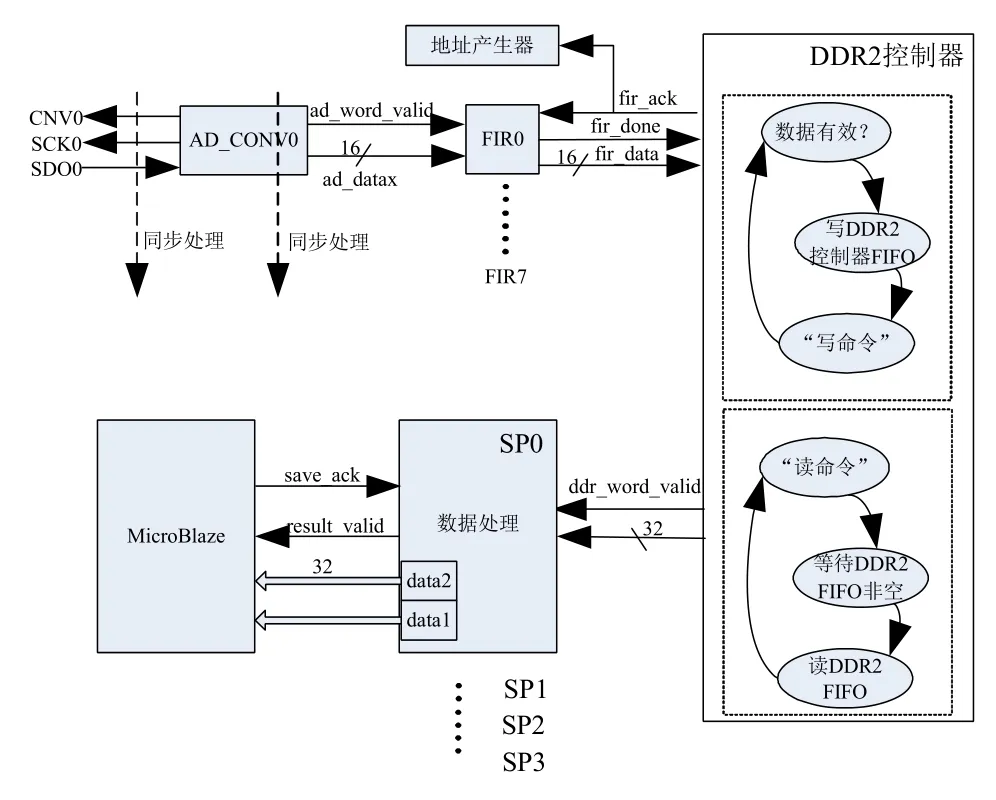

信号处理机是海流计的核心控制及处理中心,由FPGA和MSP430协同设计完成。其中,FPGA是系统的数据处理单元,MSP430是系统的控制单元,系统总体设计框图如图1所示。

FPGA数据处理单元主要完成发射控制、信号采集、流速解算处理及数据存储等功能。本设计选用Xilinx公司Spartan-6系列的XC6SLX45芯片作为主处理器。该芯片是Xilinx公司推出的低功耗FPGA,采用45 nm工艺技术,具有多达43 661个逻辑单元,54 576个触发器和48个DSP48A1 Slices,且提供先进的电源管理技术[1],已广泛应用于工业领域。

图1 总体设计框图

MSP430值班电路单元主要完成电源控制、逻辑控制和上位机交互等功能。本设计选用TI公司的MSP430F5418芯片作为主控制器,该芯片是16位超低功耗微处理器,待机电流小于1 μA[2],且具有强大的处理能力和丰富的片上外围接口,性能稳定,开发简单高效。

2 硬件实现

本设计中的信号处理机硬件平台按功能主要分为电源网络、发射控制、数据采集、数据处理、数据存储和对外通信等模块,下面对主要模块的设计进行简单介绍。

2.1 电源网络设计

电源管理是信号处理机的核心模块之一,在保障电源供给的同时需最大限度的降低系统功耗。深海海流计系统使用一组12 V/100 Ah的锂电池组供电,由电源分机将12 V电源转换成发射分机和信号处理分机所需电平。其中信号处理分机使用5 V供电,并在信号处理板内根据模块需求完成各种电平转换设计。

电源分机中使用电源模块实现信号处理分机5 V供电,为了尽可能的降低电源模块的漏电流,降低系统功耗,我们采用前端关断方式;同时,对信号处理板级的各种电平转换芯片,在选型时均选用具有低功耗模式的可关断型芯片。根据系统运行时序特性,由MSP430完成整机的电源管理控制,以此实现系统低功耗设计。

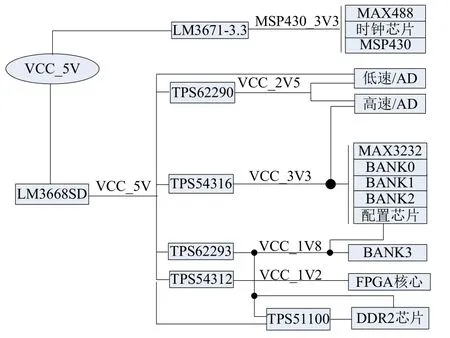

信号处理板内的电源网络如图2所示,多片电源转换芯片组成板内分布式电源网络,提供不同的电源电压标准使电路各模块正常工作与休眠,同时受控于微处理器,实现电源的时序调控。

图2 数字处理电路板内电源网络

FPGA内核采用1.2 V及1.8 V供电电压,IO接口采用3.3 V供电电源。本设计选用TPS54312系列芯片完成1.2 V电平转换设计,选用TPS54316芯片完成3.3 V电平转换设计,TPS62293芯片完成1.8 V电平转换。AD采集采用2.5 V供电,选用TPS62290设计实现。各电平转换芯片设计方式如图3~图5所示。

图3 1.2 V电平设计

图4 1.8 V电平设计

图5 3.3 V电平设计

2.2 采集模块设计

海流计系统发射中心频率为1.5 MHz,在接收机中采用模拟基带正交解调技术将回波信号中心频率搬移至150 kHz后再送入信号处理机进行采集处理。该设计方式能够将超高频回波信号频带搬移至低频段,减小信号处理机A/D采样频率,降低运算量,满足系统低功耗的要求。

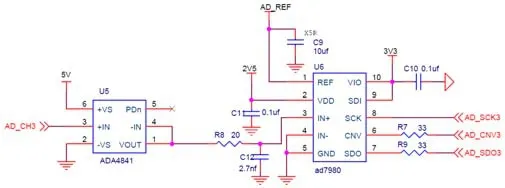

本设计使用AD7980芯片来实现高速AD采集功能。该芯片位宽为16 bit,转换吞吐量为1 Msps,单电源供电,串行输出接口,其连接方式见图6。

图6 AD7980连接方式

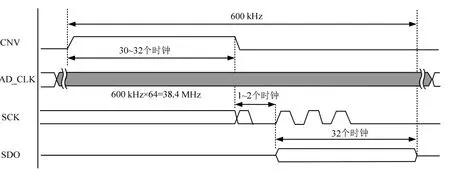

图6中,CNV为转换启动信号,SCK为芯片的串行输入时钟,SDO为转换结果数据输出线。根据系统要求,本设计采用600 kHz采样率完成采集工作。FPGA设计AD采样驱动时序如图7所示。一次完整的AD转换分为三个阶段:启动转换、转换后数据有效、数据读取。各阶段分别设置为30~32个时钟、1~2个时钟、32个时钟,共64个时钟,则转换时钟AD_CLK为600 kHz×64=38.4 MHz,该时钟由FPGA时钟管理模块DCM产生。

图7 AD驱动时序设计

2.3 数据缓存单元DDR2设计

根据系统设计需求,使用DDR2作为外部数据缓存单元。本设计中DDR2芯片选用镁光公司的MT47H64M16,它与FPGA BANK3的MCB连接。数字处理系统的数据流如图8所示,图中为第1路信号数据的采集与存取过程,其它类同。

图8 数据流向示意图

AD采集的数据进入数字滤波器FIR进行滤波处理,然后通过DDR2控制器中的“写操作”存入DDR2存储器;当采集完毕后触发“信号处理SP”模块执行“读操作”,读取DDR2存储器中相应的数据,完成解算并将流速和回波能量等信息存入SD卡中。假设采集数据量为1 200点,DDR2数据存储与读取的在线仿真时序如图9所示。

图9 DDR2的存储与读取过程

图中ad_fir/count为数据点计数,数据采集结束由fir_done脉冲指示,之后进入流速解算过程由argorithm_start高电平指示。

2.4 数据存储单元SD卡设计

SD卡是一种基于闪存技术的存储体,广泛应用于存储设备中。SD卡接口支持两种操作模式,分别为SD模式和SPI模式。SD模式传输速度快,但占用管脚较多,对处理器要求也较高。SPI模式只需要用到SS、MOSI、CLK、MISO及电源管脚,传输简单易操作。在本系统中使用SPI模式进行设计,其电路设计方式如图10所示。

图10 SD卡电路设计

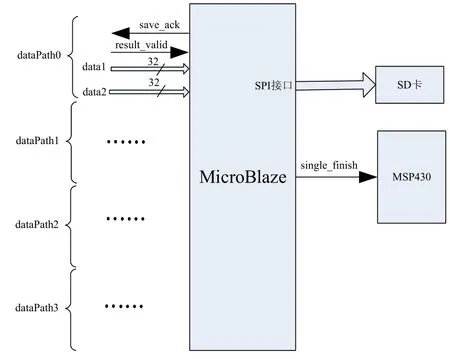

为了便于SD卡文件系统的实现以及部分算法的实现,本设计中FPGA内部使用了软核MicroBlaze进行设计,SD卡通过SPI接口挂接在软核系统上。回波信息经一系列的数据处理及解算后,将最终结果写入SD卡,其接口关系如图11所示。

图11 SD卡接口关系

3 设计验证

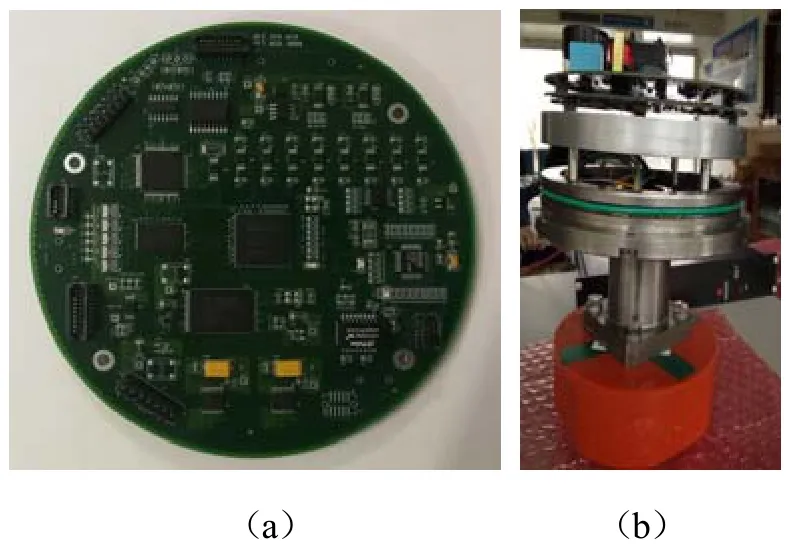

信号处理机硬件平台实物如图12(a)所示,该平台已成功应用于某863项目研制的HLJ6000海流计中,其电子舱如图12(b)所示。

图12 信号处理机硬件平台实物图

为了对系统功能进行验证,在实验室中进行了小信号采集实验。信号发生器产生1.5 MHz/20 mV正弦信号,经1 000倍分压后加载至接收板的基阵信号输入端,信号处理机对接收板输出信号进行采集并存储在SD卡中,采集完毕后读取SD卡数据并通过Matlab绘图分析,试验结果如图13所示。

图13 8路AD采样信号((激励信号1.5 MHz,幅度±20 μV)

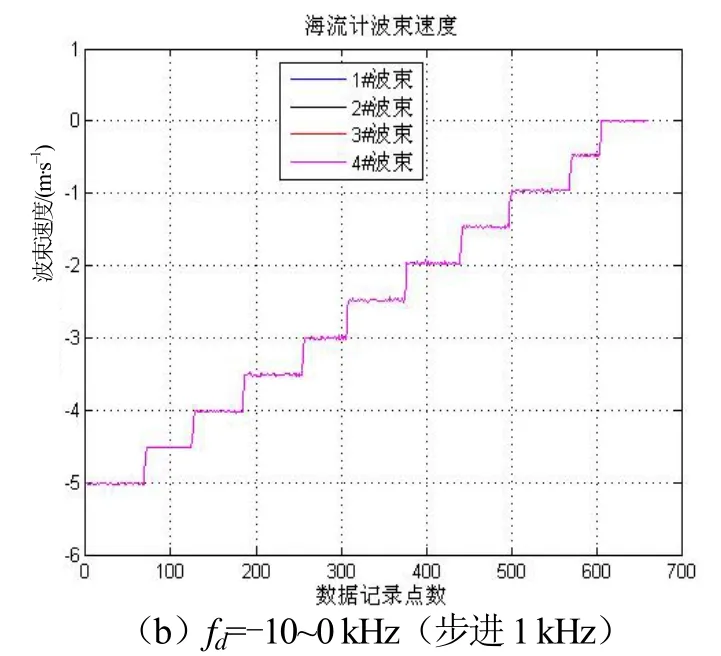

深海海流计发射频率为1.5 MHz,当发射信号选用单频脉冲时,速度测量最大范围可到±5 m/s,多普勒频率极限值±10 kHz。本系统使用加载模拟频偏信号的方式对信号处理机的功能进行验证。手动调整信号发生器输出频率,以1 kHz的步进长度从1 510~1 500 kHz,再从1 490~1 500 kHz逐级跳变,分别模拟0~10 kHz和-10~0 kHz的多普勒频移。

信号处理机采集信号后进行处理并存储在SD卡中,使用Matlab对解算后数据进行分析,结果如图14所示。从实验室验证结果来看,信号处理板采集的8路信号幅度一致,每一对波束信号的相位差基本为90°,信号采集稳定可靠。在输入20 μV、多普勒频偏-10~10 kHz微弱信号情况下,测速结果跟随频偏变化从-5~5 m/s逐级跳变,满足设计要求。此外,在实验室对该硬件平台功耗进行测试,工作功耗约为1.6 W,休眠功耗<5 mW,满足系统低功耗设计需求。

图14 系统功能验证

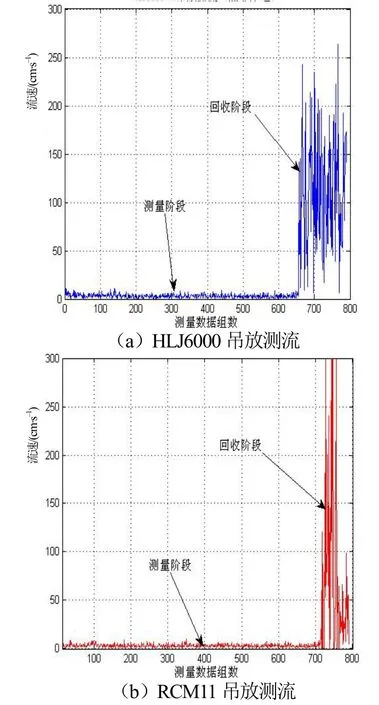

安德拉RCM11深海型海流计是目前市场占比较高的一型深海海流计,为了对系统性能进行验证,对两型设备在千岛湖进行了吊放式静态比测试验。仪器入水约为3 m,测量持续时间约20 min。完成测量比对后,进行仪器回收,通过专用软件将数据导出分析比对速度模值,数据记录结果如图15所示。

图15 千岛湖吊放式比测结果图

从图15可以看出,比对的两型设备测流趋势基本一致,由于后回收RCM11,因此其有效测量时间比HLJ6000长1 min。对测量阶段的数据作进一步细化分析,并进行1 min数据(30点)的滑动平均处理,比对结果如图16所示,数据统计分析如表1所示。由表中的统计结果可知,HLJ6000与RCM11测速结果差异为3.1 mm/s,满足测速精度要求。

图16 千岛湖吊放式比测结果图

表1 静态比对统计分析表

4 结论

本文介绍了一种基于FPGA+MSP430架构的海流计信号处理机硬件设计方式,并已成功应用于某863项目研制设备中,经试验验证,该信号处理机性能稳定可靠。本文介绍的硬件平台所采用的架构形式对各种高频、高分辨率及高处理能力的应用场合均非常适用。该硬件平台对于其它海洋设备的研制也具有一定得参考价值。