一种近阈值电源电压数控振荡器

2020-01-14武建平

武建平,徐 浩

(1. 江苏云巅电子科技有限公司,南通 226001;2. 南京邮电大学电子与光学工程学院,南京 210046)

数控振荡器(Digital-Controlled Oscillator,DCO)在集成电路中应用广泛,作为数字锁相环(Digital Phase Locked Loop,DPLL)的输出信号产生模块,为无线收发系统提供本振信号,为片上系统(System-on-Chip,SoC)提供时钟信号。它由数字控制字对输出信号频率进行调谐,相比传统压控振荡器(Voltage Controlled Oscillator,VCO),数字控制字不易受到工艺偏差、电源电压和温度变化干扰,具有更好的噪声免疫特性。

锁相环[1][2][3][4]被广泛应用于通信、信号处理、调制解调、自动化控制、时钟同步和频率综合等技术中。传统锁相环设计通常采用模拟方法,采用模拟鉴相器和鉴频器、电荷泵、环路反馈信号和压控振荡器。DCO 是宽带DPLL[5][6][7]的关键部件。它根据输入的控制字,产生对应频率的时钟信号,并且数控锁相环的诸多性能如功耗、面积、频率范围等均与DCO 的性能密切相关。作为数控锁相环中最为重要的模块,DCO 必须具有较宽的频率范围和较低的相位噪声性能。常用DCO 有环形振荡器、LC 振荡器两种结构,前者具有高集成度、低功耗、芯片面积小、调谐范围宽等优点。目前大多数设计采用环形振荡器结构以满足DCO在低电压工作,虽然环形振荡器适合于低电压环境工作,但其噪声性能差强人意,要达到与LC 结构振荡器相同的相位噪声性能,环形振荡器需要消耗高达450倍的电流值。因此采用环形振荡器实现DCO 是以牺牲噪声性能来换取低功耗性能。相反LC 谐振腔振荡器虽然使用了电感,电容等较大面积的无源器件,通常具有较大芯片面积和较高功耗,但LC 谐振腔的选频作用使得频谱中的相噪和抖动较低,提供了相对纯净的频谱,适合通信电路中作为本振电路来使用。因此,环形振荡器更适用低功耗,高集成度,对信号相噪要求不高的场合。当需要的噪声性能要求较高时,相比于功耗较大的Colpitts 型LC 振荡器,频谱纯净且中心频率高的交叉耦合型LC 振荡器更加适合。

降低电源电压是降低功耗最直接有效的方法,与模拟锁相环相比,数字模块在低电压下的表现更好,采用近阈值电压能更充分的体现数字电路优势。如何在较低的电源电压下设计DCO 是降低电路功耗的必由之路。针对低功耗、高性能的需求,提出了一款工作在近阈值电源电压环境下的数控振荡器。采用用桥电容技术和电流复用结构,提高了频率分辨率,降低了功耗。

1 DCO 设计与优化

常用数控振荡器[8][9]有环形振荡器、LC 振荡器两种结构,其中环形振荡器具有高集成度、低功耗、芯片面积小、调谐范围宽的优点,但当环形振荡器的频率增加时相位噪声急剧恶化,因此只能用于对本振信号要求不是很严格的场合。与之相比LC 谐振腔振荡器因为使用了电感,电容等较大面积的无源器件,LC振荡器通常具有较大的芯片面积和较高的功耗,但是LC 谐振腔的选频作用使得频谱中的相噪和抖动较低,提供了相对纯净的频谱。

图1 DCO结构简图

图1为一个基本的数控振荡器结构,可变电容阵列的各支路电容由相应的数字信号控制,控制信号di 具有不同的权重,各支路的电容大小是成倍数增长的,分别为C、2C、4C、8C 等,以此类推。高有效位控制大容值电容,低有效位控制小容值电容,振荡器频率分辨率受限于阵列中容值最小的电容。

1.1 基于桥接电容的高分辨率数控振荡器

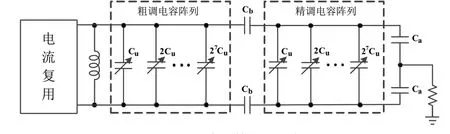

针对Σ-Δ 调制器电路较为复杂,功耗较大,电源电压驱动能力较低,且振荡器工作在高频段,调制器在这种条件下可能会引入额外的噪声甚至影响正常工作的问题。本文采用了如图2所示的数控振荡器。

图2 基于桥接电容的高分辨率DCO

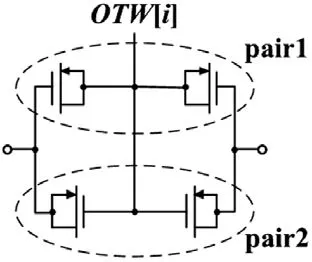

图3 DCO基本电容单元

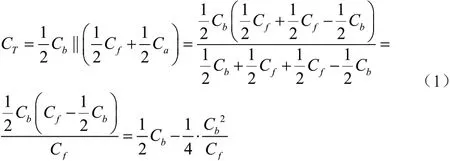

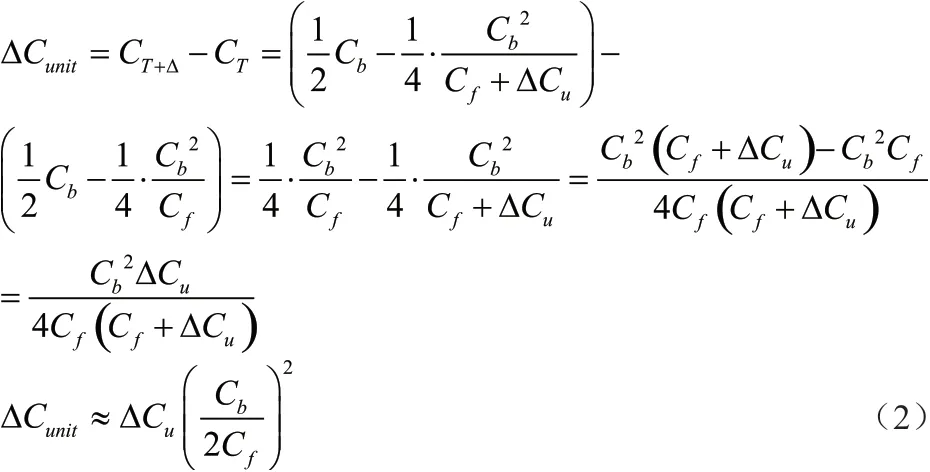

设计采用了桥电容技术[10]和电流复用结构,提高了频率分辨率,降低了功耗,如上图3所示。基于LC 振荡器的DCO 包含两个相同的可调电容阵列,粗调电容阵列和细调电容阵列,它们均由8位数字端OTW 控制。两个反向并联的PMOS 对组成了电容阵列中的基本单位电容单元,其电容值受OTW 控制。当OTW 较高时,pair1部分工作在反型区,而pair2部分工作在耗尽区。当OTW 较低时,pair1部分工作在耗尽区,而pair2部分工作在反型区。因此,通过两个部分轮流工作来减小电容的差值从而减小了最小电容值。在pair1和pair2部分中晶体管的大小分别为800/65和400/65,导致单位电容ΔCu 大约200aF,对应频率分辨率为200kHz/LSB。通过对桥接电容和精调电容阵列总电容微分,计算出精调电容阵列的单位可变电容ΔCunit,推导如下:

式中,CT为接入桥接电容调制后桥接电容与精调电容阵列的总电容;Cf为精调电容阵列的总电容,则经过调制后的最小单位可变电容值为:

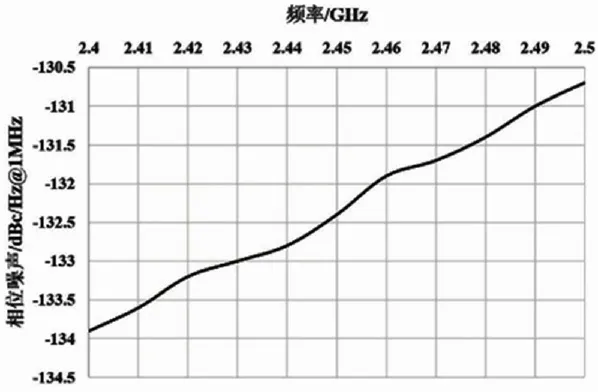

将ΔCu= 200aF,Cb= 12.6Cu和Cf= 63Cu带入式(2)中,可得到单元电容约为2aF,频率分辨率约为3kHz/LSB。理论计算可知,该频率分辨率所产生的相位噪声约为-135dBc/Hz@1MHz。

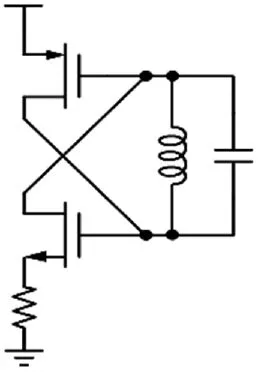

为了降低功耗,在0.6V电压下采用电流复用结构,如图4所示。通过将NMOS 和PMOS 叠加成交叉耦合对,同一电流从近阈值电源流入晶体管,电流被再利用。与交叉耦合型LC 振荡器相比,电流复用只用了一半晶体管即可达到能量补偿效果,降低了近一半功耗。

图4 电流复用结构

1.2 相位噪声分析

传统振荡器的相位噪声[11][12]主要由幅度噪声和相位噪声构成,两种噪声的功率谱密度分别占总噪声功率谱密度一半。假设振荡器输出为正弦信号(3)

幅度噪声一般指输出信号在幅度A(t)上的变化。通常,幅度上的变化与振荡器输出的大信号相比相对较小。锁相环中,幅度轻微变化也能通过锁相环固有的限幅机制使幅度变化逐渐变小最终使振幅趋于平稳,对幅度的轻微变化并不敏感。因此,通常情况下可以忽略幅度噪声,并将A(t)近似为常数。

相位噪声是输出信号在相位上的变化。在无线通讯中对本振电路的相位噪声性能要求较高,是设计振荡器的重要指标。在时域中,振荡器的相位噪声表现为周期不稳定,即输出信号一个周期时间不断变化,在某一范围内抖动,并非严格的每个振荡周期相同。在频域中,相位噪声则表现为频谱中掺杂了不需要的频率。对于理想的振荡器来说,在输出信号中只需要谐振频率,所以频谱是一个单一脉冲,而在实际情况中振荡器的频谱是在中心频率的两边掺杂了许多噪声频率形成了两条“裙带”。混频时,裙带的存在会对收发信号产生严重影响,使信号失真。

图5 DCO量化噪声产生模型

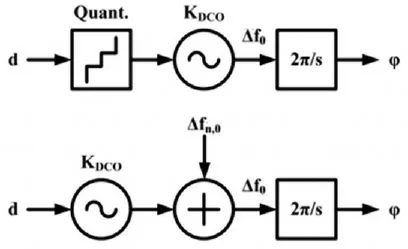

图5所示的模型显示了数控振荡器在有限的频率分辨率下将信号量化从而产生量化噪声的问题。当连续的控制信号d 被量化为离散的数字调谐字后,若数控振荡器的频率分辨率ΔfLSB,在实际测量中,实际的频率会偏移理想频点±ΔfLSB/2。这一频偏随后通过2π/s 积分后从频率转化为角频率。DCO 控制字通常跨越多个量化阶,因此数控振荡器的量化噪声模型可以看作多个量化阶噪声均值,像白噪声加在整个系统中,可以用随机变量Δfn,0来表示其方差

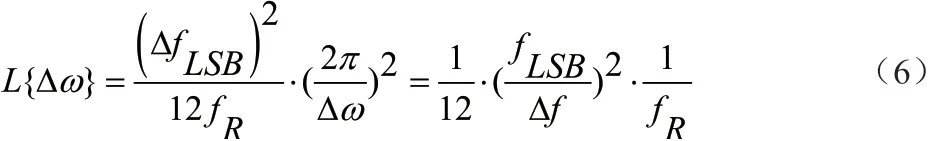

总体的相位噪声功率是在零频率到奈奎斯特频率(参考频率fR的一半)内是均匀分布的[13],因此,Δfn,0的单边频谱密度为:

其中,频偏Δfn,0到转化到相位φ 经数控振荡器输出后,单边功率谱密度变为:

实际上,数控振荡器的输入信号并非理想的脉冲函数,而是用较窄的矩形波,因此式(6)需要再加上一个零阶保持项,后得到量化频率噪声为:

式(7)显示出了与在频谱上与热噪声同样的衰减特性。在不采用Σ-Δ 调试器加抖或其它调制方法下,依靠物理上减小电容值所能达到的最精确的分辨率不能满足5G 通信标准要求。若Σ-Δ 调制器加抖前频率分辨率ΔfLSB为12kHz,参考频率fR为26MHz,计算可得在频偏400kHz 处的相位噪声为-121dBc/Hz,这与数控振荡器本身的相位噪声已经达到相当的数量级。若通过加抖使得分辨率ΔfLSB 提高到到39Hz,这将使量化相位噪声降低48dB,但因为使用了调制器,所以还需计算由调制器产生的噪声。

本文中数控振荡器使用桥接电容来实现频率高分辨率,无需采用调制器来加抖提高分辨率,在提高分辨率、减小量化误差的同时并未引入由调制器产生的噪声。省去了调制器的复杂电路,振荡器整体功耗进一步降低。

2 实验与验证

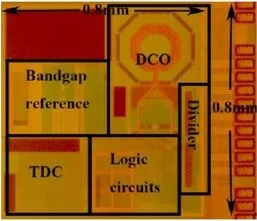

采用优化后DCO 的ADPLL 在130nm CMOS 工艺下流片,核心面积为0.64mm2,版图如图6 所示。其中DCO 工作在0.6V电源下,总电流为1mA,功耗为0.6mW。

图6 ADPLL流片版图

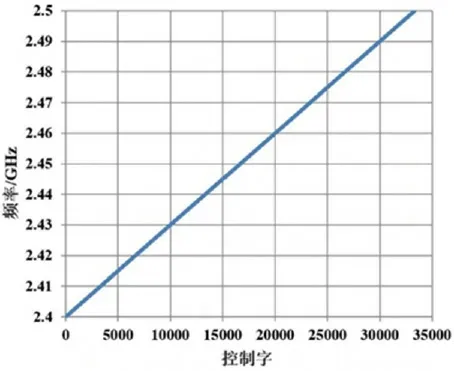

图7 DCO传输曲线图

如图7所示,优化后的DCO 分辨率为3kHz/LSB,调节范围为2.4GHz 到2.5GHz。DCO 相位噪声仿真结果如图8 所示,在调频范围内,其噪声性能随着频率的升高而逐渐变差。在中心频率2.4GHz 处,DPLL 相位噪声性能测试结果如图9 所示。由图9 可以看出在2.4GHz 处,ADPLL 带外相位噪声为-131dBc/Hz@1MHz 频偏,其中大部分带外噪声由DCO 贡献,小部分噪声来自于环路中未被滤波器完全滤除的其它元件的噪声。本文DCO 的最终测试如表1所示。

图8 DCO带外相位噪声测量结果

图9 2.4GHz处相噪测试结果

表1 DCO流片测试结果

3 结束语

本文提出了一款数控振荡器结构采用桥电容技术和电流复用结构,提高了频率分辨率,降低了功耗。在0.6V 低压电源下采用电流复用结构,通过将NMOS 和PMOS 叠加成交叉耦合对,同一电流从近阈值电源流入晶体管,电流重复利用。在低压电源的条件下实现较低功耗。工程流片实测结果显示采用优化后的DCO 基本上实现了低功耗和高性能需求,有一定的工程实用价值和参考意义。