基于微波多层板的Ka频段带状线功分器仿真设计

2019-11-18赵元英夏俊颖

赵元英,夏俊颖

(中国电子科技集团公司第十三研究所,河北 石家庄 050051)

0 引言

目前微波组件的发展趋于小型化、多功能化,组件的功能不断增加,从单通道发展为多通道,从单一的接收或发射功能发展为收发源一体功能,而组件体积要求进一步缩小。因此组件设计由平面向立体寻求空间,趋向于三维集成方式[1-3],把射频前端、信号处理、控制和电源等多种功能垂直堆叠在一起,提高密度,改善层间互联,在小体积下满足多功能化的需求。

在组件三维集成发展思想中,多层电路板的高集成优势凸显。通过将无源电路设计在多层板中间层,有源电路设计在多层板的顶层,可充分利用组件Z方向的空间,缩小X,Y方向的电路面积,立体交叉布局,有利于减小信号串扰,缩小组件体积。文献[4]研究了在多层板中通过金属通孔实现电路板正面和背面的微带线之间的互连。文献[5-6]研究了多层电路板中,中间层带状线和顶层微带线之间的互连。

多层板的应用范围不断扩展。在传统组件设计中,多层板中间层部分常用来传输电源信号、控制信号或C波段以下的微波信号[7],多为低频应用。近年基于组件高度集成的需求,多层板的应用对象和应用频率逐渐拓展,由简单的传输线电路扩展为功分器、耦合器[8]等无源射频电路,由传输低频信号扩展为毫米波高频信号[9-11]。

基于高频率、高集成度应用,本文仿真设计了用于多层板的Ka频段Wilkison带状线功分器[12-15],将功分器端口与微带线进行匹配过渡,并分析了版图设计参数对带状线功分器性能的影响。设计结果表明,带状线功分器在22~37 GHz频带内,插入损耗S21>-3.6 dB,回波损耗S11<-15.3 dB,S22<-17.8 dB,隔离度S23<-15.7 dB,适用于多通道组件中基于多层板实现功率分配。

1 带状线特性

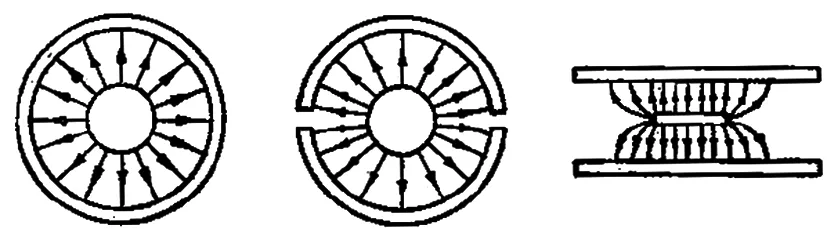

带状线的演变过程为:将同轴线的外导体对半分开,把两半外导体分别向上、下方向展平,内导体做成扁平带状,构成带状线。带状线的电力线是上下左右都对称的,如图1所示。

图1 带状线的演变

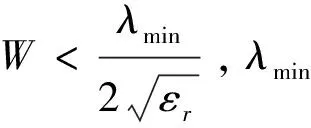

带状线中传输的主模为TEM模。如带状线尺寸选择不当或制造过程中引入不均匀性,就会出现高次模。高次模的产生和传输会影响主模TEM波的正常传输,而且高次模极易引起辐射而使损耗增加。为防止辐射损耗,带状线的尺寸应满足:

③ 接地板的宽度足够大,应大于(2~3)b;

④ 当带状线中接入微波半导体器件时,由于外接器件的不对称,将会激发出高次模。因此,需在不均匀性附近,在带状线侧边加以屏蔽,避免高次模辐射引起的附加损耗。

带状线辐射损耗小,适用于高性能、高Q值的无源微带线元件,如滤波器、耦合器和功分器等。

2 带状线功分器设计

2.1 带状线功分器仿真设计

根据上述带状线尺寸要求,带状线功分器的带线宽度W,两接地板间距b应满足:

接地板的宽度设置为大于(2~3)b。带状线与外界的不对称性来源于与微带线、有源芯片器件的连接,因此在带状线两侧加接地孔对高次模进行屏蔽。

电路板材料选用Rogers 6002,介电常数为2.94。在多种微波电路板材中,RT/duroid 6002是常用的高频电路板材,它是聚四氟乙烯(PTFE)树脂材料,在PTFE中掺杂了少量的陶瓷粉,介电常数低,损耗小,电气和机械性能优异,极适宜高频应用。由于RT/duroid 6002在Z方向上的热膨胀系数(24 ppm/℃)与铜的热膨胀系数(17 ppm/℃)十分接近,多层板中金属化过孔的镀铜层在Z方向上不易开裂,具有高可靠性,因此是制作多层微波板的首选材料。

带状线下层介质厚度为0.254 mm,上层介质厚度为0.127 mm。功分器的输入输出端带状线为50 Ω阻抗匹配,根据电路板的介电常数、电路板厚度和功分器频率等,可计算得到输入输出端口带状线的宽度。在仿真设计中,需对功分器阻抗变换节的宽度和长度进行仿真。

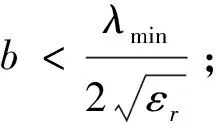

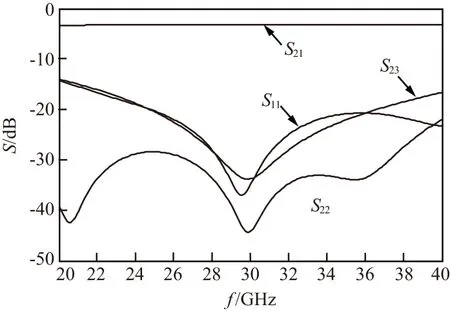

在ADS软件中建立带状线功分器原理图,如图2(a)所示。TL1~TL6为阻抗变换节,在ADS中进行优化仿真,仿真结果如图2(b)所示。

(a)原理图

(b)仿真结果

由图2(b)可见,在22~37 GHz频带范围内,带状线功分器的插入损耗S21>-3.1 dB,回波损耗S11<-16.5 dB,S22<-30.6 dB,隔离度S23<-15.9 dB,仿真结果满足应用要求。ADS仿真基于二维仿真,仿真速度快,而实际的功分器安装在盒体内,具有空气腔体,HFSS软件采用3D有限元分析方法,更适合三维仿真。为精确验证功分器的设计,尽可能得到满足实际应用的电路参数,可将ADS仿真中得到的功分器参数代入HFSS中建立模型,进一步进行仿真。

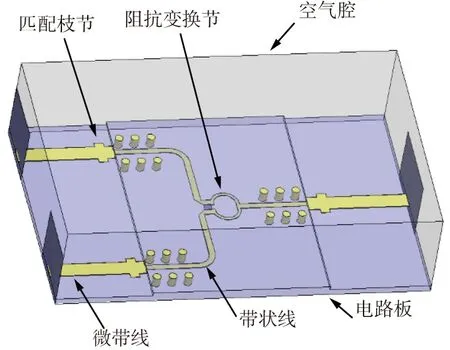

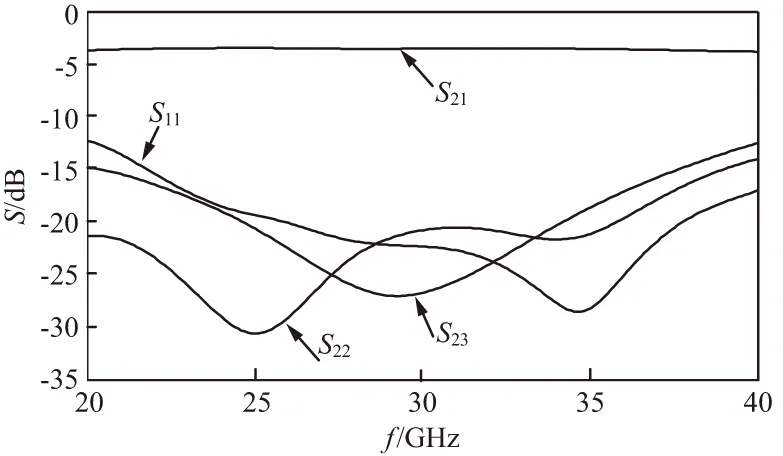

在实际应用中,带状线功分器端口常与微带线连接,依此建立模型,在微带线和带状线之间设计容性匹配枝节进行二者的过渡匹配,并在带状线端口设计2排接地孔,用于屏蔽高次模能量辐射,如图3(a)所示。将功分器阻抗变换节的宽度W1,长度L1,带状线宽度W,匹配枝节的长度Lp,宽度Wp设置为优化变量,在HFSS中进行优化,仿真结果如图3(b)所示。

优化后各参数的值为W1=0.12 mm,L1=1.69 mm,W=0.23 mm,Lp=0.35 mm,WP=1 mm。仿真结果表明,在22~37 GHz频带范围内,带状线功分器的插入损耗S21>3.6 dB,回波损耗S11<-15.3 dB,S22<-17.8 dB,隔离度S23<-15.7 dB,仿真结果满足应用要求。

(a)仿真模型

(b)仿真结果

2.2 设计参数对带状线功分器性能的影响

带状线埋置于上下两层接地面之间,能很好地屏蔽辐射,所以带状线是内部传输线的良好选择。但接地面的接地质量对功分器的损耗和驻波影响很大,通过在带状线两侧设置接地孔贯通上下两层接地面,可实现中间接地层与地的可靠连接,消除寄生平板波导效应,改善功分器的性能。

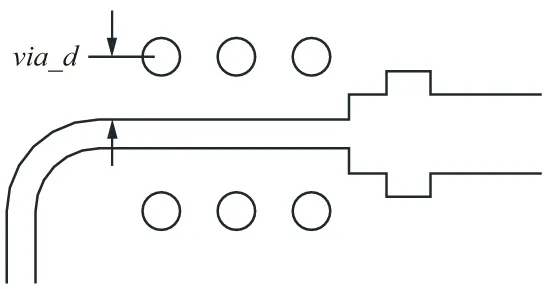

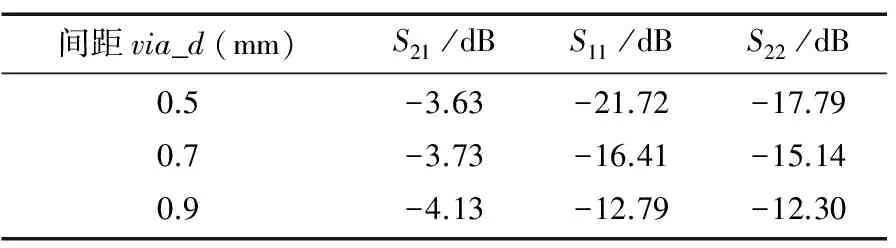

带状线两侧接地孔与带状线距离via_d(如图4所示)需合理设置,via_d过小,会影响带状线的特性阻抗,增大插入损耗、驻波和辐射损耗;via_d过大,有可能激发介质填充矩形波导模式,导致功分器微波性能不稳定。在HFSS中设置不同的via_d值进行仿真,仿真结果显示了via_d的取值对插入损耗S21和回波损耗S11,S22的影响,如表1所示。在功分器版图设计中,via_d设置在0.5~0.7 mm之间即可,如via_d>0.7 mm,功分器在高频段的插入损耗将变大,回波损耗变差。

图4 接地孔与带状线距离示意

表1via_d对指标的影响 (f=37 GHz)

间距via_d(mm)S21/dBS11/dBS22/dB0.50.70.9-3.63-3.73-4.13-21.72-16.41-12.79-17.79-15.14-12.30

在HFSS模型中设置不同的接地孔数量(1~4个)后进行仿真,仿真结果显示,接地孔数量对S参数影响不大。基于可靠性、冗余性考虑,在版图设计中设置3个以上接地孔即可。

3 结束语

本文研究了在多层板中Ka频段的Wilkison带状线功分器的仿真设计。简述了带状线的性能特点和电磁场结构,利用ADS和HFSS软件联合仿真,建立了带状线功分器仿真模型。设计结果显示,功分器在22~37 GHz频带范围内,插入损耗S21>-3.6 dB,回波损耗S11<-15.3 dB,S22<-17.8 dB,隔离度S23<-15.7 dB,实现了应用要求。最后分析了版图参数对功分器性能的影响,便于工程实现。