一种低功耗低成本的数字化查表控制方法

——以Buck转换器的PID控制为例

2019-11-12祝博文刘蒙瑞申树杰

吴 了,祝博文,刘蒙瑞,申树杰

(长沙学院电子信息与电气工程学院,湖南 长沙 410022)

相较于模拟控制器,数字控制器具有高度灵活性、可配置性的优势,因此有更强的环境适应能力.数字控制器一般由MCU、FPGA等控制器实现,被包含在控制环路中,与执行器一道形成反馈,由配置的相应控制规则,控制执行机构得到所期望的控制输出.由于数字控制器处理的是数字信号,而执行器一般接受、处理并输出模拟信号,所以反馈环路中应包括ADC和DAC模块,与数字控制器一起实现所期望的控制输出.

ADC和DAC模块的使用带来两个问题,一是延迟问题,二是精度问题.延迟要么受限于低成本控制器的主频时钟和密集计算,要么受制于ADC和DAC的转换速率;而精度则要考虑ADC和DAC引入的量化误差,和控制器在计算过程中引入的精度损失.这两个问题带来的后果是系统环路稳定性的降低,和执行器控制目标精度的下降.

由于低成本MCU难以实现快速计算,导致环路延迟和精度指标下降,所以文中给出了一种查表控制方法,目的是降低控制器的密集计算,减少延迟,降低功耗和应用成本.文中将以Buck转换器PID控制为例,阐述查表控制方法.

1 数字控制器中各模块设计指标考虑

图1是数字控制Buck转换器的电路模块图,其中数字控制部分包括ADC、DAC和PID计算控制模块,执行器部分则是由功率开关和输出滤波电路组成的一个Buck转换器的功率级.反馈控制通过求转换器输出电压与参考电压的差,得到误差量,然后对误差量根据控制规则经一系列计算后,控制Buck电路的占空比,调节其输出电压,最终使输出电压受控.

图1 数字控制的Buck转换器的电路模块图

要实现Buck转换器稳定可控,要考虑数字控制器中ADC与DAC的性能指标.

首先是ADC位数的确定.事实上,ADC的最低量化级别应小于转换器的输出纹波量,以实现对输出电压的控制.在稳态情况下,由于Buck转换器输出纹波变化范围不大,所以ADC具有较小的动态转换范围,仅需少量控制字进行控制.例如,假设ADC的VREF为3.3 V,对一个Vin=12 V和Vo=5 V的Buck转换器,要使输出电压纹波被控制在1%以内,计算后易得,使用ADC的最小位数是7位.注意到为了减少ADC的延迟,Buck转换器中的ADC一般采用flash ADC或延迟线ADC.

接着是DPWM位数的确定.基于MCU实现的数字控制器,DPWM一般由MCU内置的定时器来实现,等效于数字控制系统中DAC.DPWM的最小量化误差应小于ADC的最小量化误差,以实现输出电压可控.所以随着使用ADC位数的增加,则要增加DPWM的分辨率.这样,为了达到预期更高的开关频率,就必须选择更高主频时钟的MCU,导致一些低成本的MCU不能被使用.因此,最终DPWM使用的位数需要折中.注意到DPWM是设计高开关频率Buck转换器的一个技术瓶颈[1-2].

最后是设计PID控制器,得到预先计算的表值.考虑到一旦环路负反馈稳定后,转换器的输出电压和参考电压将十分接近,两电压求差后的误差量将非常小,接近于0,因此,在一定变化范围内,误差量的变化范围十分有限,完全可以通过建立模型,对整个系统进行数值仿真,将得到的计算值做成表放入低成本MCU中,实时对整个系统进行控制,以降低功耗,达到稳定输出的目的.

图2 Buck转换器在一个开关周期内的两个运行阶段

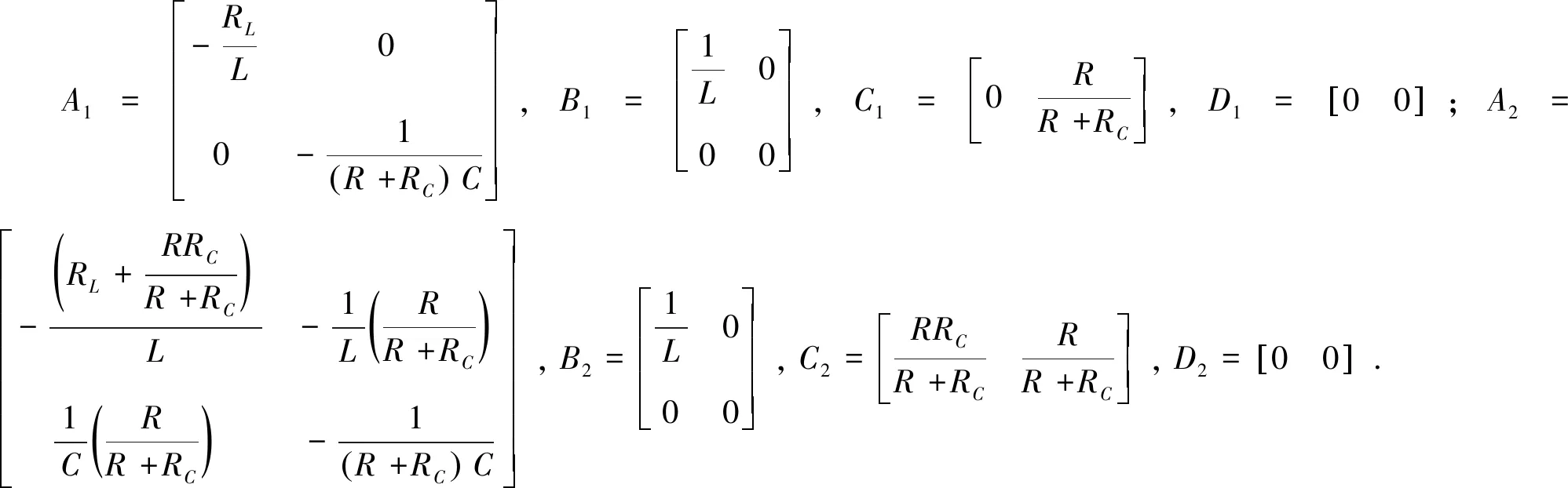

如图2所示为连续导通模式下Buck转换器在一个开关周期内的两个运行阶段.Buck转换器每一运行阶段的状态空间方程可以分别被表示为式(1)与式(2).

2 Buck转换器建模与PID控制器表值获取

为了设计控制规则,需要全面了解执行器的运行特点.Buck转换器本质上是一个非线性执行器.若在一个开关周期内取平均,忽略开关频率以外的高次谐波,则可获得其平均等效模型.

(1)

(2)

在一个开关周期内,通过引入占空比d(t)(0≤d(t)<1),结合式(1)和式(2),对状态空间方程中的系数取平均,易得Buck转换器的平均状态空间模型,由式(3)和式(4)所示.

(3)

(4)

根据式(3)和式(4)容易搭建输入参数为占空比d,Vg和io,输出参数为v和i的仿真模型.基于此模型,根据性能指标,可以设计出所需的PID控制器.PID控制器的传输函数可以被表示为

(5)

这里参数KPA,KIA和KDA分别表示比例、积分和微分参数[3].其中第三项微分项放置一个极点的目的在于限制高频带宽,抑制高频噪声,其中γ为极点因子,调它使传递函数离散化后的极点位于单位圆内,以保证稳定.

不像文献[4]所采用的直接建模方法,为得到PID的表值,文中首先使用式(5)在连续域得到满足Buck转换器性能指标的控制器;然后,对得到控制器的传输函数进行差分离散化[5];最后,根据得到的差分方程,结合Buck转换器模型,进行数值仿真,最终得到PID控制规则的表值.由于误差变化范围不大,所得到表的规模并不大,仅3个数组,每个数组含25个元素.

3 实验验证

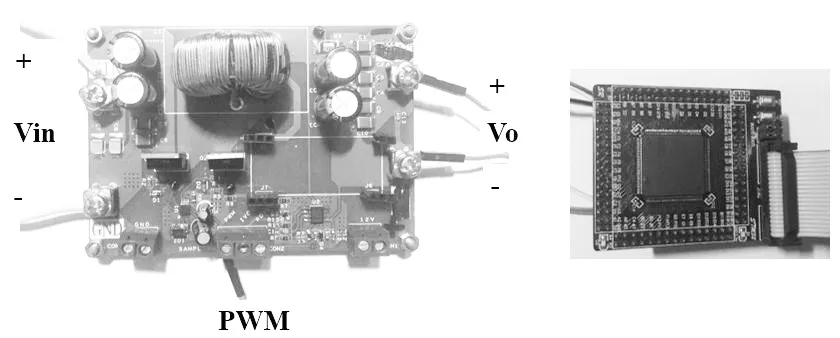

图3 Buck转换器功率级以及相应MCU的实验照片

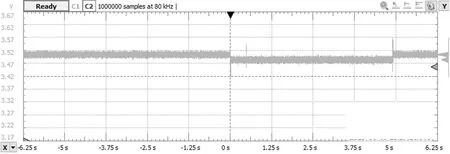

图4 Buck转换器的负载从轻载过渡到重载然后重回轻载时输出电压的实验测试图

图3所示为Buck转换器的功率级以及用于控制的MCU的实验照片.其中,Buck转换器中的滤波电感L=100 μH,滤波电容C=470 μH,开关频率fs=41 kHz.MCU采用意法半导体的STM32F407ZET6实现数字控制部分,MCU用来实现数字控制器的ADC、PID与DAC部分.在这里,ADC位数设为8位,DPWM的时钟频率被设置为42 MHz.MCU中定时器采用向上计数模式,在每次更新中断时使用ADC对转换器的输出电压分别进行一次采样和查表操作,从而更新占空比,反馈控制输出电压.

图4为负载从轻载过渡到重载然后重回轻载时Buck转换器输出电压的实验测试图.可以看到,在轻载时,输出电压为3.5 V,当在图4所示的0 s时刻,负载突然被加载,输出电压下降至3.48左右,并马上稳定,在5s时刻,负载被突然卸载,输出电压重回到3.5 V.运行结果验证了PID查表控制Buck转换器的可行性.

4 结论

文中以PID控制的Buck转换器为例给出了一种低功耗低成本的数字化查表控制方法.该方法在考虑ADC与DAC对Buck转换器性能影响的基础上,通过建模,分析系统环路,预先计算控制规则得到的值,并将值预先储存于RAM表中,依据实际运行过程中转换器输出电压与参考电压的误差量进行查表,通过反馈,稳定转换器的输出电压.文中以Buck转换器为例实现了PID查表控制,验证了该方法的可行性.