锁相解调器锁定指示的快速检测设计与验证

2019-11-12刘苏杰郭金雷

刘苏杰, 冯 旻, 王 蓉, 郭金雷

(1.上海无线电设备研究所,上海201109;2.上海机电工程研究所,上海201109)

0 引言

锁相解调器锁定指示信号在雷达、通信、无线电遥控遥测等领域,用于锁相接收回路扫描停止、工作时序管理、BIT检测等场合。该信号检测时间过长,将直接影响产品进入下一个状态,对于工作时序要求严格的产品尤为重要。

经典的锁定指示装置是正交鉴相器,也被称为辅助鉴相器或相干振幅检测器[1]。为了减少虚警,通常采用较大的时常数,确保产品给出稳定可靠的解调器锁定指示,因而需要较长的时间才能形成解调器锁定指示。由于产品工作时序的需要,锁定指示的检测时间应控制在非常短的时间内。为实现锁定指示的快速检测,本文对经典的锁相接收机锁定指示原理进行研究。从现代数字信号处理的角度,提出了周期计数、数字滤波检测算法,进行了软硬件设计,通过试验验证。

1 经典锁定指示检测原理

采用异或门鉴相的锁定指示原理,如图1所示[2]。停止比相器把天线信号经混频中放后,作为输入;把多普勒信号经过90°相移后作为另一个输入。从图中可以看出,环路比相器输出信号经过环路滤波器后的输出电压为(1/2)sinθe,同时,停止比相器输出信号经过低通滤波器后,输出电压为(1/2)cosθe。在锁相解调器稳定锁定后,θe趋近于0,所以斯密特触发器的输入为(1/2)cosθe≈0.5,固态本振输入为 (1/2)sinθe≈0。当环路锁定时,停止比相器输出信号的主要频率成分为零频和倍频,经低通滤波器后,进入斯密特触发器的为直流电压,提供一个有用的停止信号,该信号通过解调器的逻辑管理,最终形成锁定指示。

图1 锁定指示检测原理框图与计算

低通滤波器输出的电压幅度和噪声起伏情况,反映了锁定指示的品质。低通滤波器又被称为平滑滤波器,其时常数是实际锁定指示的关键部分。如果没有平滑,锁定指示将会因为环路起伏噪声而上下跳变,发出错误的锁定和失锁指示。如果平滑过多,锁定指示因延迟太长而导致没有及时停止扫描造成的环路失锁。与之对应,从锁定到失锁的延迟时间太长,将会使环路在失锁噪声的推动下,环路将远离锁定的设计值,将大大降低环路的捕捉能力[3]。

2 锁定检测设计

经典的锁定指示检测采用模拟电路实现,产品性能稳定可靠,但在研制和生产过程中存在不足之处。首先,构成经典锁定指示检测的电阻、电容存在容差,锁定检测性能个性差异大;其次,温度、器件的老化也会导致电容、电阻的参数变化,锁定指示检测性能不可避免的受到环境和贮存的影响。

为弥补这些不足,本设计采用数字信号处理技术实现锁相解调器的锁定指示检测。依据图1的检测原理,可采用周期计数检测、数字滤波检测以及组合检测的方法。组合检测就是将周期计数检测和数字滤波检测结果进行逻辑组合所形成的检测方式。

2.1 周期计数检测

根据锁相环原理,环路锁定后,鉴相器的两个输入之间存在稳定的相位差,而没有频率差。根据这一原理,可以对鉴相器两个输入的每一个周期的相位差进行比较,当连续几次相位差的大小相互之间小于一定的值,即可认定环路已基本锁定[4]。

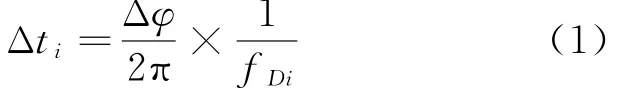

周期计数检测的工作过程示意图如图2所示。异或门鉴相器的两个输入分别为中放限幅中频输入和基准中频输入(频率为fDi),Δti(i=1~5)为这两个信号连续5个周期的时间滞后。

Δti与滞后相位的关系为

图2 周期计数检测示意图

设中频频率fDi=2.5 MHz、fs=200 MHz、相位误差Δφ=15°,那么Δti≈16.7 ns。则环路锁定的判定准则:Δt2-Δt1≤16.7 ns,Δt3-Δt2≤16.7 ns,Δt4-Δt3≤16.7 ns,Δt5-Δt4≤16.7 ns,Δt6-Δt5≤16.7 ns。通过6个周期的相位差的检测,共2 400 ns完成整个环路锁定的判定。由于检测时间短,将频繁出现环路锁定状态检测的虚警。

如果设计要求锁定指示形成时间为40μs,则可将6个周期增长到100个周期,40μs形成锁定指示信号,减小环路锁定检测的虚警。然而,100个周期数较大,在解调器灵敏度附近时,每个时间间隔都能满足检测条件的难度较大,降低了解调器灵敏度。有两种解决措施:一是可以采用滑窗算法,只要有连续100个周期满足要求,即完成锁定检测;二是采用比例检测门限,降低连续100个周期的要求,只要N(1≤N≤100)个周期满足锁定要求即送出锁定指示信号,具体取值通过试验进行确定。

2.2 数字滤波检测

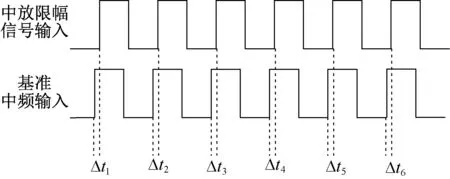

数字滤波检测的方法是针对模拟锁定指示的经典锁定检测技术(图1)进行数字化来完成。图1中,环路鉴相、停止鉴相、斯密特触发器、逻辑管理的数字化实现起来也较为简单。模拟锁定检测电路的平滑滤波器的电路图如图3所示。

图3 平滑滤波器电路图

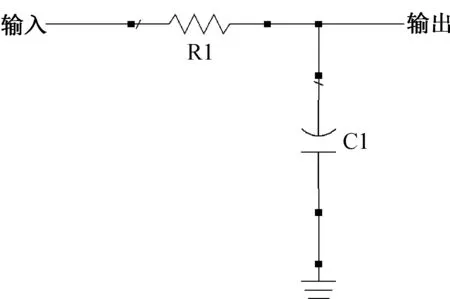

为保持锁定指示性能,不采用FIR滤波器设计,而是在模拟滤波器设计的基础上,进行传递函数的数字化滤波设计,即采用IIR滤波器设计。

具体设计思路:按照经典平滑滤波器的电路图计算模拟滤波器的传递函数Hm(s),再按s域到z域的转换,将Hm(s)转换成数字滤波器的H(z)。实现这一过程的方法较多,为了保证转换后的H(z)保持良好的滤波性能,必须满足两个条件。一是经典平滑滤波器转换成数字滤波器后,必须是因果稳定的。平滑滤波器Hm(s)的极点位于s平面左半平面上;转换后的数字滤波器的极点必须位于单位圆内。即转换关系必须使模拟滤波器传递函数s平面的左半平面影射数字域z平面的单位圆内部。二是数字滤波器的频响为保持Hm(s)的幅频、相频特性不变,转换过程必须使模拟传递函数s平面的虚轴线性映射到z平面的单位圆上。

脉冲响应不变法和双线性不变法是工程上常用的转换方法[5]。本文的平滑滤波器实现数字化,采用双线性变换法。

从图3的电路图建立平滑滤波器的传递函数为

式中:A0=1;A1=0;B0=1;B1=R1×c1。

采用双线形变换法对式(1)进行z变换后,数字域平滑滤波器传递函数为

式(2)与式(3)中:

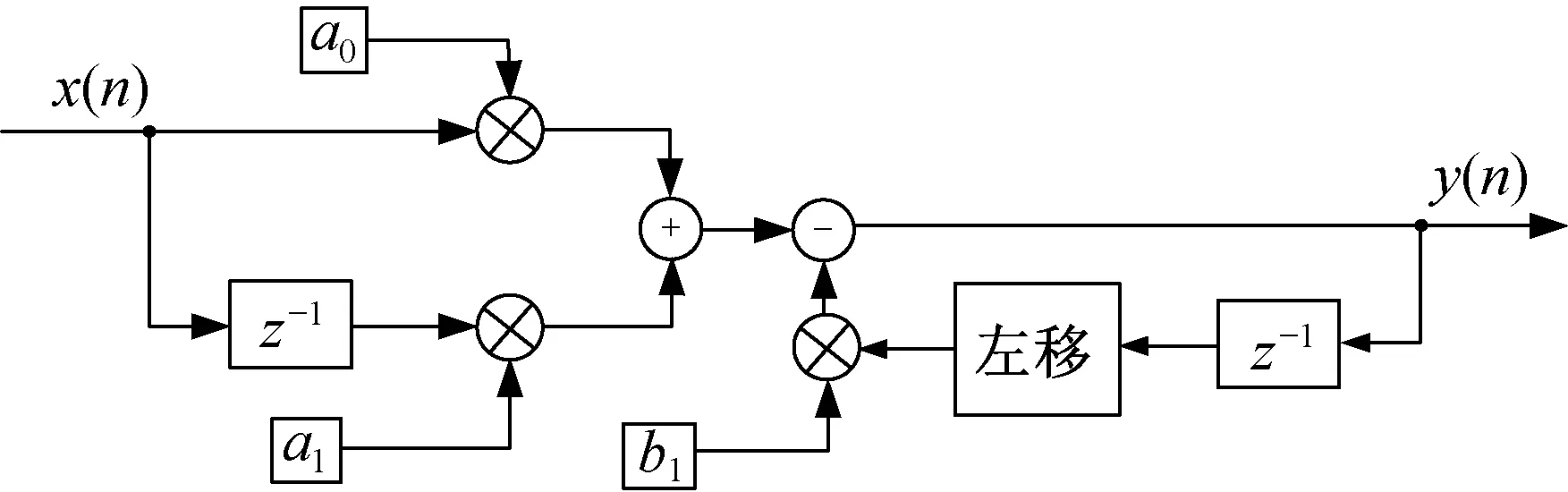

考虑到定点运算,需将滤波器的浮点系数定点化,可将所有系数进行同比放大,将舍位误差对滤波器性能的影响减小到可以忽略,该平滑滤波器的实现框图如图4所示。x(n)为数字信号输入,经过乘法器、延迟、加法器、减法器等最终形成输出y(n),完成信号数字滤波。

图4 平滑滤波器的实现框图

2.3 组合检测

周期计数检测是通过对每个周期相位差进行计数检测,当连续多个周期的计数值都满足锁定条件,即判定环路锁定。这种方法锁定检测时间短,判决条件过松容易发生锁定的虚警,判决条件过紧容易发生漏警。

数字滤波检测是通过与模拟锁定检测的数字化方式来实现,即采用数字正交鉴相器,再通过数字低通滤波器来实现锁定信号检测,这类锁定检测需要较长的时间,但稳定可靠。

通过对这两种检测结果进行逻辑组合,取各自的优点从而可以获取更好的检测性能。

3 硬件设计

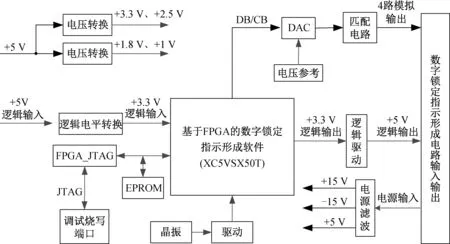

按照上述的分析,周期计数检测对工作时钟有较高要求,数字滤波检测则希望能够便利的使用数字信号处理基本的IP核。综合这些因素,本设计采用XILINX公司V5系列的XC5VSX50T芯片完成该锁定指示形成电路的设计,硬件原理框图如图5所示。

图5 硬件原理框图

图5 中,锁定指示形成电路的硬件设计以XC5VSX50T芯片为中心,按照数据手册配置相应的晶振、驱动、EPROM等辅助器件,完成锁定指示形成算法的实现[6]。为实现一定的通用性,设计8路逻辑输入、8路逻辑输出、4路模拟信号输出。为降低电源噪声,对输入+5 V电源进行电源滤波后,进行电压转换。

4 软件设计

采用原理图和硬件描述语言混合的输入方式,将周期计数检测、数字滤波检测的设计输入到ISE软件中。FPGA软件顶层设计采用原理图的方式进行设计;原理图中逻辑、控制管理等具体模块采用硬件描述语言(VHDL),周期计数、数字滤波检测软件顶层示意图分别如图6、7所示。

为验证设计模块的有效性,将图6、7所示的设计软件在XC5VSX50T芯片上进行综合编译和仿真,周期计数检测、数字滤波检测软件能够完成预期的功能。在时钟频率使用150 MHz时,稳定、周期计数指示使用的资源的总和小于30%。

图6 周期计数检测软件的顶层设计

图7 数字滤波检测软件的顶层设计

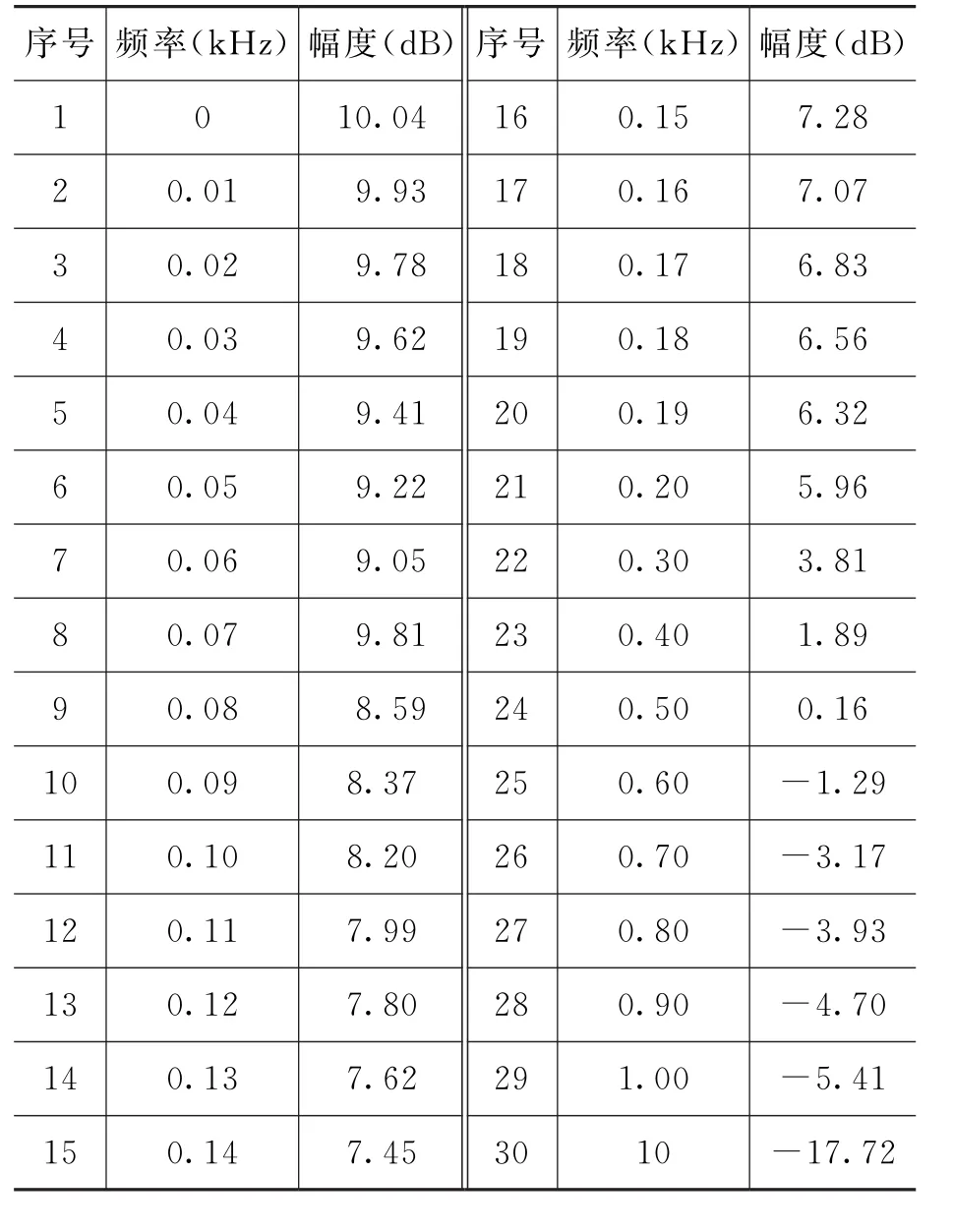

为验证数字滤波检测软件的有效性,建立平滑滤波器的激励信号源,在ISE软件中进行时序仿真。先后将输入激励信号的频率设置为0.01 k Hz、0.02 k Hz…0.19 k Hz、0.20 k Hz、0.30 k Hz…0.90 k Hz、1.00 k Hz,为便于分析,对仿真数据进行20×log10(dout)转换,结果如表1所示。从表中可以看出,平滑滤波器的3 dB带宽约在0.16 k Hz,符合设计要求。

表1 平滑滤波软件模块仿真结果

5 试验验证

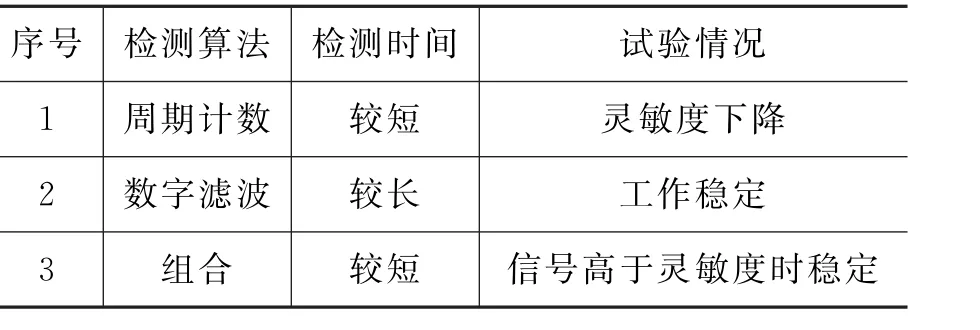

在完成软硬件设计后,接入锁相解调器系统,进行以下三个试验,探索锁定指示数字形成算法的性能。一是仅采用周期计数检测算法完成解调器闭合;二是仅采用数字滤波检测算法完成解调器闭合;三是同时采用周期计数检测算法和数字滤波检测算法,所形成的锁定指示进行逻辑“或”后送出,形成“组合锁定检测”指示信号。试验结果如表2所示。

从表2中看出,周期计数检测能够较快的形成锁定指示信号。但因为锁相解调器工作在灵敏度附近时,噪声较大,计数在满足条件和不满足条件之间来回切换,导致解调器灵敏度下降,可用于对灵敏度要求不高的场合。

表2 锁定检测试验结果

数字滤波检测需要较长的检测时间,但在锁相解调器的各种状态下均能够稳定工作。

经过逻辑“或”的组合锁定检测的检测时间时间较短,在高于灵敏度时,能够稳定工作。在低于灵敏度时,该方法会出现锁定指示跌落和反复虚警,需要在设计中加以考虑。

6 结束语

为实现锁相解调器锁定指示的快速检测,提出采用周期计数的方法,并结合数字滤波检测方法,实现了锁定指示的组合检测,达到了预期功能。试验表明:数字滤波检测算法与模拟锁定检测的性能基本保持一致,可用于对锁定检测时间要求不高的场合;组合锁定检测算法,同时满足快速和性能需求,但需要更多的资源。