基于DDS技术的脉冲涡流检测激励源研制

2019-09-10冯红东武新军

冯红东,武新军,李 威

(华中科技大学机械科学与工程学院,湖北武汉 430074)

0 引言

脉冲涡流检测技术是当前无损检测领域的研究热点之一,单次检测能够获取金属构件多层次信息,同时具有电磁非接触耦合的特点,是一种快速不停机大面积检测技术[1]。脉冲涡流检测激励源是脉冲涡流检测仪器的关键组成部分,用于产生激励信号,并经过功率放大后加载到传感器的激励线圈中,从而在被检试件中感应出涡流,涡流引起的磁场变化被接收线圈转换为电信号输出[2]。激励源性能直接关系到脉冲涡流检测信号质量,为提高检测灵敏度,需要高性能激励源。

直接数字频率合成(direct digital synthesizer,DDS)技术是一种从相位角度出发的全数字化频率合成技术,具有分辨率高、频率切换时间快、能输出任意波形等优点,在通信、测试、仪器仪表等领域得到了广泛应用[3]。本文在DDS原理的基础上,开发了一款以FPGA为核心的高性能脉冲涡流激励源,该激励源能够实现正负方波输出,幅值、频率、占空比和边沿时间连续可调。其中,频率范围为0.02~2 Hz,边沿时间范围为1~10 ms,占空比范围为1%~50%,能满足脉冲涡流检测对激励源的要求。

1 脉冲涡流检测激励源组成

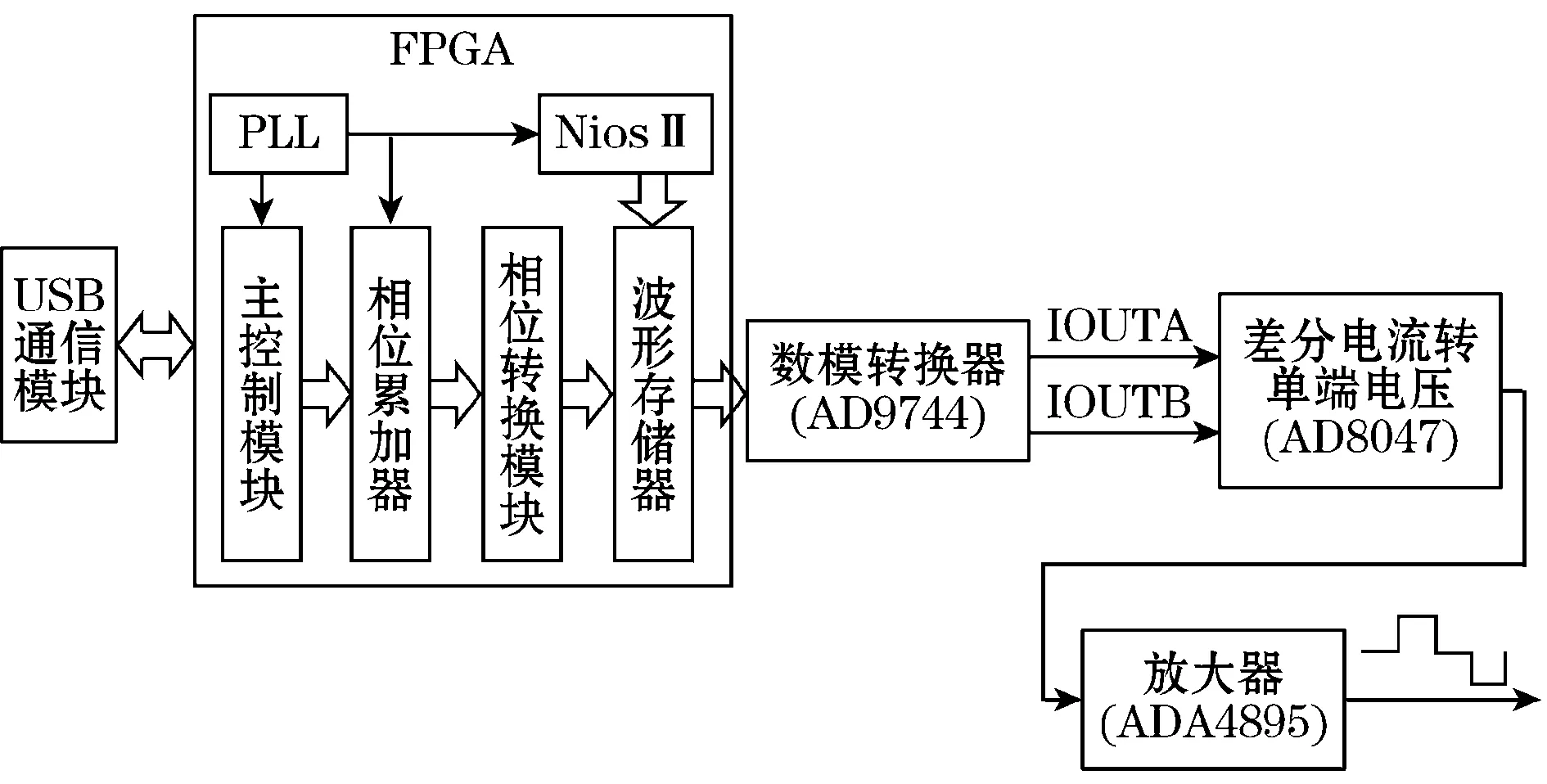

脉冲涡流检测激励源的原理框图如图1所示,其主要由USB、FPGA、DAC等模块组成。FPGA选用EP3C16Q240C8N器件,具有15 408个LEs,240个管脚,最多支持4个PLL,56个M9K RAM块,高达516 096 bits;数模转换器采用AD9744芯片,它是一款高性能、低功耗的CMOS数模转换器,14位分辨率,最大刷新率165 MSPS。由于AD9744是一款差分输出电流型DAC,需要利用差分转单端、电流转电压电路将其输出转化为单端电压信号。在此采用电压反馈运放AD8047和轨到轨运算放大器ADA4895来实现差分转单端、电流转电压电路。

图1 激励源硬件结构

2 脉冲涡流检测激励源实现

2.1 DDS基本原理

DDS是从相位角度出发的全数字结构频率合成技术,如图2所示,其主要由参考时钟、相位累加器、波形存储器、数模转换器和低通滤波器组成[4]。其中,fc为参考时钟;K为频率控制字;N为相位累加器的位数,其决定了输出信号的频率分辨率;A为波形储存器的地址位数,决定波形存储器的存储深度;D为波形存储器的数据位字长及DAC的位数,决定了幅值分辨率;fo为输出信号频率。

图2 DDS功能结构图

DDS开始工作之后,在fc作用下,相位累加器将频率控制字K与上一次累加结构进行累加保存,其输出为二进制相位码,用于对波形存储器的寻址,在溢出之前,相位累加器的输出为一个以K为步长的线性增长序列。相位累加器的输出相位码为波形存储器的地址输入,从而完成相位-幅度的转换。该幅度码经过DAC转换为阶梯波形,经过低通滤波后变成模拟波输出[5],输出信号频率如式(1)所示。

(1)

2.2 DDS逻辑开发

基于DDS技术原理,采用Verilog HDL语言实现相位累加器、相位转换模块和波形存储器的设计,借助SOPC技术生成波形存储器中正负方波的相位-幅值数据。

2.2.1 相位累加器设计

相位累加器是DDS系统中最关键的结构,由图2所示,其由N位的加法器和寄存器构成,加法器用于求和,寄存器用于保存求和结果。相位累加器在fc作用下,完成对K的累加,因而相位累加器输出可认为是一个以K为步长的线性增长序列,并且由于溢出会呈现周期性。相位累加器的输出为有效寻址,其有效地址个数也代表了一个激励波形周期内的数据点数。为了尽可能降低相位截断误差的影响,A的取值一般等于或稍大于DAC的位数加2[6]。本文选用的DAC为AD9744芯片,14位分辨率,在此将相位累加器的输出位宽设为17位,这样一个激励周期中相位累加器的输出结果中有131 072个有效寻址,正负方波波形中也有131 072个数据点。同时,本文设计的参考时钟fc=100 MHz,结合激励波形的频率范围为0.02~2 Hz。根据式(1),同时为了增大步进的最小分辨率,将相位累加器位数N设置为36,此时DDS能够输出的最小频率分辨率为0.001 5 Hz,能够满足系统设计的要求。相位累加器例化元件如图3所示。

图3 相位累加器例化元件

在图3(b)中,i_DDS_FRE_A用于设置频率控制字K,32位宽;i_clk是时钟信号,频率为100 MHz,当输出使能信号有效时即i_COMMAND置为高电平,在时钟i_clk上升沿,相位累加器进行累加,每次累加K,输出为截断之后的高17位二进制相位码,可以保证每个波形周期中的有效查找地址数量为217=131 072个,这样进行不停地累加和查表,输出波形具有连续性。其仿真结果如图4所示。

图4 相位累加器仿真图

2.2.2 波形存储器设计

波形存储器用于存储离散化的相位-幅值数据,实现相位-幅度转换。波形存储器的地址位数A决定了波形存储器的存储深度,字长等于DAC芯片的位数D。A的取值过大,会极大增加波形存储器的绝对容量,使设计成本提高,功耗增大;而A的取值过小,又会导致信号中杂散严重,频率稳定性较差。根据相位累加器的输出设计,A的取值设为17,这样波形存储器的存储容量大小为217×14=1 835 008 bits。而本文选用的FPGA为EP3C16Q240C8N,其含有56个M9K RAM块,大小为516 096 bits,不满足设计要求。有两种解决办法:增加外部大容量SRAM芯片,但需要改动硬件电路,增加系统功耗,结构复杂;利用压缩存储的方法,减小波形存储器的绝对容量,该方法实现时较灵活方便,需要根据波形不同来进行调整。综合考虑选用第2种方法,通过对正负方波激励信号的分析,采用压缩存储数据来等效增大波形存储器数据有效寻址位,正负方波信号示意图如图5所示。

图5 正负方波激励信号示意图

假设第1阶段包含n1个数据点,第2阶段包括n2个数据点,第3阶段包含n3个数据点,从而可以得出第4、6、8阶段也分别包含n2个数据点,第5阶段包含n1个数据点,第7阶段包含n3个数据点,数据点总数量为217=131 072个,离散化的波形可采用分段函数的形式来表达,如式(2)所示。进一步分析,第1、5阶段各有n1个数据点,各数据点相位不同,幅值相同,可用一个数据值来表示;在第2、4阶段,各数据点相位不同,幅值也不相同,但由于对称性,可采用其中一个阶段数据来表示;其他阶段数据亦是如此,这样存储相位-幅值数据可以显著节省波形存储器的绝对容量。基于此,本文采用数据压缩的方法来存储波形数据,具体存储顺序为,1个低电平点数据0,正方波上升沿全部n2个数据点,1个正的高电平点数据b,1个低电平点数据0,负方波下降沿全部数据点n2个,1个负的高电平点数据-b,总共为2×n2+4个数据,显著压缩了存储空间。

(2)

根据前述提出的激励信号波形参数可以计算出一个方波边沿对应的最大点数为217×10/500≈2 622,两个边沿点数为5 244,因此可将本文波形存储器的大小设为213=8 192≥5 248,满足设计要求。采用IP核设计方法将FPGA内部RAM块配置成ROM或RAM形式,文中配置成RAM形式,地址线13位,数据线14位,可以方便地更新其中的相位-幅值数据,生成参数可调的正负方波。波形存储器如图6所示。

图6 波形存储器

2.2.3 相位转换模块

根据波形存储器和相位累加器的结构设计,相位累加的输出并不能直接用于波形存储器的寻址,否则会造成相位截断,波形失真。为了确保一个周期内包含131 072个数据点的设计要求,需要在相位累加器和波形存储器之间加入一个相位转换模块,将相位累加器17位宽输出转换为13位宽。该转换过程中不能改变相位累加器寻址个数和寻址速度,相位转换模块如图7所示。

图7 相位转换模块

2.2.4 波形数据生成

根据对波形存储器的分析可知,波形存储器中存储激励波形的相位-幅值数据。为能够实现占空比、幅值、边沿时间等参数可调的需求,波形存储器中的数据必须能够得到及时更新。波形数据的来源通常有3种:上位机生成,然后通过USB写入DDS的波形存储器;设置若干个波形存储器存储不同的波形数据,然后切换来改变激励波形;在FPGA内部例化一个波形生成器,通过相应的参数生成波形数据。综合比较上述3种方案,本文选用第3种方案,借助SOPC技术可以方便地设计出正负方波的波形函数,完成波形数据的生成。本文设计的波形存储器的存储深度为8 192点,用来保存2个低电平点、2个高电平点、1个正方波的上升沿波形数据和1个负方波的下降沿波形数据。根据频率、占空比、幅值和边沿时间可以计算出边沿中含有的数据点个数及数据值,例如频率0.2 Hz,边沿时间10 ms,占空比50%,可以计算得到周期T=5 000 ms,边沿时间10 ms对应的点数131 072×10/5 000=262,进而可采用一次函数计算出方波边沿的相位-幅值数据。本文设计时采用上位机由波形参数计算出各阶段对应的点数传递给下位机,下位机根据点数和幅值就可以生成相应的波形数据,然后写入波形存储器。

2.3 上位机软件开发

利用VS2013开发环境在计算机编写上位机软件,通过USB2.0实现上位机和FPGA之间的数据传输,上位机界面包含了显示区和按钮区,用于可视化信息的选择与输入,如图8所示。操作者可以输入信号的频率、幅值、边沿时间、占空比等具体信息,上位机将这些信息转化为下位机可以识别的指令,通过USB2.0传输到FPGA中。

图8 上位机界面

3 激励源功能测试

脉冲涡流检测激励源具有幅值、频率、占空比、边沿时间连续可调的功能,设计中搭建了测试平台对功能进行了验证。利用HDO 4054数字示波器来观察波形各项参数,分别对激励波形的幅值、频率、占空比、边沿时间进行测试,观察输出波形质量。实际检测中常用激励频率为0.2 Hz,方波占空比50%,边沿时间1 ms,通过示波器观察到波形如图9所示,可以看出,方波波形正常,稳定,无明显毛刺。

图9 正负方波激励信号

图10 实验平台

为了进一步检测激励源实际性能,结合其他电路和仪器搭建实验平台,检测激励源在实际检测的性能。实验平台布置如图10所示,包括计算机、激励源、采集卡、前置滤波放大器、±12 V线性电源、数字示波器、BP4610双极性功率放大器、检测传感器、阶梯试板等。其中,试板的材料为16MnR,规格为33 mm×18.5 mm,壁厚分别为10 mm、8 mm。

将检测传感器分别放置于16MnR阶梯试板的8 mm、10 mm处,16MnR阶梯试板的检测信号如图11所示。从图中可以看出,16MnR阶梯试板的8 mm和10 mm壁厚能够清晰区分。因此,本文所研制的激励源能够生成具有一定频率和占空比的正负方波激励信号,符合设计目标,满足脉冲涡流检测需求。

图11 16MnR阶梯试板检测信号

4 结束语

本文利用DDS技术的优点和FPGA技术,开发了一种用于脉冲涡流检测的高性能激励源,能够产生高质量的正负方波激励信号,满足检测需求。工作时,上位机通过USB2.0完成对下位机的控制,包括波形参数设置、激励控制等,上位机界面友好,便于操作;下位机体积小,功耗低,性能稳定;上位机只需向下位机发送正确的控制命令,便可得到需要的正负方波激励信号。对激励源的功能测试表明,系统可以实现频率、占空比、幅值、边沿时间等参数的连续调节,系统输出的激励信号频率稳定性好、分辨率高、切换速度快,能够很好地满足脉冲涡流检测的需求。