基于IBIS模型的SDRAM信号完整性仿真

2019-09-10凌健鸿范攀锋

凌健鸿 范攀锋

摘 要:随着集成电路发展速度的不断提升,系统设计的复杂度也在不断增加,PCB(印制电路板)已不是简单的支撑电子元器件的平台,而变成了一个高性能的系统结构,因此信号完整性等因素在板级设计中已成为一个必须考虑的问题。传统的设计流程过分依赖开发者的技术和经验,存在各种不可控因素及资源消耗;在如今的板级设计中,采用电路板级仿真已经成为必然,借助前仿真和后仿真相结合的分析方法,可在发板前尽可能发现和解决设计过程中遇到的信号完整性及电磁兼容性问题,极大地提高系统设计的稳定性,减少因设计缺陷而多次改版的人力成本。本文结合前仿真及后仿真功能,以IBIS模型为基础,对SDRAM系统设计中的过冲、辐射及串扰进行针对性仿真探索,以仿真的输出结果指导产品设计,提高了系统稳定性。

关键词:信号完整性;仿真;过冲;串扰;EMC

中图分类号:TN402;TN401 文献标识码:A 文章编号:2096-4706(2019)15-0038-04

Simulation of SDRAM Signal Integrity Based on IBIS Model

LING Jianhong,FAN Panfeng

(ZLG Technology Corp.,Ltd.,Guangzhou 510660,China)

Abstract:With the continuous improvement of integrated circuit speed,the complexity of system design is also increasing. PCB(printed-circuit board) is no longer a simple platform to support electronic components,but a high-performance system structure. Therefore,signal integrity has become a must be considered in the board design. The traditional design process relies too much on the developer’s technology and experience,and there are various uncontrollable factors and resource consumption. In today’s board level design,it is necessary to adopt circuit board level simulation,with the help of the analysis method of combining pre-simulation with post-simulation,can be found as far as possible in front of the plate and solve encountered in the process of design of signal integrity and electromagnetic compatibility issues,greatly improved the stability of the system design,reduce the human cost of multiple revision due to design flaws. Combined with the pre-simulation and post-simulation functions,based on the IBIS model,this paper conducts targeted simulation exploration on the overshoot,radiation and crosstalk in the design of SDRAM system,and guides the product design from the output of simulation to improve the system stability.

Keywords:signal integrity;simulation;overshoot;crosstalk;EMC

0 引 言

當前新产品上市的周期越来越短,这样的大环境对产品的系统设计带来了更大的挑战。在做产品设计时有一个常见的现象,即设计人员一般都会记住某些经验法则,以此作为PCB的设计指导,但究其原因,却答复不出个所以然,如匹配电阻必须靠近驱动器端布局、传输线之间的距离必须保证3倍线宽才能保证信号之间的串扰不易过大问题等,针对常见的3W规则,这些法则有时候并不适用于所有的设计,特别是在一些高密度板的设计中,要满足3倍线宽的间距似乎很难做到。为此,设计人员通过增加板层来完成设计,诚然这种做法达到了3W规则的要求,但却因此提高了产品成本。如果前期能够通过仿真对串扰大小进行评估,就能确定在小于3倍线宽的情况下,信号布局走线是否在合理范围内;另外,在已成产品上发现问题是一件困难的事情,即使找到问题,在一个已成形的PCB板上实施整改同样会花费大量时间,那么在设计过程中提前发现并消除这些问题就显得很有必要了,因此,仿真技术的加入对于系统稳定设计的重要性不言而喻。

1 信号完整性仿真

1.1 LineSim及IBIS概述

LineSim为前仿真功能模块,主要功能是在PCB布局布线前对原理图中的关键信号(如时钟信号、复位信号、模拟信号)进行针对性的仿真分析,以考察关键信号在设定的叠层结构中以及特定布局走线参数条件下的传输质量,以确定系统设计是否会存在常见的如过冲、串扰、辐射等隐患。

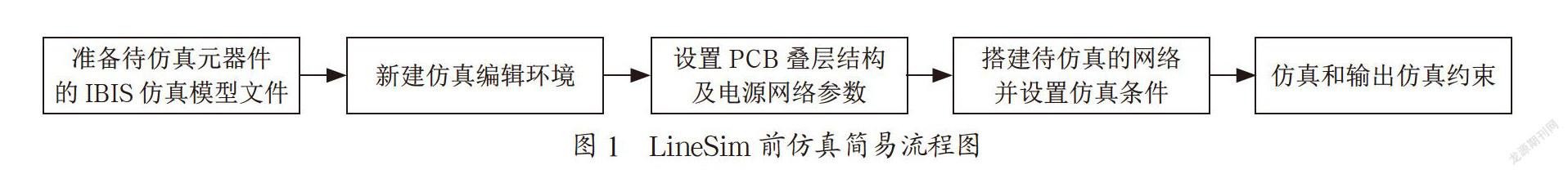

通过前仿真的波形对比分析,设计者可提前对原理图设计的可靠性进行评估。在进行实际的前仿真前,都需设置一些仿真条件,作为仿真参数的一部分,前提条件的设置是否正确,将直接影响结果和分析结论,前仿真的整个流程图大致可总结如图1所示,该前仿真的流程图对于后仿真设置是同样适用的。

IBIS是Input/Output Buffer Information Specification的缩写,是一种行为级模型,描述的是芯片输入和输出接口的行为特性,它基于I/V曲线,在不泄露芯片电路接口的情况下可对I/O Buffer快速建模。可通过IBIS模型仿真获取互通网络的电气参数,如信号质量(过冲、串扰、辐射)等;通常IBIS模型可从元器件官方网站获取,以下仿真需要下载的元器件IBIS模型名称分别为“rt1052_196bga.ibs”和“IS42S16160J-7TLI.ibs”。

1.2 设置仿真叠层参数

为得到准确的、和实际相符的设计参数,在进行前仿真之前,有必要设置准确的板层结构参数,这一点非常关键。在LineSim工具栏中选择“Setup→Options→Edit”,可对叠层参数进行相应的设置。图2为以下仿真及实际发板所需的叠层参数,PCB叠层采用4层板设计(TOP层和BOTTOM层为信号层,第二层为GND层,第三层为电源层),完成板厚为1.6mm,线宽设置为6.5mil,PP的介电常数为4.25。

1.3 搭建仿真信號拓扑

在元件库栏中选择需要的器件、传输线和电阻的图标,放置在LineSim原理图编辑区中,然后通过拖放的方式,连接各个元器件的热点。为更好地将过冲仿真拓扑及后续辐射仿真波形数据形成对比,这里将待仿真的信号拓扑设计成四种拓扑组合,如图3所示,并依次编号为“[1]”“[2]”“[3]”“[4]”号。

“[1]”号拓扑结构为驱动器通过单端50Ω阻抗传输线直连到接收器;“[2]”号拓扑在靠近驱动器端串入33Ω阻值的电阻;“[3]”号将33Ω电阻放置在接收器处;“[4]”号则在靠近驱动器端预留了一个0Ω电阻工位,与“[1]”号的区别是两者Rdrv配置不一样,Rdrv为驱动器的输出内阻。

1.4 过冲仿真及分析

仿真拓扑搭建完成后,下一步需要设置仿真条件。在LineSim原理图编辑窗口中,通过双击进入器件参数属性界面,点击界面中的“Select”按钮,为相应的器件选择合适的仿真模型,接着按照此步骤对所有器件逐一设置其仿真模型。但需要注意的是,在设置中需选择U1、U3、U5的驱动模式为Rdrv=111,U7为Rdrv=011,然后将器件的“Buffer Settings”都指定为Output模式;将U2、U4、U6、U8器件的“Buffer Settings”指定为Input模式。

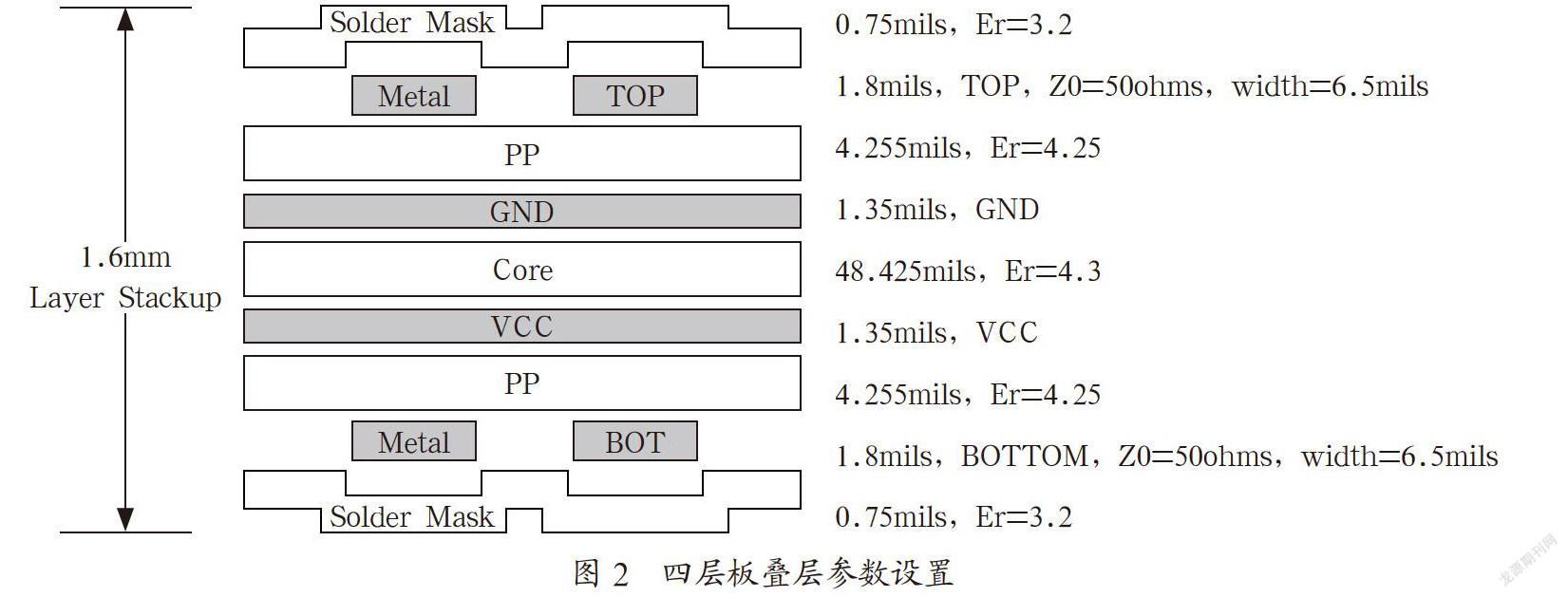

在LineSim菜单栏中选择“Simulate SI→Run Interactive Simulation and Show Waveforms”,进入仿真数字示波器交互界面,该界面提供两种仿真激励设置,一种是标准的具有一定占空比的周期脉冲信号,对应Global选项;另外一种是将激励源设置为常用的比特流激励,对应Per-net/pin选项,此处选择Global选项,根据所需仿真的SDRAM型号的将频率设置为143MHz,占空比设置为50%,将水平延迟设置为100ns,水平比例设置为5ns/div,点击开始仿真按钮“Start Simulation”输出仿真结果,如图4所示为接收器接收到的波形,是四个波形的叠加。

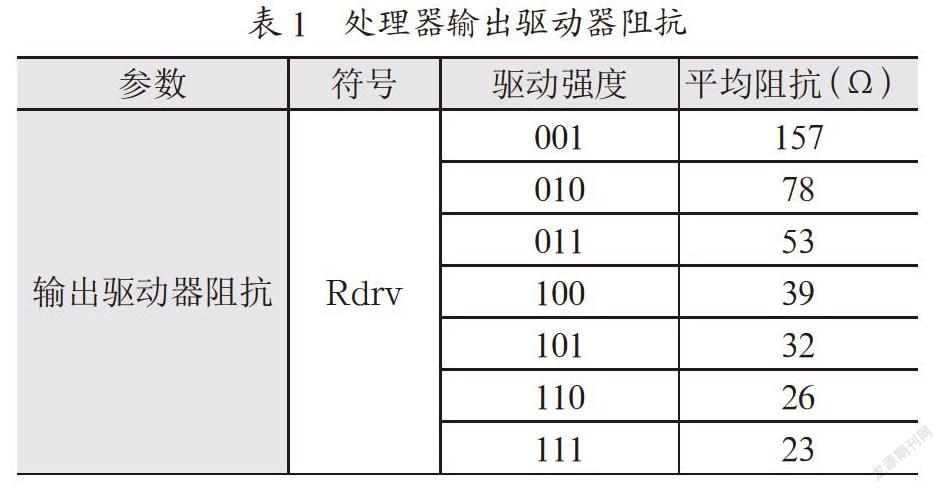

根据“[1]”和“[2]”输出波形对比验证了驱动器输出阻抗与传输线不匹配会引起信号反射,从而引起过冲、下冲问题,但串接电阻可消除过冲问题;根据“[2]”和“[3]”输出波形对比验证了匹配电阻应靠近驱动器布局,因为此时驱动器输出阻抗加上匹配电阻等于传输线阻抗,信号反射的情况会小很多,但将匹配电阻靠近接收端布局,由于驱动器还是没有实现阻抗匹配,因此对消除过冲、下冲的效果几乎没有;根据“[1]”和“[4]”波形对比可知,一些处理器支持软件配置解决过冲问题,只需将驱动器的输出阻抗配置为传输线阻抗即可。如表1所示,只要按照“[4]”的拓扑结构,将输出驱动器驱动强度软件配置为Rdrv=011,即可将过冲问题消除。

表1 处理器输出驱动器阻抗

1.5 EMC仿真及分析

电磁兼容(Electro Magnetic Compatibility,EMC)意指设备所产生的电磁能量既不对其他设备产生干扰,也不受其他设备干扰。早期EMC问题的处理都是在产品设计周期的最后阶段进行,一般都是用成品设备在专业的实验室进行测试,显然这样做是非常不经济的。因为产品已经做成,任何修改均会造成经济上的损失,而在产品设计的起始阶段采用EMC仿真技术可以大大减少这种损失。

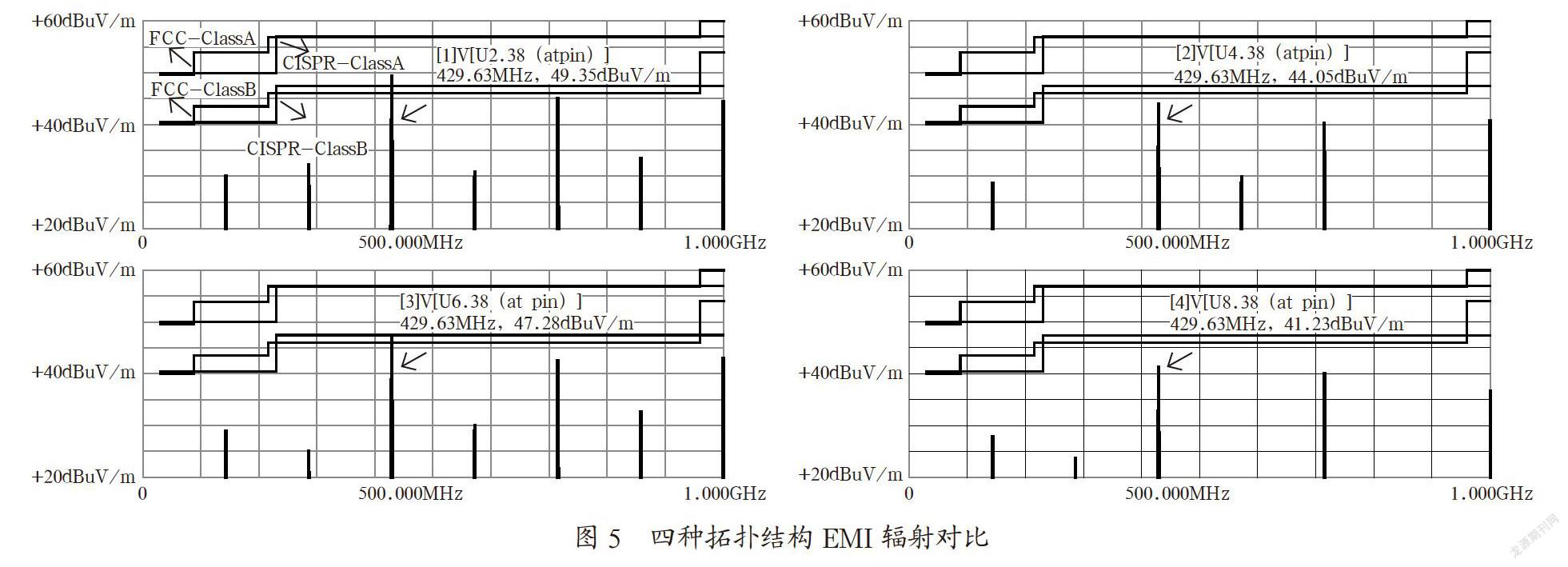

以下EMC仿真继续以图3的四个拓扑分别对时钟信号进行分析,测试辐射的距离可以在“Simulate SI→Attach Spectrum Analyzer Probe→Set Spectrum Analyzer Probing→Distance from antenna to PCB”对话栏中进行设置,本文选择默认的距离,即“3meters”,其余选项按默认设置即可。接着单击工具栏的“Simulate SI→Run Interactive EMC Simulation”图标,打开频谱分析仪“Spectrum Analyzer”,在对话框的“Stimulus”栏中,将激励源频率设置为143MHz,占空比设置为50%,选择“IC modeling”为“Fast-Strong”,其他选项按照默认设置即可,单击“Start Simulation”按钮,即可分别对四个拓扑运行EMC仿真,仿真结果如图5所示。图中的垂直线条代表了时钟信号仿真时的实际辐射大小,FCC代表美国规定的容限,CISPR代表欧洲国家规定的容限,Class A为工业等级,Class B 为民用等级,以等级严格程度来讲,B>A,同样产品在测试EMI中的辐射测试来讲,B类要求产品的辐射限值不能超过40dbm 而A类要求不能超过50dbm。注意“[1]”号及“[3]”号线条在429.63MHz频段附近,频谱辐射是超标的,这是因为其信号过冲,往往会导致辐射也超标,“[2]”号及“[4]”号通过硬件措施和软件措施消除了辐射问题。

1.6 串扰仿真及分析

串扰是信号完整性中的主要问题之一,在电路板尺寸变小、成本要求提高、电路板层数变少的情况下,布线密度越来越大,串扰的问题也越来越严重,因此,预先防止和减小串扰对产品设计就显得非常关键。后仿真BoardSim工具能够很好地对选择的信号进行串扰仿真,并输出具体串扰的幅值,可以很方便地评估关键信号的走线间距或者PCB叠层是否符合设计要求,对设计者而言非常关键。

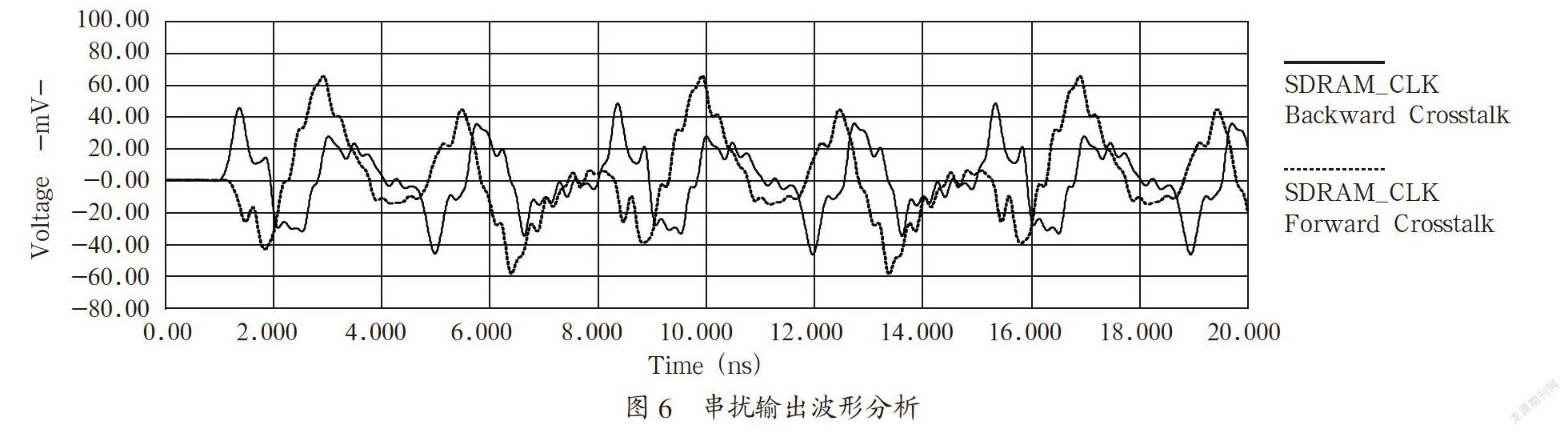

在进行串扰仿真之前,需先设定串扰的门限电压,可以点击菜单栏“Setup→Coupling Thresholds”选项,设置合理的串扰门限值,一般建议将串扰门限设置在器件逻辑高电平的5%左右;下一步打开准备好的待仿真“HPY”格式文件,按照图2设置好叠层参数及编辑验证电源网络,接着即可对待仿真元件添加仿真模型,仿真模型添加完成之后,单击工具栏“Select→Net by Name for SI Analysis”,打开“Select Net by Name”窗口,选择要仿真的时钟信号,设置网络名称为“SDRAM_CLK”,选择完成后点击“OK”按钮,此时待仿真网络被选中,然后单击工具栏“Setup→Enable Trace Coupling”,使其能与走线耦合功能,则在选定的被攻击网络周围会出现一些攻击网络,在编辑区中待仿真的被攻擊网络用实线表示,其周围的攻击网络用虚线表示;最后点击“Simulate SI→Run InteractiveSimulation and Show Waveforms”运行串扰仿真,结果如图6所示,可见,所选信号与相邻走线在3W规则下的串扰是符合要求的,峰峰值在120mV左右。

2 结 论

本文的仿真波形均为在实际SDRAM内存系统设计过程中,借助前仿真工具LineSim及后仿真工具BoardSim对关键信号进行信号完整性仿真得出的波形。

在系统设计中,通过靠近驱动器串接电阻可将过冲、问题很好地解决,但同时也要核对处理器是否支持软件配置驱动器的输出阻抗,如果支持,那么外部串接电阻可以省略不计,这对于高密度板级设计而言,可以省下更多的布线面积;此外,通过对EMC的仿真,使得在设计前期就可以评估板级设计是否存在缺陷,极大减少了系统的设计成本;后仿真BoardSim对信号串扰的仿真波形,非常直观地量化了PCB设计中的疑点,让模糊不定的3W走线规则得以进行直观的对比,特别是对于高密度板级设计,走线间距往往做不到3倍的走线宽度,通过仿真,可以对小于3倍间距的情况进行量化分析,极大提高了工作效率。在后续的研究中,还应加大对板级系统信号完整性仿真技术和应用研究的力度,争取在高速度高性能产品系统设计方面取得突破,进一步促进物联网的快速发展。

参考文献:

[1] 邵鹏.信号/电源完整性仿真分析与实践 [M].北京:电子工业出版社,2013.

[2] 王剑宇,苏颖.高速电路设计实战 [M].北京:电子工业出版社,2016.

[3] 毛忠宇,杨晶晶,刘志瑞,等.信号、电源完整性仿真设计与高速产品应用实例 [M].北京:电子工业出版社,2018.

作者简介:凌健鸿(1990.05-),男,汉族,广西玉林人,嵌入式硬件工程师,毕业于闽江学院,学士学位,研究方向:电子信息科学与技术、嵌入式系统设计。