基于TMS320C6455的SRIO互连技术应用*

2019-09-04王才能刘慧红吴晋成

王才能,刘慧红,吴晋成

(中国电子科技集团公司第三十研究所,四川 成都 610041)

0 引 言

随着时代的发展,信息技术和设备已经深入地影响到人类社会的各方面。同时,社会的新需求,反过来要求信息系统或设备的功能越来越多,继而规模也越来越大。把多种功能集成到一个系统或设备中,已成为电子信息设备发展的一个趋势。设备中不同的功能由独立的硬件板卡实现,板卡之间需要交互大量数据。现在一般采用总线技术互连多个板卡。

现有的并行总线,需要的物理线路多,印制板布线要求高,传输距离和传输速率都有限。通用的串行总线有集成电路总线(Inter-Integrated Circuit,I2C)、串行外设接口(Serial Peripheral Interface,SPI)等,在实际传输中有一个主方,多个从方。传输过程完全由主方控制,从方之间不能直接进行数据交互,不够灵活。

Rapid IO是一种新型交换式总线,它有着轻量型的传输协议;总线框架层次清晰,对软件的制约要少;适用于设备内部芯片与芯片之间,板卡与板卡之间的互连。

1 Rapid IO总线技术

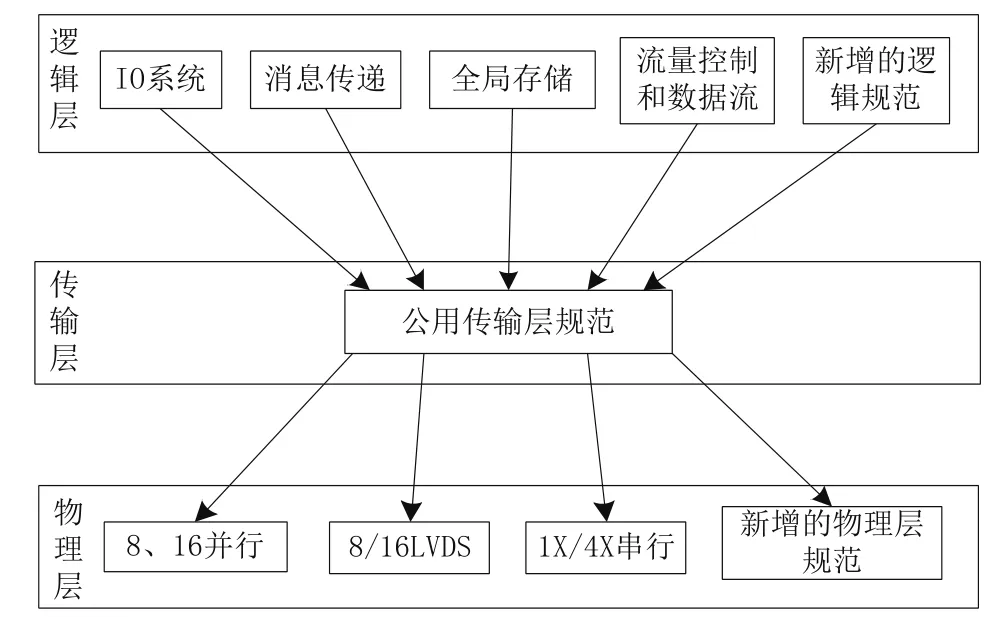

Rapid IO的框架共有3层(见图1),即:物理层、传输层和逻辑层。物理层规定电气特性、链路控制、流量控制、低级错误管理等;传输层规定包交换、路由和寻址机制等;逻辑层规定总体协议和包格式[1]。

图1 Rapid IO协议框架

(1)物理层

物理层定义了串行和并行两种方式。其中1x/4x串行Rapid IO仅4或16个信号线,采用差分交流耦合信号,具有抗干扰强、速率高、传输距离较远等优点,是现在应用最多的物理层传输方式。串行Rapid IO(Serial Rapid IO,SRIO)的物理层使用了可靠传输协议。

(2)传输层

Rapid IO传输层定义了数据包交换的路由和寻址机制。采用单一的公用传输层规范来会聚不同的逻辑层和物理层,即使有新的逻辑层、物理层规范出现,也可以用这个单一的传输层。

Rapid IO网络中主要由两种器件,即终端器件和交换器件。Rapid IO的路由和交换是通过每个终端设备的ID号来实现的。

(3)逻辑层

逻辑层定义了业务协议和相应的包格式。RapidIO支持的逻辑层业务主要是:直接IO/DMA(Direct IO/Direct Memory Access)和消息传递(Message Passing)。直接IO/DMA模式是最简单实用的传输方式。在这种模式下,发送端知道接收端的存储器地址,可以直接读写接收端的存储器。直接IO/DMA在接收端的功能往往完全由硬件实现,所以接收端的器件不会有任何软件负担。

(4)Rapid IO的基本传输流程

Rapid IO数据传输基于请求和响应数据包。在图2中,发送器件通过产生一个请求包开始一次传输。该请求包被传送到交换机构。交换机构发出控制符号确认收到了该请求包,随后交换机构将该包转发至目标器件,这就完成了此次传输中的请求阶段。目标器件完成要求的操作后产生响应事务包,通过交换机构将该响应事务包传送回发送器件,以完成此次传输[2]。

图2 Rapid IO传输流程

2 TMS320C6455的SRIO接口模块

TMS320C6455是德州仪器(Texas Instruments,TI)公司推出的一款高性能定点型数字信号处理器(简称DSP6455)。该处理器运行主频最高为1.2 GHz,最大峰值计算速度达到9600MIPS;每个周期能够执行8个32位的指令。DSP6455的SRIO模块,具有4个全双工的端口,可配置为4个1X通信端口,也可配置为1个4X通信端口;每个通信端口波特率可配置为 1.25 Gb/s、2.5 Gb/s、3.125 Gb/s[3]。

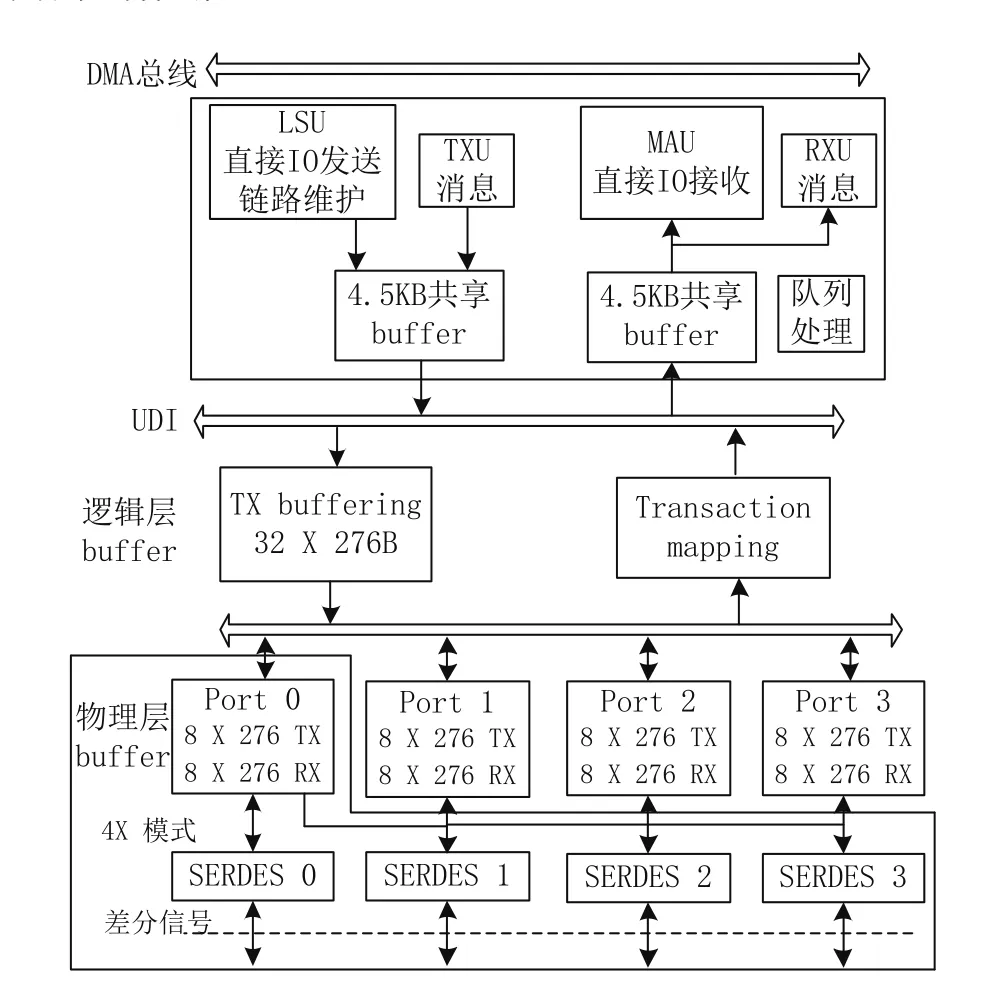

图3展示组成DSP6455 SRIO的功能模块。该图描述DSP6455如何实现SRIO三层协议。加载/存储单元(Load Store Unit,LSU)控制直接IO数据包的发送和维护包的发送;存储器访问单元(Memory Access Unite,MAU)控制直接IO数据包的接收。发送单元(Transmit(tx) Unite,TXU)和接收单元(Receive(rx) Unite,RXU)负责消息数据包的发送和接收。LSU、存储器访问单元(Memory Access Unit,MAU)、TXU和RXU都使用直接存储器访问(Direct Memory Access,DMA)通道与DSP的内存交互数据,使用缓存器和接收/发送端口与外部设备交互数据。串行/解串器(Serializer/deserializer,SERDES)在发送数据时完成并行数据转换为串行数据,在接收数据时完成串行数据转换为并行数据。

图3 DSP6455 SRIO功能框图

SRIO模块在DSP处理器中是一个数据传输的主动方,不需要产生中断给DSP处理器的CPU或借助EDMA,就能够将数据传送到DSP处理器的内存。

DSP6455 SRIO的SERDES(串行/解串器)由差分接收器(Rx)、差分发送器(Tx)、串转并行器、并转串行器、时钟恢复器、8b/10b解码器、8b/10b编码器、8位FIFO、收发通道对齐模块、循环冗余校验(Cyclic Redundancy Check,CRC)错误校验器、CRC产生器和锁相环(Phase Locked Loop,PLL)等组成。SRIO模块的PLL需要外部参考时钟源,通常要求该时钟源是低电压差分晶振。PLL将外部时钟倍频后送给时钟恢复器使用。外部晶振的频率根据SRIO的传输速率决定[4]。

3 系统及硬件设计

SRIO总线的线路少,硬件布线方便;传输速率快,能够适用于各种高速互联需求;协议框架相对简单,易于进行软件开发;SRIO支持两个设备直连,点对点地交互数据;如果使用交换芯片,可以实现多个设备间的任一互联,数据互联通道的拓扑结构灵活。本文设计了一个多任务处理平台,采用DSP6455作为主处理器,同时使用DSP 6455的SRIO接口完成板卡之间的互联。

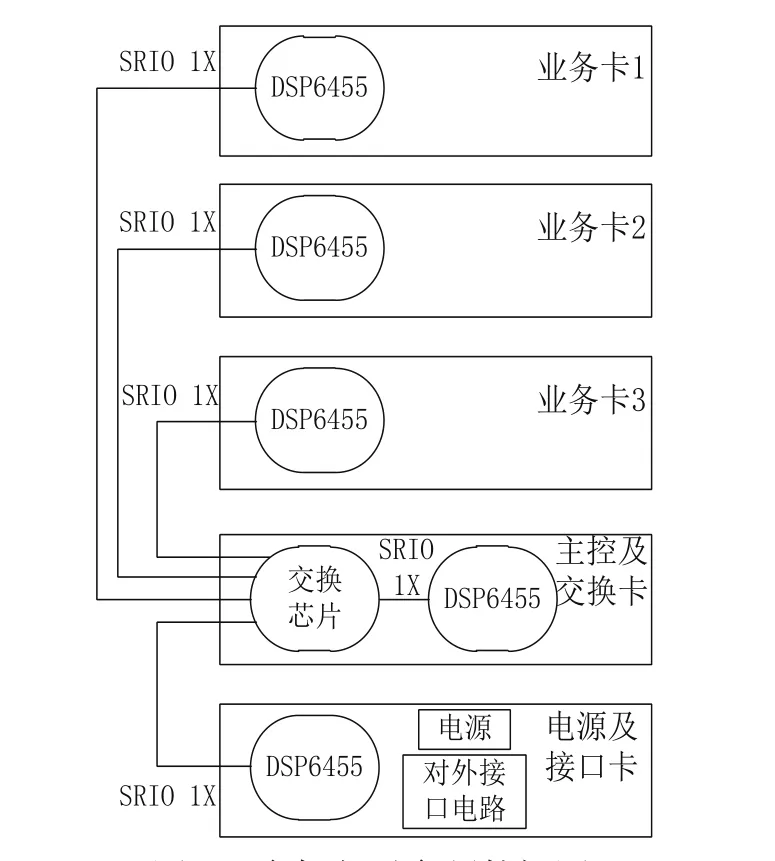

图4为多任务平台的硬件框图。业务卡1、2、3实现不同的数据业务处理功能,采用DSP6455作为各个业务卡的主处理器。各个业务卡和主控卡通过SRIO交互数据。SRIO交换芯片布置在主控卡。各个板卡的SRIO都接入交换芯片,通过交换芯片的路由控制功能,实现各板卡之间的数据交互。

图4 多任务平台硬件框图

主控及交换卡实现整个平台控制功能和SRIO路由交换功能。电源及接口卡完成220 V交流电到直流电12 V、5 V、-12 V的变换,通过对外接口电路和外部设备连接,完成平台的对外数据交互功能。平台的SRIO总线采用1X模式,速率设为1.25 Gbit/s。

该平台具有很强通用性,能够适应多种不同的需求,实现相应的功能。交换芯片采用Integrated Device Technology(IDT)公司的80HCPS1432系列芯片,该芯片可同时连接8个4X模式通道或14个1X模式通道。由于交换芯片有多个SRIO端口,所以可以连接多个业务板卡,具有很强扩展能力。业务卡的数量不限于图中描述的3个,可以根据需求进行增减。

需要注意的是SRIO的SERDES(串行/解串器)需要单独提供差分晶振时钟,以便进行串行数据的收发。由于本平台的SRIO速率为1.25 Gbit/s,所以选择的差分晶振的时钟频率为125 MHz。

4 软件设计

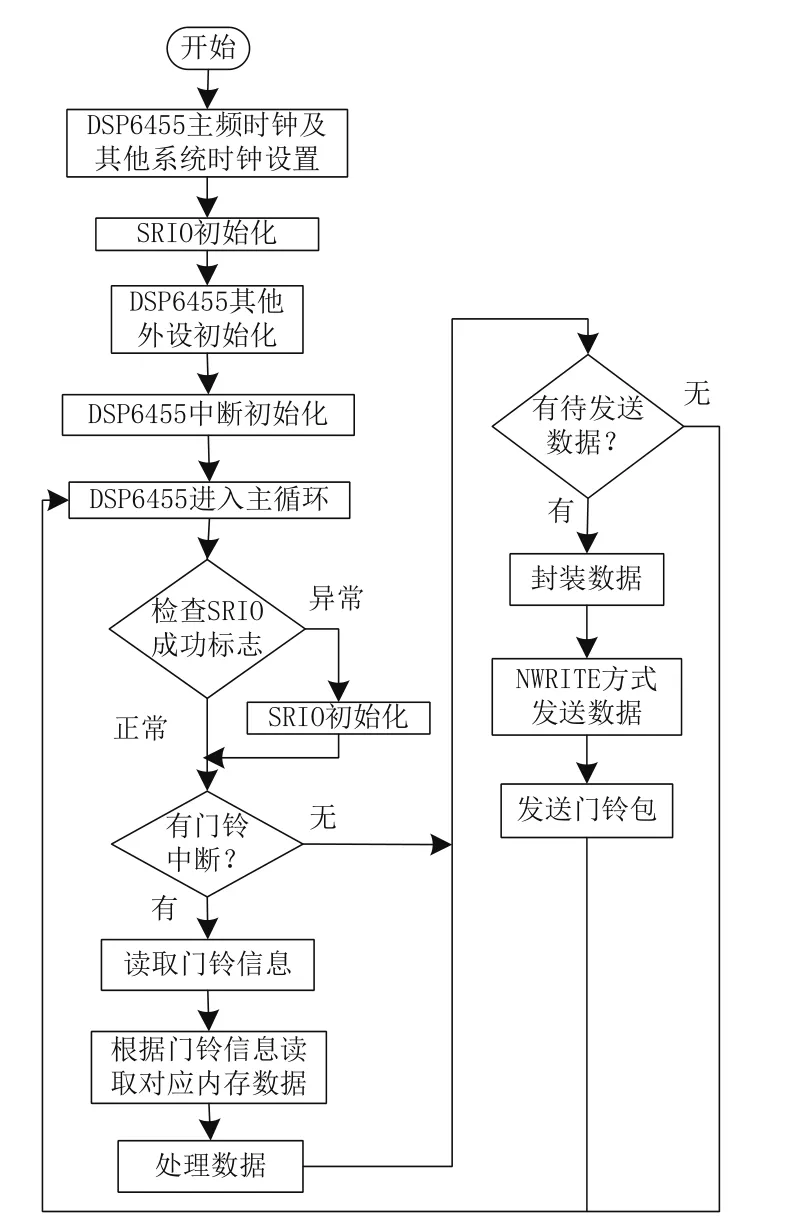

DSP6455上电后,首先进行芯片配置,主要是设置主时钟频率、和其他系统时钟。接着进行SRIO的初始化。然后进行其他外设的初始化,如外部存储器接口A(External Memory Interface A,EMIFA)、通用输入输出接口(General-purpose input/output,GPIO)、多通道缓存串口(MultiChannel Buffered Serial Port,MCBSP)、以太网口等。中断初始化完成后进入主循环,处理业务数据。SRIO对平台至关重要。在某些情况下,SRIO可能初始化失败。为此在主循环中设计了一套SRIO重新初始化机制。程序在主循环中定期检查SRIO成功标志是否正常,当SRIO成功标志异常时,程序再次进入SRIO初始化过程,重新配置SRIO的寄存器。DSP6455的软件流程图如图5所示。

图5 DSP6455软件流程图

下面重点描述SRIO相关程序设计,平台中采用SRIO的1X模式,具体使用DSP6455的SRIO通道0。

(1)SRIO初始化

1)设置寄存器PERCFG0的SRIOCTL(bit31:bit30)字段,使能整个DSP6455的SRIO。

2)将错误状态寄存器SP0_ERR_STAT设置为0。

3)打开SRIO的全局使能寄存器GBL_EN,打 开 寄 存 器 BLK0_EN、BLK5_EN、BLK1_EN、BLK2_EN相应使能字段,分别使能SRIO的寄存器MMR、打开通道0、使能LSU单元和MAU单元。

4)对SRIO外设设置寄存器PER_SET_CNTL进行设置,该寄存器主要规定了SRIO与DSP内核交互数据的要点。

5)设置SERDES的配置寄存器SERDES_CFG0_CNTL,DSP6455有4个SERDES配置寄存器,但其他3个配置寄存器没有使用,暂无意义,程序上赋值为全0。把SERDES_CFG0_CNTL的ENPLL字段置为1,使能SERDES的PLL。MPY字段代表PLL的倍频系数,本文平台设为10X。本文为SRIO选用125 MHz的差分晶振。所以PLL输出的用于串行收发的时钟为1.25 GHz。

6)设置通道0的SERDES接收、发送配置寄存 器 SERDES_CFGRX0_CNTL、SERDES_CFGTX0_CNTL。上述两个寄存器字段多,关系到SERDES能否正常工作和数据传输的可靠性,须正确设置。本文平台将SERDES_CFGRX0_CNTL赋值为0x81121,将SERDES_CFGTX0_CNTL赋值为0x00010a21,采用半速率模式,SRIO的传输速率为1.25 Gbit/s。

7)设置设备ID寄存器DEVICEID_REG1、DEVICEID_REG2。寄存器DEVICEID_REG1需要与寄存器BASE_ID赋值一致。寄存器DEVICEID_REG1决定了发送数据包中的源ID。寄存器DEVICEID_REG2用于接收时比对接收数据包的目的ID,判断是否接收处理该数据包。

8)完成上述设置后,要把寄存器PER_SET_CNTL的字段BOOT_COMPLETE设为1,以便SRIO物理层启动状态机,按照上述配置进行初始化。

9)在寄存器SP_IP_MODE中设置SRIO为1X模式。

10)寄存器SP_LT_CTL、SP_RT_CTL最好赋值为0xFFFFFF00,以便给链路维护、数据包传输提供足够的超时时间,增强SRIO传输的可靠性。

11)寄存器SP0_CTL是端口控制寄存器。在该寄存器中,将字段PORT_DISABLE置为0,将字段OUTPUT_PORT_ENABLE、INPUT_PORT_ENABLE置为1,使能该端口接收发送数据包;其他可写的bit位置为0,打开相应功能,让端口进行数据包CRC校验,重传错误包,处理任何数据包等。

12)完成上述设置后,要再次把寄存器PER_SET_CNTL的字段BOOT_COMPLETE设为1,以便再次让SRIO物理层启动状态机,按照上述配置进行初始化。

13)程序等待约10 ms,判断寄存器SP0_ERR_STAT的字段PORT_OK(即bit位1)是否为1,为1则SRIO初始化成功。SRIO初始化成功后,才可以正常使用。

14)最后要将寄存器PCR的字段PEREN置为1,使能数据流控功能。需要注意的是:当DSP从复位或设置状态进入正常工作时,该bit位应是最后使能的bit位。

(2)直接IO方式的操作

直接IO方式时,SRIO可以直接访问CPU的内存。发送时,SRIO从内存读取数据,封装成数据包,通过端口发送出去。接收时,SRIO将接收到的数据包净荷存入指定的内存空间,CPU直接使用数据净荷。所以接收过程一般由硬件完成,不需要程序参与。本文采用NWRITE方式实现直接IO的发送。NWRITE方式一包最大为256 bytes,且不要求接收端回复响应包。

DSP6455提 供 寄 存 器 LSUn_REG0、LSUn_REG1、LSUn_REG2、LSUn_REG3、LSUn_REG4、LSUn_REG5、LSUn_REG6(n=1、2、3、4) 来 完成直接IO的发送。LSUn_REG0为扩展寻址方式时目的地址(接收端内存地址)的高32位;LSUn_REG1为目的地址,或者扩展寻址方式时目的地址的低32位;LSUn_REG2为源地址(发送端内存地址),LSUn_REG3为数据净荷的长度(以字节为单位);LSUn_REG4寄存器规定了发送端ID、目的端ID、数据包优先级等。LSUn_REG5寄存器规定门铃包的信息、数据包的类型(其中0x54表示NWRITE包,0xA0表示门铃包)。LSUn_REG6寄存器的COMPLETION_CODE字段表示SRIO数据包的传输状态,BSY字段表示LSU的上述7个寄存器是否可用。

在写完寄存器LSUn_REG0到LSUn_REG5后,SRIO开始进行封包并发送,需要等待一段时间SRIO才能完成发送。程序定时查询寄存器LSU1_REG6的bit位0,如果为0,表示LSU的寄存器已处于空闲可用状态,本次发送成功,可以再次发送。

NWRITE方式的程序代码如下:

(3)门铃中断

发送方采用直接IO方式将数据直接写入接收方的内存中。该过程不需要接收方的CPU参与,CPU也就不知道是否接收到数据。此时需要采用中断方式通知接收方CPU去读取内存接收到的数据。发送方在采用直接IO方式完成数据传输后,紧接着发送一包门铃数据包,接收方收到门铃数据包后,会产生中断,通知CPU及时处理接收到的数据。

SRIO提供4个门铃,每个门铃包含16个bit的信息,其中每个bit可以表示一个单独的中断请求。所以SRIO有64个门铃中断请求。DSP6455中断机制有别与TI公司之前的DSP。在DSP6455中,各种外设可以产生很多中断请求,由中断请求映射到中断事件,中断事件再映射到CPU的中断。其中用户可编程的中断事件有124个,分别为EVT4~EVT127。CPU可以响应的中断有16个,其中用户可以编程控制的中断有12个,分别为INT4~ INT15。

DOORBELLn_ICSR(n=0、1、2、3)为门铃中断状态寄存器,其中低16 bit位有效,对应门铃包中的16个信息bit。DOORBELLn_ICCR(n=0、1、2、3)为门铃中断条件清除寄存器,其中低16 bit位有效,将该16个bit置为1时,会清除DOORBELLn_ICSR中的对应bit位。DOORBELLn_ICRR、DOORBELLn_ICRR2为门铃中断条件映射寄存器,每4个bit一组,共有16组。它的每组和一个门铃信息bit对应。如此,可以将某个门铃信息bit(即门铃中断请求)通过该4 bit组映射到中断事件。中断条件映射寄存器每个4 bit组为0000时,对应的中断事件为INTDST0,4 bit为0111时,对应的中断事件为INTDST7,共有8个中断事件组合。4 bit的值大于7时无意义。需要注意的事:DSP6455中给SRIO分配的中断事件只有3个,分别为INTDST0(中断事件编号20)、INTDST1(中断事件编号21)、INTDST4(中断事件编号22)。所以将门铃中断请求映射到中断事件时,只能选择上述3个事件。上述3个中断事件经过中断选择寄存器INTMUXn(n=0、1、2、3)可以映射到DSP6455的12个中断。

此处在实际设计开发时,需要特别注意的是:INTDSTn_RATE_CNTL(n=0~7) 是 8个 中断事件的中断速率控制寄存器。只有当程序写了INTDSTn_RATE_CNTL的值后,在收到门铃包时,才会产生相应的中断逻辑信号。所以在程序初始化时或者门铃中断处理完成后,必须重新写一次INTDSTn_RATE_CNTL。

5 SRIO传输验证

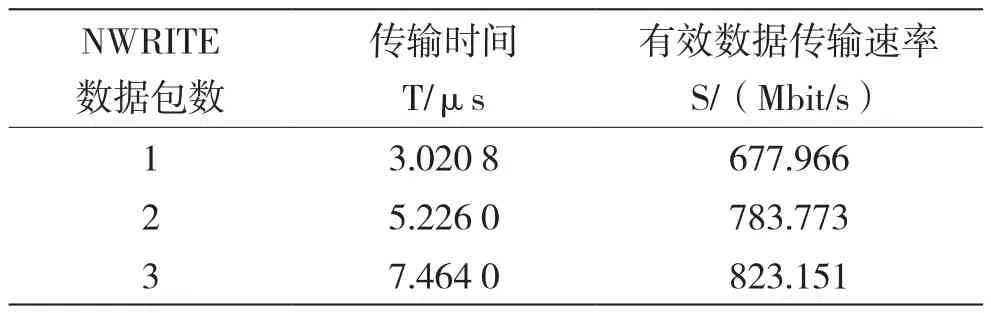

本文对SRIO的实际传输速率进行了测试。测试方法:发送一包或多包NWRITE数据包,接着再发送一个门铃包。发方开始发送时由DSP输出一个低脉冲,收方接收到门铃信号后由DSP输出一个低脉冲,两个脉冲的下降沿之间的时间差即为传输时间T1。发方仅发送门铃包,该时间差为门铃包传输时间T2。T=T1-T2,T即为NWRITE数据包的传输时间。每个NWRITE数据包发送的有效信息为256字节,有效数据传输速率S=256*8*n/T,n为NWRITE数据包数。用示波器测量出两个低脉冲的时间差值T1、门铃包传输时间T2。示波器实测的数据和有效数据传输速率测试结果见表1。

表1 SRIO传输速率

本文接着进行了稳定性测试。发方在发送NWRITE数据包时,计算出数据的校验值CRC16,并将CRC16放在数据包的最后。收方接收数据后,进行CRC16校验,并统计正确包数。测试结果如表2所示。

表2 SRIO传输稳定性

6 结 语

相较于以前的总线传输技术,SRIO技术传输速率快,连线少,并且可以灵活构成多种形式的传输网络。DSP6455作为一款TI公司高速处理器,其CPU主频高,数据处理能力强。本文利用DSP6455,作为实现SRIO互连的物理器件,设计了通过SRIO高速连接多个板卡的多任务处理平台。描述了平台总体设计和软件设计思路,并详细介绍了SRIO模块的软件设计和实现。通过实验验证项目,测得了SRIO高速的有效数据传输速率;通过大数据量的传输实验,验证了SRIO的传输可靠性。