AD9364射频捷变收发器的配置方法

2019-08-16孙南南周洪波张隽康尚国武

孙南南,周洪波,张隽康,尚国武

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

0 引言

软件定义无线电(SDR)架构可以简化系统设计,实现无线电平台标准化。提出SDR已经二三十年[1-4],限于高昂的成本和复杂的实现方案,一直以来是少数高端应用的独宠。ADI推出的集成式RF收发器AD9364的优势在于为多种无线电方案提供统一的可再编程无线电平台[5]。

AD9364射频捷变收发器具备灵活性、可配置性、低功耗、体积小、重量轻以及支持现场升级等优点,在无人飞行器、LTE通信基础设施以及防务电子等领域有较大的应用价值[6-10]。AD9364将信号链封装于一个软件可配置IC之中,包括混频器、发射和接收通道的频率合成器、模拟滤波、数据转换器和其他功能模块。而一般的集成式宽带捷变收发器解决方案在性能、可调带宽方面受限,缺乏实用性、高性价比的SDR能力,因此,AD9364自上市以来供不应求。

目前,国内基于AD9364的研究主要集中在平台架构设计,以及该芯片的指标参数和芯片架构,这些在官方手册中有比较全面的介绍[11]。但是涉及在实际工程中的使用并没有详尽的研究,尤其是配置方法和实际应用中遇到的一些问题。

本文基于现有AD9364常见平台架构设计方案[12-15],结合实际工程应用中的经验,详尽阐述了AD9364射频捷变收发器的4种配置方法:FPGA逻辑配置方式、FPGA片上Nios配置方式、FPGA+SDRAM配置方式与FPGA+单片机配置方式。描述了其软硬件设计方案,分析了各方法的适用场景和优缺点,为AD9364和AD936x系列的使用提供了指导。

1 AD9364的芯片架构及控制接口特性

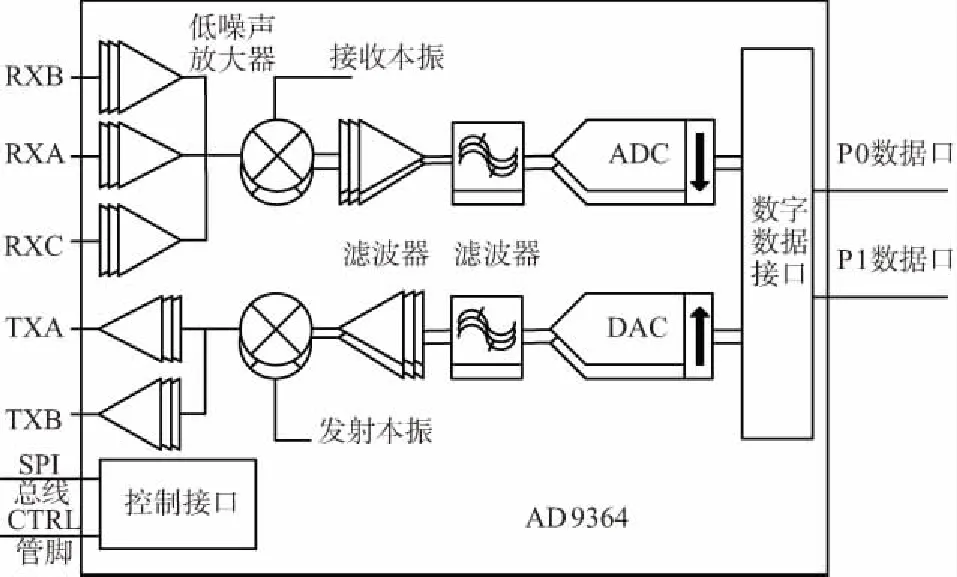

ADI公司的AD9364射频捷变收发器作为一款单发单收的零中频信号发射模块,由发射器、接收器、滤波器、混频器、ADC、DAC、数字数据接口及控制接口组成,其芯片架构如图1所示。

图1 AD9364芯片架构

AD9364的接口设计主要分为2部分:芯片与基带处理芯片(比如FPGA)之间的12位并行数据端口P0,P1,用于芯片配置寄存器的控制参数传输的控制接口。

AD9364通过内部寄存器映射表实现可配置和灵活性的特点。芯片内部的寄存器虽然多达上千个,但是这些寄存器按照其主要功能被分为基带锁相环频率设定、发送与接收信号带宽设定、数字数据接口设置、发送与接收射频频点设定、接收功率控制和发射功率设定等。以上这些模块需要根据实现的功能来设计,而像低通滤波器参数设定、正交校正与直流补偿这些功能模块的寄存器值一般参照默认值设置即可。

AD9364提供了2种配置控制接口的方式:SPI控制和管脚配置。在SPI控制模式下,AD9364通过芯片上的SPI接口与外围控制模块交互,可以实时修改芯片的所有寄存器值,尤其是芯片当前工作状态(比如:频分双工FDD、时分双工TDD、发射状态和接收状态)。而在管脚配置模式下,外围控制模块通过对芯片特定的几个管脚进行高低电平控制,只能实现芯片当前工作状态的切换,应用范围比较小。实际使用中,结合 SPI控制和管脚配置一起使用,只需要设置某几个寄存器参数即可,这样可以直观简单地控制芯片当前的工作状态。

2 FPGA逻辑配置方式

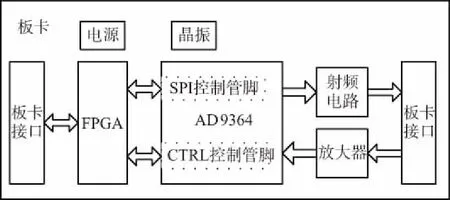

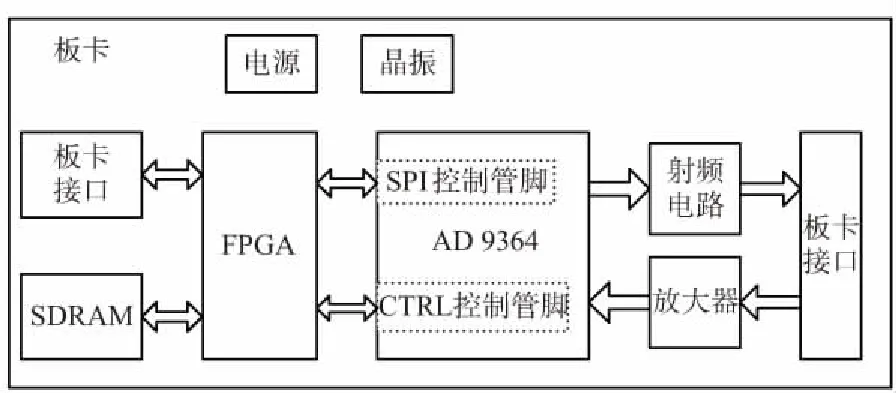

采用FPGA逻辑配置方式的硬件设计如图2所示。FPGA自身具有强大的时钟、运算及扩展能力,只需将FPGA与AD9364之间的管脚在物理上正确连接,通过编程实现与AD9364之间的SPI通信。从硬件设计角度分析,板卡可以通过一块电源芯片、一片晶振及相关电路设计满足FPGA,AD9364及其他器件的所有需求,从而减小板卡尺寸并节约成本。

图2 FPGA逻辑配置方式

根据图2 的设计,在FPGA中利用VHDL语言或Verilog语言编程实现AD9364相关寄存器的赋值,通过SPI接口配置AD9364。同时AD9364的CTRL控制管脚只需要高低电平就可以工作,因此在FPGA中,对这类管脚的控制非常简单。

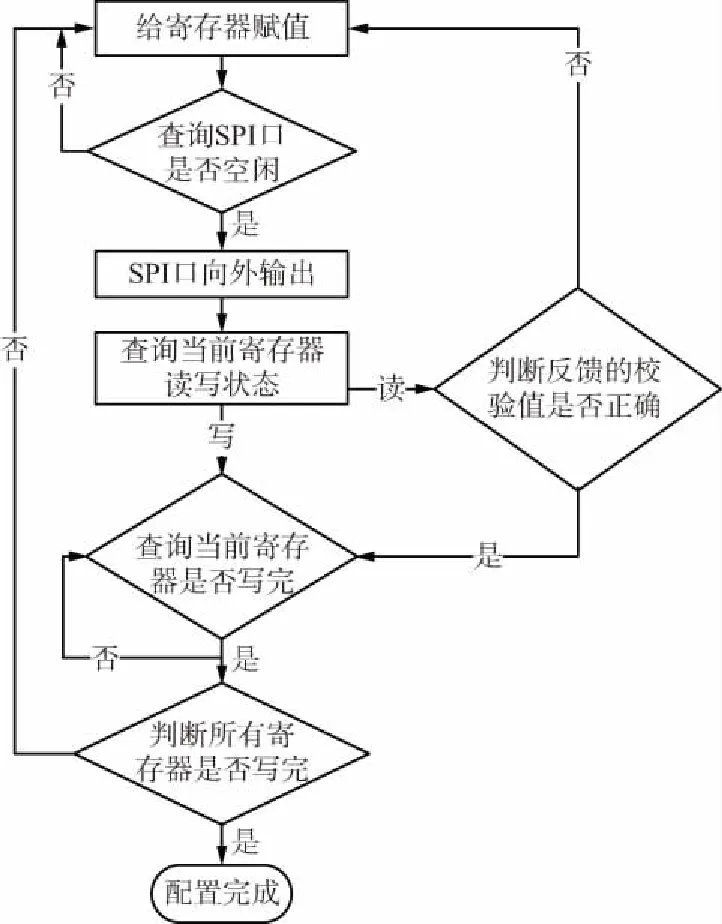

FPGA中AD9364寄存器赋值模块的软件设计如图3所示。

图3 FPGA逻辑配置方式软件设计

首先按照顺序依次给寄存器赋值,查询SPI口的状态决定是否写数,在某些寄存器写完值后等待AD9364返回的校验值,如果校验值正确则继续给寄存器赋值,反之重新给该寄存器赋值等待校验正确。

从硬件、软件设计角度分析,该种配置模式的使用较简单,涉及的硬件电路和开发环境较少。但是,AD9364的配置是一个闭环过程,通过AD9364与外围配置模块之间配置环节的校验功能,根据反馈的信息更加精确地调整AD9364的工作状态,从而更好地实现设计的功能;同时把当前工作状态反馈给外围配置模块。而FPGA逻辑配置方式大量简化了校验功能,直接单向输出控制指令,对校验的判断仅限于是否配置正确而没有校准功能。如果校验一直失败程序会陷入死循环,导致AD9364工作指标的偏差。AD9364每个寄存器的位宽是8 bit,每个比特代表不同的功能,该芯片的某些功能有时需要几个寄存器一起配合实现,而该芯片涉及了基带信号处理、射频信号处理和模拟电路等多方面知识。该种配置方式需要给所有相关的寄存器依次赋值,这就需要准确地知道这些寄存器的功能,从这一角度来说,这种配置方式有一定的难度。

3 FPGA片上Nios配置方式

图2与FPGA逻辑配置方式一致。从硬件设计来说二者一致,不同的是该种配置方式对FPGA性能要求高,需要占用3 M左右的FPGA片上RAM资源。因此,在FPGA选型时需要注意。

根据图2 的设计,该种配置方式需要使用FPGA片上自带的Nios II系列软核处理器,作为Altera公司推出的第2代FPGA嵌入式处理器,其性能超过200DMIPS。在Nios II开发环境下使用C/C++语言编程实现AD9364相关寄存器的赋值,通过SPI接口配置AD9364。同时,在FPGA中通过VHDL语言或Verilog语言编程实现对AD9364的CTRL管脚的控制。

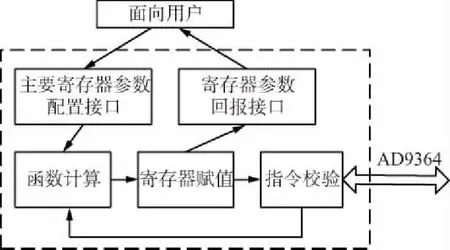

FPGA片上Nios配置方式的软件设计如图4所示。

图4 FPGA片上Nios配置方式软件设计

软件设计主要分为5部分:主要寄存器参数配置接口、寄存器参数回报接口、函数计算、寄存器赋值和指令校验。用户通过主要寄存器参数配置接口模块设计AD9364工作指标,函数计算模块根据参数值进行相关运算,寄存器赋值模块根据其输出结果给AD9364的相关寄存器赋值,经由指令校验模块处理后通过FPGA管脚输出给AD9364,指令校验模块根据AD9364返回的指令调整相关寄存器的偏差并反馈给函数计算模块,从而形成一个闭环的配置校验过程。同时,用户通过寄存器参数回报接口实时观测AD9364的寄存值来分析其工作状态。该种软件设计方式的主要优势如下:

① 用户体验佳,简洁、高效和直观地使用AD9364;

② 形成一个完整的闭环配置校验过程,更加精准地调整AD9364的工作状态。

从硬件设计角度分析,该配置模式的硬件电路比较简单。从软件设计角度分析,该种配置模式实现了AD9364的闭环配置过程,但是需要研发人员熟练掌握C/C++语言编程。Nios II作为FPGA片上嵌入式处理器,在跨芯片平台、跨芯片系列使用时并不适用,并且不支持软件开发工具的跨界使用。

4 FPGA+SDRAM配置方式

采用FPGA+SDRAM配置方式的硬件设计如图5所示,与前2种配置方式相比较,板卡上增加了一片SDRAM芯片及相关电路,从而节省了FPGA片上RAM资源。

众所周知,FPGA片上RAM资源是宝贵的,一般中端系列的FPGA片上RAM资源约12 M左右。相较于前一种配置方式,该种配置方式将Nios II处理器运行过程中需要占用的内存资源转移到SDRAM芯片内,从而释放了原本需要在FPGA片上占用的RAM资源,进而降低FPGA芯片的指标要求并降低成本。

图5 FPGA+SDRAM配置方式

FPGA+SDRAM配置方式的软件设计方法与FPGA片上Nios配置方式一致,也需要借助Nios II开发环境,形成一个完整闭环的配置校验过程。

从硬件设计角度分析,该配置模式的硬件电路相对复杂,增加了额外成本。从软件设计角度分析,该配置模式实现了AD9364的闭环配置过程。虽然SDRAM凭借其极高的性价比,广泛应用于高速数据存储等设计中,但是相对于SRAM等其他存储器件,SDRAM的控制相对复杂[16]。在实际工程应用中发现,SDRAM内部的命令发送和数据传输都以同步工作时钟为基准,因此对其与FPGA交互的44条信号线(数据线和地址线)的时钟同步要求很高,会发生转发给AD9364的指令无法解析的情况。这种情况下只能通过改善同步工作时钟与信号线的时序关系来解决,增加了程序运行的风险。同时SDRAM与FPGA交互的管脚数为54,大量占用了FPGA的IO口资源。

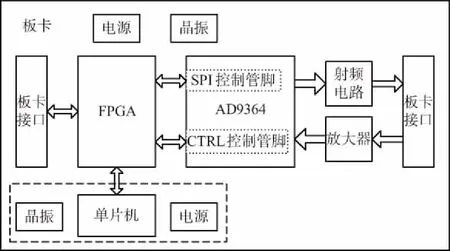

5 FPGA+单片机配置方式

采用FPGA+单片机配置方式的硬件设计如图6所示。与前2种配置方式相比,板卡上增加了一片单片机及相关电路,可以节省FPGA片上RAM资源,但是增加了板卡的尺寸和设计复杂度。

图6 FPGA+单片机配置方式

相对于FPGA逻辑配置方式和FPGA+SDRAM配置方式,该种配置方式用单片机替代了FPGA片上嵌入式处理器,用Keil替代Nios II开发环境,FPGA只作为AD9364和单片机的电平转换接口,不做任何信号处理。

该配置方式的软件设计方法与前2种配置方式一致,只是在Keil开发环境中用C/C++语言编程,最终形成一个完整闭环的配置校验过程。

从硬件设计角度分析,该种配置模式的硬件电路最为复杂,虽然单片机成本低(约15元一片),但需要给单片机提供单独的供电、晶振、调试接口和相关电路,因此增加了板卡尺寸和附带成本。该种方式附带总成本仍然比一片SDRAM成本的一半要少。单片机与FPGA交互的管脚数仅为2,大大节约了FPGA的IO口资源。从软件设计角度分析,该种配置模式不仅能实现AD9364的闭环配置过程,还可以跨芯片平台、跨芯片系列使用,移植性强,但是需要研发人员熟练掌握单片机的开发。

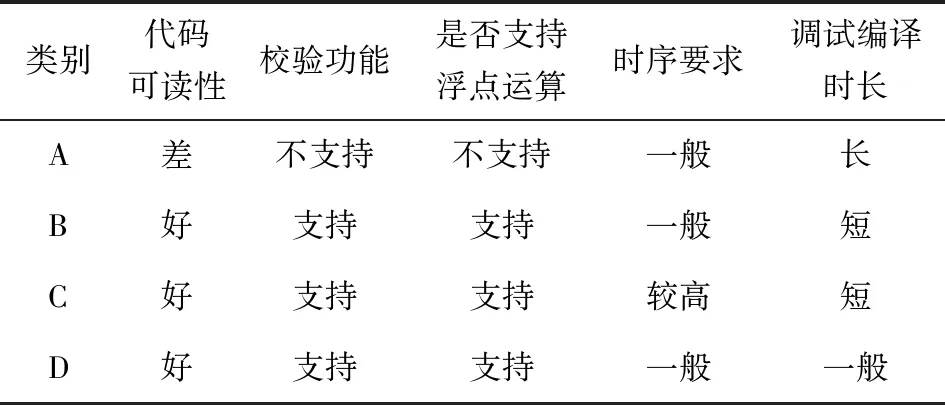

6 AD9364配置方式的分析

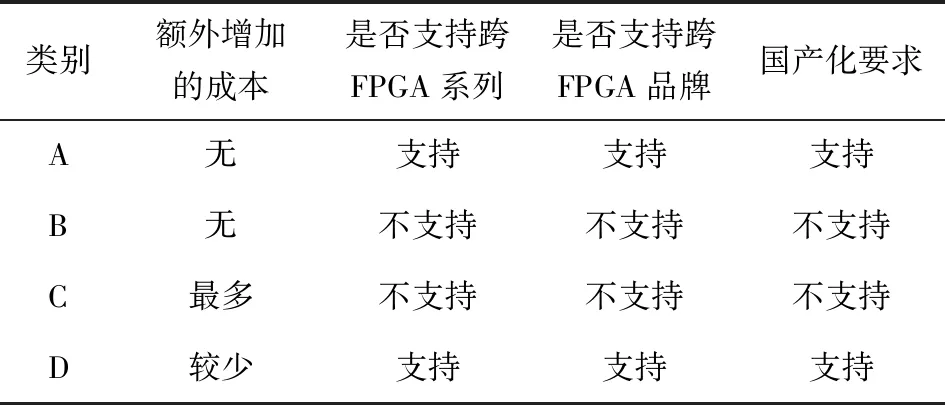

根据上述介绍的4种配置方式,从软件设计和硬件设计2个角度分析各自的特性。表1和表2以类别A,B,C,D分别表示FPGA逻辑配置方式、FPGA片上Nios配置方式、FPGA+SDRAM配置方式和FPGA+单片机配置方式。

AD9364四种配置方式的软件设计特性如表1和表2所示。

表1 软件设计特性

类别代码可读性校验功能是否支持浮点运算时序要求调试编译时长A差不支持不支持一般长B好支持支持一般短C好支持支持较高短D好支持支持一般一般

表2 软件设计特性

AD9364的4种配置方式的硬件设计特性如表3和表4所示。

表3 硬件设计特性

表4 硬件设计特性

类别额外增加的成本是否支持跨FPGA系列是否支持跨FPGA品牌国产化要求A无支持支持支持B无不支持不支持不支持C最多不支持不支持不支持D较少支持支持支持

结合表1~表4,可以发现:

① 对AD9364配置程序移植性要求高,只能采用FPGA逻辑配置方式和FPGA+单片机配置方式;

② 对板卡尺寸、复杂度和成本要求高,建议采用FPGA逻辑配置方式和FPGA片上Nios配置方式;

③ 对研发人员要求低,建议选择FPGA逻辑配置方式;

④ 对程序可读性、调试便捷性要求高,建议采用FPGA片上Nios配置方式、FPGA+SDRAM配置方式、FPGA+单片机配置方式。

7 结束语

在ADI公司提供的配置方法的基础上,根据实际工程经验总结了射频捷变收发器AD9364的4种配置方式并分析了常见问题,从硬件设计复杂度、硬件设计成本、软件开发复杂度及是否满足国产化要求等方面分析。FPGA逻辑配置方式成本较低但调试最为复杂,FPGA片上Nios配置方式成本较低但移植性差,FPGA+SDRAM配置方式节省FPGA片上RAM资源但开发复杂,FPGA+单片机配置方式移植性好但板卡尺寸最大。阐述的4种配置方式可以灵活满足各种硬件平台架构,从而满足大多数软件无线电平台的应用需求。