非均匀多载波信道分路技术的FPGA设计方法

2019-08-16李辉,岳田

李 辉,岳 田

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

0 引言

数字信道分路技术是目前软件无线电及卫星通信领域研究的热点,欧洲的EuroSkyWay及美国的WGS[1]等系统采用的关键技术都是基于数字信道分路。数字信道分路大体可以分为均匀和非均匀2种信道分路方式[2],采用基于多相滤波器组的均匀信道分路方法只能实现多路相同符号速率、相同间隔的均匀信号分路[3],具有处理路数多,实现复杂度低,降低中心站解调器成本等优点,但应用具有局限性,对于某些系统应用的场合适应性较差。而采用基于完全重构调制滤波器组[4]的非均匀信道化技术,通过分析和综合等数字处理可在一定带宽内实现多路不同符号速率、任意频点的非均匀信号的灵活重构,增加交换结构,还支持卫星柔性转发器设计[5-6]。本文基于完全重构调制滤波器组的信道化技术,提出一种非均匀多载波数字信道化分路的FPGA设计方法,采用资源复用及模块化设计,结合解调可实现非均匀多载波整体解调器,将其应用于大容量卫星通信系统的中心站,能够使系统处理组网方式更加灵活,处理能力更强,并兼容均匀多载波整体解调[7]的功能。

1 基于调制滤波器组的非均匀信道化技术理论推导

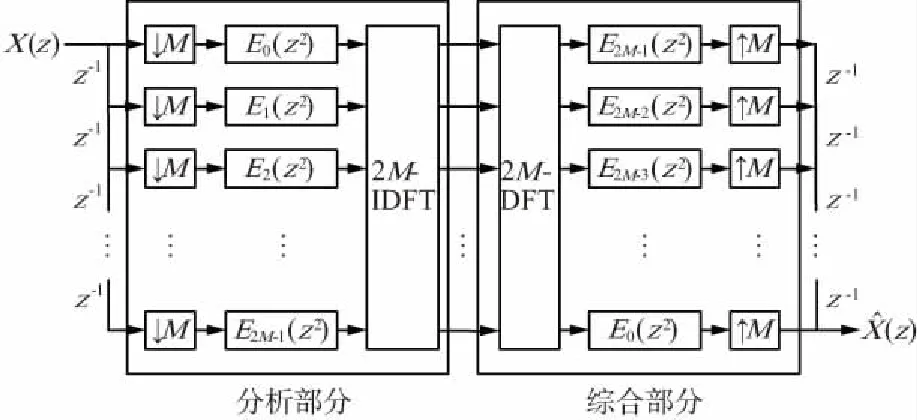

对于调制滤波器组而言,有2种典型形式:DFT调制滤波器组和余弦调制滤波器组[8],二者均可以通过设计实系数的原型滤波器经调制获得,文献[9-10]对此进行了详细描述。经过推导余弦调制滤波器组可以转化为DFT调制滤波器组的形式[11]。若一个原型滤波器可以使其对应的余弦调制滤波器组满足完全重构条件,则同样可以作为一个DFT调制滤波器组的原型滤波器使之满足完全重构条件。以下采用DFT调制滤波器组结构,假设原型滤波器h(n)的系数长度为2mM(m为正整数),滤波器组的子信道数为2M,则对应分析部分滤波器Hk(z)和综合部分滤波器Fk(z)可表示为[12]:

令多相成分为:

则上式可以写成:

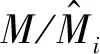

图1 完全重构DFT滤波器组的多相结构

分析滤波器组将[0~2π]等分成2M份,由于子带信号的带宽和频带位置分布各不相同,因此,每个子带信号可能占据分析滤波器组的不同数量的子信道。

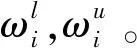

图2 完全重构调制滤波器组的优化结构

2 非均匀多载波信道分路FPGA设计

根据完全重构调制滤波器组的优化实现结构提出一种非均匀多载波信道分路的FPGA设计方法。非均匀信道分路模块包括分析和综合2个部分,其中分析部分有分析滤波器和IFFT模块,综合部分有综合FFT模块、综合滤波器模块以及上采样模块。

2.1 分析部分设计

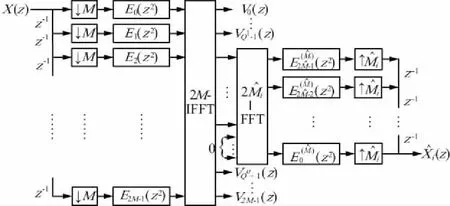

分析滤波器模块可由图3中多组双端口RAM串行实现,例化深度为N/2×M,写入时钟为采样钟fs,读出为高倍工作时钟fw,其中fw>2fs。由于分析滤波器每组M个系数中实际有效系数为M个,其余为零,故采用高倍工作时钟复用后,每隔一组RAM读出一个数据分别与对应系数做乘法运算,这样共有M组乘法器,每组N/2个数据共用一个乘法器,节省了大量的乘法器资源。分析滤波器模块具体实现如下所述:数据在采样钟fs下顺序写入RAM1 中的0~N/2-1地址后,原来RAM1中的N个数据依次推入下一组RAM2的0~N/2-1地址中,其他RAM写入数据以此类推,每完成一组N个数据写入后,从每隔一组RAM块的0~N/2-1地址中读出一个数据并与相应滤波器系数相乘相加完成滤波过程,读完数据后等待下一组N/2个数据写入。为了使在N/2/fs时间内完成N点的IFFT运算,还需要将前段时间内读出的N/2个数据缓存到后一时间段内,与后一段读出的N/2个数据合并成N个数据进行IFFT运算。

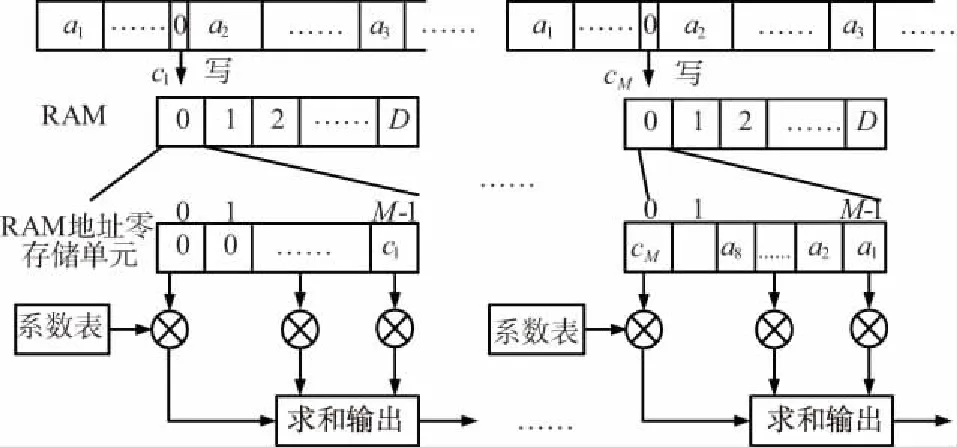

图3 分析滤波器模块的实现结构

2.2 综合部分设计

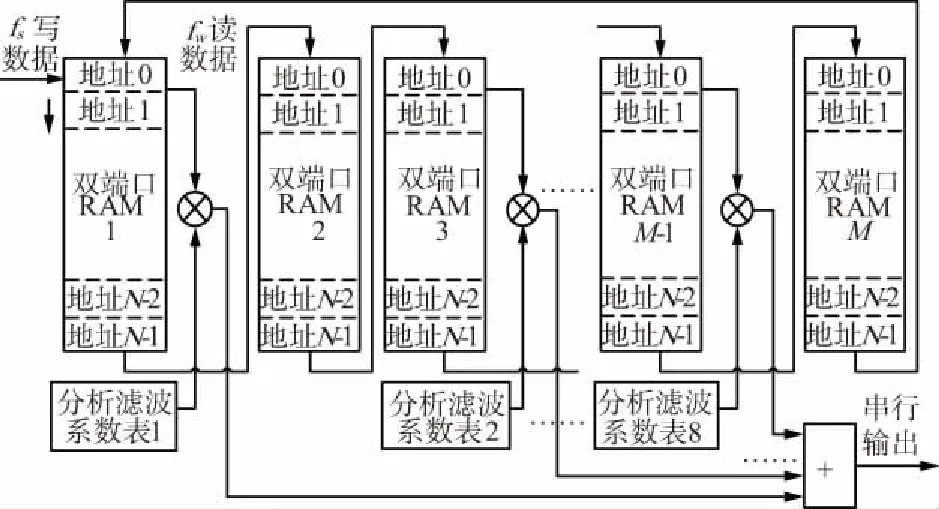

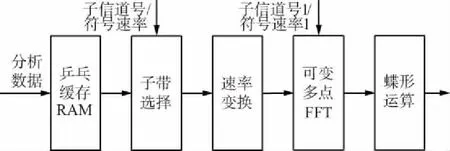

综合FFT处理模块由乒乓缓存RAM、子带选择模块、速率变换模块、可变多点FFT运算模块以及蝶形运算模块组成,如图4所示。

图4 综合FFT处理模块组成

先将N点IFFT数据进行乒乓缓存,根据各载波起止子带号和载波速率等参数,并按照起始子带号由小到大的顺序将各载波参数排列,根据起止信道号从乒乓缓存后的N个子信道中提取出各载波子信道数据,之后依据各载波占用子信道长度和起始子信道号进行数据速率变换,变换后的数据乒乓缓存在RAM中;然后对各载波符号速率分别完成不同长度Ni的FFT处理,FFT支持可变多点的FFT计算,同时为了节省处理时间、处理更多路数,对于长度较长的FFT点数计算采用分解为两段或四段的FFT的蝶形运算来实现。经过速率变换后数据速率可以降低至4倍符号速率。

综合滤波器处理模块结构如图5所示。利用双端口RAM实现,深度最大数据长度为N,宽度为M/2×Q比特,每M个数据ci循环存储在同一个RAM地址中,需要注意的是综合滤波器系数相隔一列都为零,因此只需要间隔存储一组数据,每隔M组数据ci分别与对应的综合滤波器系数相乘相加并输出,不同数据长度对应的系数可由最长N点系数抽取得到,同时每隔M组数据每一个RAM存储单元内的数据循环更新一次。其中每M个数据循环存储在同一个RAM地址中,不同数据长度对应的系数可由最长N点的系数抽取得到,Q为量化比特数,ci(i=1,2,3,…,M)为写入数据。

图5 综合滤波器模块结构

综合滤波之后为上采样模块,因实现结构简单,在此不做详述。

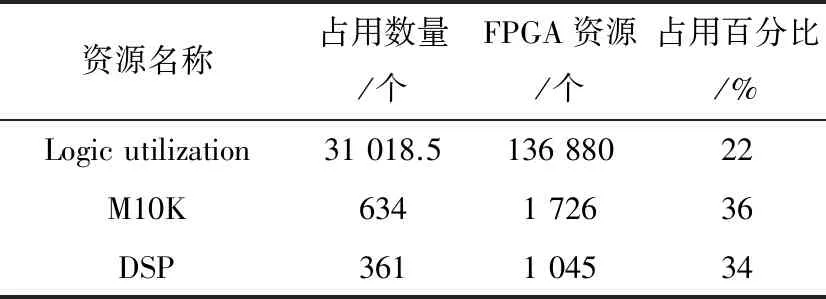

3 硬件实现

按照以上非均匀多载波信道分路技术的FPGA设计方法,在Intel公司的Arria V系列的FPGA芯片上实现非均匀信道分路功能,最大处理工作时钟为150 MHz,能够实现一定带宽内、多达几十条载波速率为32 ksps~16 Msps任意排列的混合信号的重构。FPGA占用资源如表1所示。从表1可以看出,关键的逻辑资源、乘法器模块(DSP)及存储资源的使用均约占整个芯片资源的1/3左右,采用单个150 MHz时钟作为工作时钟,易于工程实现。

表1 FPGA主要资源占用情况

资源名称占用数量/个FPGA资源/个占用百分比/%Logic utilization31 018.5136 88022M10K6341 72636DSP3611 04534

将该信道分路应用于非均匀多载波整体解调实测结果为:对32路低速非均匀突发信号同时整体解调时,在Eb/N0大约为4.5 dB,采用QPSK调制、1/2LDPC编码时误码率可以达到1×10-6,满足工程应用。

4 结束语

提出的非均匀多载波信道分路技术的FPGA设计方法易于工程实现,已经应用于信道转发、多载波整体解调等诸多项目中,从而证明这种非均匀多载波信道分路技术的FPGA设计方法的实现可行性,能够满足系统要求的传输性能。相对于均匀多载波信道分路技术的局限性,该技术能够更好地适应未来大容量方向的发展,应用场景也更加宽广。

在实现过程中,发现当载波速率跨度较大时,该方法需要对不同的载波速率分段并行处理才能完成全部载波分路,FPGA的硬件资源占用将增加,针对这一问题,在后续的工程化应用中需要进一步深入研究。