基于DM9161EP的嵌入式光纤以太网传输系统设计

2019-07-17田晔非

周 鑫,田晔非

(1.重庆电子工程职业学院通信工程学院,重庆 401331;2重庆大学电气工程学院,重庆 400044)

0 引言

随着嵌入式网络技术的发展,嵌入式以太网在工业制造、智能监控、测试系统等采用嵌入式芯片的各类系统中广泛应用,特别在工业领域中,数字化水平逐步提高,嵌入式设备均需要接入统一的现场网络,供DCS、MES等集中控制、管理软件使用[1]。工业嵌入式设备分布在厂区各地,网络传输距离过远,传统的嵌入式以太网采用网线连接,网线为双绞线传输结构,当长度过长时受电阻和电容的影响会导致网络信号衰减和畸变,因此影响信号的传输稳定性,规定单POE传输网段距离不能超过100 m,而不能满足超远距离传输需求。使用搭建网络中继器的方式不但增加成本,而且对安装调试,调试维修带来困难,中继器的设置也会产生一定传输延迟,降低传输效率[2]。

光纤以太网是目前应用非常广泛的技术,是指利用在光纤上运行以太网LAN数据包接入网络,在改变网络传输媒介的基础上,使以太网网络可以进行超长距离的传输[3],在嵌入式设备基础上实现光纤以太网传输能够很好地适用于工业应用的超长距离网络传输需求。本文将通过STM32F407芯片和DM9161EP芯片实现光纤以太网传输的数据传输,满足嵌入式设备超长距离传输需求[3]。

1 系统总体框架

1.1 模块介绍

目前工业应用使用最广泛的嵌入式芯片为STM32F407芯片,它支持32位高性能指令集,最高可达168 MHz频率,内置高速存储器,有丰富的I/O接口和外设资源,其芯片内部集成了MAC(media access control)控制器,支持IEEE-802.3和IEEE-802.3u规范控制PHY(Physical Layer)物理层,对外提供MII与RMII总线接口与PHY连接,从而实现数据传输[4]。

DM9161EP是用于100Base-FX以太网的物理层收发器芯片,其完全符合IEEE-802.3和IEEE-802.3u规范,支持光纤上实现100 Mbit/s以太网标准。其可以通过可变电压的MII或RMII总线接口连接到MAC层。在对媒介侧提供了数据接口,可以与光纤收发器相连接,实现光纤传输[6]。

1.2 系统设计架构图

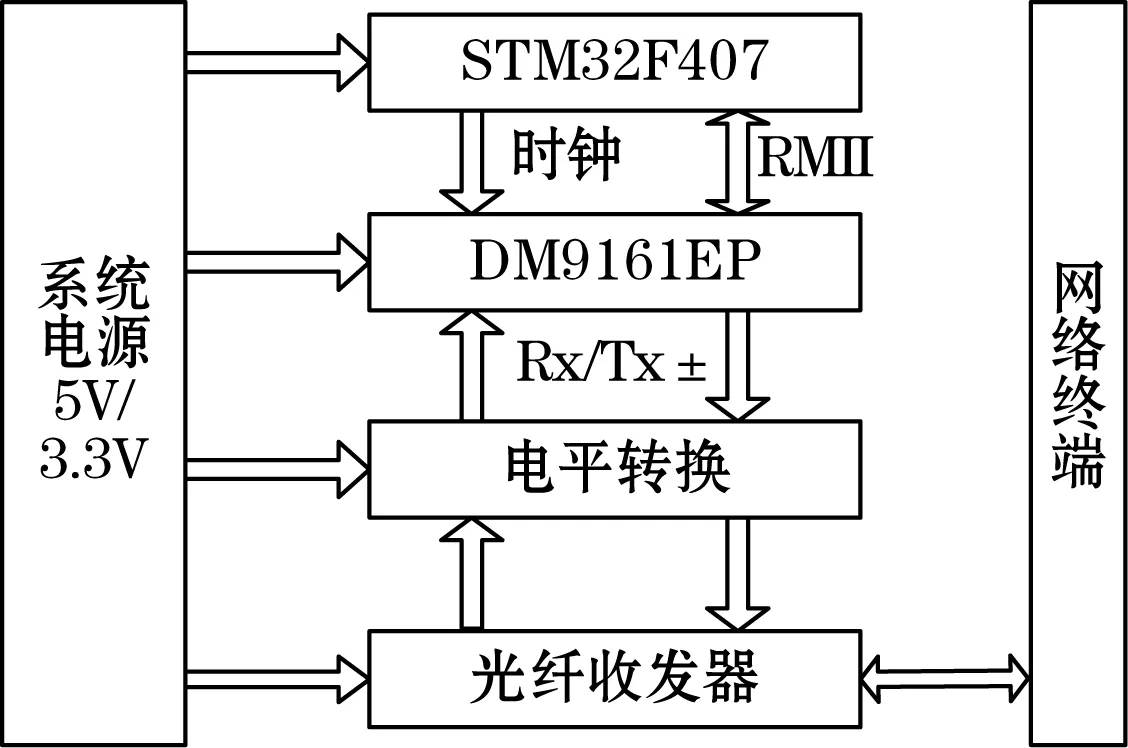

STM32F407芯片通过标准的RMII硬件接口与DM9161EP相连进行数据交互操作,可以减少I/O口的占用,节约芯片引脚资源,RMII总线需要50 MHz的晶体振荡器振为STM32F407的MAC及DM9161EP提供同步时钟,为节约成本,可直接采用STM32F407输出50 MHz时钟信号作为同步时钟。DM9161EP与光纤收发器通过Rx/Tx± 4个信号线与光纤收发器连接,通过光纤收发器发送至网络终端,光纤收发器为5 V 供电,其信号为0~5 V,而DM9161EP芯片信号为0~3.3 V ,因此需要加入电平转换实现信号的互转,使得信号正确匹配。光纤收发器将电信号报文利用光纤传输至网络终端,从而完成数据传输。系统需求电源为5 V和3.3 V,图1为系统整体框图。

图1 系统整体框图

2 系统设计实现

2.1 系统电源设计

根据系统设计架构,首先需要进行系统电源电路设计。在本系统中STM32F407芯片、DM9161芯片工作在DC 3.3 V电压,而光纤收发器工作在DC 5 V电压,为了此系统可以正常工作,必须给系统统一供电。外部供电设计为DC 5 V输入,因此必须设计DC 5 V-3.3 V的电源电路,在系统电源设计中应用了电压转换芯片AP1510设计降压型DC/DC变换器,实现电压转换。通过R1、R2、R3电阻将芯片输出配置为3.3 V,为系统提供所需的DC 5 V与DC 3.3 V工作电压。系统电源电路如图2所示。

图2 系统电源电路

2.2 系统硬件电路设计

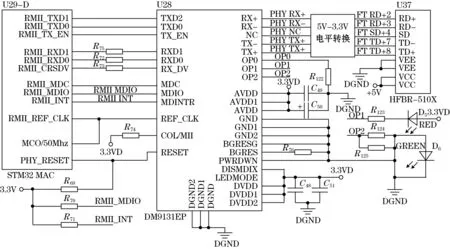

本设计是基于STMF407、DM9161EP和光纤收发器HFBR-501X的光纤以太网通讯模块设计。图3为系统硬件电路图,其中,STM32F407芯片通过站管理接口(SMI)访问PHY芯片,SMI通过时钟线MDC与数据线MDIO向PHY发送控制数据或者接收状态信息。系统通过RMII接口进行MAC层与PHY层的数据传输,RMII是精简介质独立接口,是一种专用于MAC与PHY相连接的通用总线,包括7个数据和控制信号的引脚[7],RMII总线信号为:TXD0、TXD1、TX_EN、RXD0、RXD1、CRS_DV、REF_CLK 7路,其中TXD0、TXD1为一组数据发送信号;TX_EN为发送使能信号;RXD0、RXD1为一组数据接收信号;CRS_DV为数据接收有效信号;REF_CLK为连续时钟信号,该信号提供数据发送与接收时的参考时序,在RMII中当传输速度在10 Mbit/s时应为5 MHz,当传输速度在100 Mbit/s时应为50 MHz,为了节约资源采用STM32F407的MCO输出50 MHz频率信号作为时钟源,提供参考时序,将其直接与对应信号进行直连。INT信号为PHY芯片的初始化信号,用于系统初始化时对PHY的操作。RESET信号为PHY芯片的重置信号,用于芯片重置,由STM32F407控制。在STM32F407与DM9161EP的接线中,MDIO、INT与RESET信号为低电平有效,因此连接上拉电阻对其进行信号拉高。

DM9161EP芯片需要通过上电时相关配置引脚的电平状态来进行芯片初始化配置,其物理通信地址通过26~29引脚,以及25引脚来确定的,本系统在RMII模式下只连接了28、29引脚(RXD0、RXD1),其余为悬空配置,在上电时引脚都为高电平,因此本系统PHY芯片物理地址为0x00。因为对媒一侧连接光纤收发器,所以需要使PHY芯片工作在100Base-FX模式下,芯片的工作模式配置引脚为11~13引脚(OP0、OP1、OP2),并将电平状态分别配置为高、低、低。

图3 硬件电路图

DM9161EP芯片通过RX+、RX-、TX+、TX-线实现与光线收发器HFBR-510X的数据收发,通过45引脚连接SD信号,用于检测信号是否有效。因为DM9161EP芯片引脚电平范围为0~3.3 V,而光线收发器HFBR-510X引脚电平范围为0~5 V,采用直连方式会造成数据错乱,甚至硬件损坏的不良后果,因此加入电平转换模块,如图4所示,利用电阻分压对RX+、RX-、TX+、TX-以及NC-SD信号进行电平转换,以保证电平匹配,让PHY芯片RM9161EP与光纤收发器HFBR-510X数据收发正常。

图4 电平转换电路

2.3 软件设计

2.3.1 DM9161EP驱动

DM9161EP芯片的驱动是实现设备联网的基础,芯片驱动就是STM32F407通过MAC控制器控制PHY芯片,访问与控制DM9161EP芯片内存储器,如控制寄存器,PHY寄存器、以太网缓冲器[7],最终实现STM32F407可以发送与获取以太网数据包。DM9161EP驱动包括初始化、数据包发送与接收。

DM9161EP初始化是对MAC与PHY进行初始化配置。首先STM32F407对RMII端口GPIO进行配置,并且控制MCO输出50 MHz频率信号,设置完成后就可以对DM9161EP进行访问,对DM9161EP进行参数配置,设置PHY地址0x00,工作模式为RMII、100 Mbit/s全双工,最后配置本地MAC地址,同时设置MAC滤波,使能接收和发送,设置网络中断,网络中断用于检测是否接收到从硬件传输至本地的以太网数据包,使用中断的方式比轮询方式具有更高的效率。

STM32F407会把从DM9161EP芯片中接收/发送的数据信息存储在一个高速接收/发送FIFO中,数据包通过DMA进行接收/发送FIFO与内存缓冲区之间的以太网数据传输,DMA通过DMA描述符进行控制,接收与发送描述符被存储在2个不同的描述符列表中,本系统选用链表结构方式进行连接,DMA描述符列表中的最后一个描述符指向第一个,形成链式结构。这2个列表的基址分别写入在STM32F407芯片的ETH_DMARDLAR寄存器与ETH_DMATDLAR寄存器中[10]。如图5所示为采用链表结构,DMA常规描述符Control与Status为描述符控制和状态描述;Buffer Count为描述指向缓冲区Buffer的长度;BufferAddress用于保存该描述符指向的内存缓冲区地址;Next Descriptor保存下一个描述符的地址,当列表最后一个描述符则保存列表首位描述符的地址。

图5 输入或输出DMA描述符与内存缓冲区关系

根据DMA描述符特性,DM9161EP_Rx_Packet()函数为以太网接收数据函数,将以太网接收的数据打包成一个结构体返回,该结构体包含有指向DMA描述符的指针,通过该指针获取以太网数据包所在的位置,通过描述符列表获取完整的数据并保存至缓冲区内。DM9161EP_Tx_Packet()函数为以太网发送数据函数,其实现过程与接收函数类似,将缓冲区数据传入DMA描述符,完成后使能发送标志位,从而将数据打包发送至以太网。

2.3.2 TCP/IP协议实现

本系统采用以太网传输,还需要实现TCP/IP协议,完整的TCP/IP协议族功能繁多,代码量也较为巨大,不能很好地适用于资源有限的嵌入式设备中。LWIP是一个开源的轻量级TCP/IP协议栈,该协议栈采用C语言编写,能够方便地移植至嵌入式设备中,其减少了内存的占用,因此被广泛地应用在嵌入式设备中使用。本文选用LWIP来实现TCP/IP协议。LWIP采用分层方式,把TCP/IP协议中每一个协议作为单独的模块,并且提供了该模块的访问接口。图6为LWIP模型与接口,应用层为应用程序,采用标准的netconn接口函数或应用层消息邮箱方式与上层进行交互,这样应用程序能够直接调用使用TCP/IP;对于下层网络驱动接口函数采用标准化函数接口,需要根据硬件驱动不同实现函数编写,其中包括low_level_input()底层输入函数接口与low_level_output()底层输出函数接口[11]。

图6 LWIP模型与接口

根据DM9161EP驱动,low_level_output()将需要发送的LWIP协议栈Pbuf缓冲区中的数据拷贝至DMA发送数据缓冲区中,并使用驱动发送至以太网。low_level_input()函数是在DM9161EP中提取接收到的以太网数据包,即DMA接收缓冲区中数据拷贝至LWIP协议栈Pbuf缓冲区中,将这个Pbuf返回,给LWIP进行以太网报文的分析处理。至此完成了LWIP在STM32F407系统中的移植。

3 测试结果与分析

根据设计的嵌入式光纤以太网系统进行制作,图7所示为样品板卡实物图,软件中设置样品板卡IP地址为192.168.1.103,通过多模光纤线连接至远端管理计算机,计算机IP设置为与样品板卡IP在同一网段,采用windows的ping指令进行ARP协议测试,可以检测通讯是否正常,通讯延时及丢包率情况,图8为计算机ping通样品板卡IP结果,说明本设计网络功能正常。

图7 样品板卡实物图

图8 计算机ping通样品板卡IP

网络测试正常后,进行光纤传输距离及性能的简单测试,测试方式为在不同传输长度时采用计算机ping指令发送10个数据包,并观察记录其丢包情况,延时时间情况,实验数据如表1所示,可见在700 m内网络传输稳定,没有出现丢包,网络延时较低,当高于700 m传输距离时,收光纤收发器功率及光纤接收传感器敏感度限制,光信号开始出现衰减,延时与丢包率逐渐上升,在高于850 m传输时出现了大量的丢包现象。实验表明本系统光纤传输距离在0~700 m网络连接快速稳定,传输距离远远高于传统网线传输的极限距离,充分说明本设计可以大幅度提高嵌入式以太网的超长距离传输。实验数据如表1所示。

表1 实验数据

4 结论

本文提出一种长距离的嵌入式以太网传输系统,其创新之处在于利用STM32F407与DM9161EP支持的IEEE-802.3u规范进行了光纤以太网的设计,将传输介质从电传播的网线变更为光传播的光纤,利用光纤的传输特性实现了超远距离的直连以太网传输。相对比其他嵌入式以太网传输,本设计具有快速稳定的超远距离传输能力,在0~700 m直连传输范围内表现稳定,无需在中段架设如中继器等信号增强设备,让嵌入式网络设备具备了超远距离传输能力,可很好地应用于需要远距离传输的应用系统中。本系统设计连接方式采用标准接口,能很方便地移植至其他嵌入式控制器,可以灵活地运用在工业制造、智能监控、测试系统等需要超长距离监控的领域。