基于FPGA的动态光弹仪声光同步系统的研制

2019-07-17陆铭慧胡俊涛纪炜辞石文泽

陆铭慧,胡俊涛,纪炜辞,石文泽

(南昌航空大学,无损检测教育部重点实验室,江西南昌 330063)

0 引言

在超声检测中,探头具有电能与声能转换功能,其声场辐射特性对检测方案的选择、工艺参数的确定具有指导意义,尤其对相控聚焦探头,更为重要。由于超声波肉眼不可见,一般采用光学方法进行观察,利用动态光弹法可直观显示超声的传播散射过程[1],也可观察探头的辐射、聚焦过程,对研究声波传播规律,探头辐射特性具有重要意义。

中科院声学所在20世纪80年代在国内率先搭建了一套动态激光光弹成像设备[2],清华大学物理系在国内首先研制了LED光源的动态光源设备[3],南昌航空大学、中北大学也有开发类似设备的报道[4-5]。近年来,随着声学研究的不断深入以及电子计算机技术飞速发展,在实际使用中对声场动态光弹仪的观测精度提出了更高的要求[6-7]。

为使动态光弹技术实用性提高,便于推广,本文提出一种通过LED光源与FPGA配合的方案,成功研制出了一套控制精度达2.5 ns的声光同步延时控制系统,此套方案成本低廉,理论上可在精度范围内实现声场不同程度的细节捕捉。

1 光弹法显示声波的原理

光弹法通常是用来观察透明静力模型中的应力分布,因超声波作为一种应力波动,实现对声波动态应力场的观测目前有2种有效的方案:一种是高速连续拍照法;另一种是冻结时刻频闪光源法。

高速连续摄像法通过高速照相机对受力模型中应力场的变化进行连续图像采集,然后通过专用软件播放图片来实现超声场的动态观测,此方法对硬件设备的要求非常高。冻结时刻频闪光源法是通过多次激励超声换能器,并配合调整每次声激励信号和光源点亮信号的延时间隔,来实现不同时刻声场图像的采集。此方法对摄像机要求不高,仅满足超声换能器激励的重复频率即可,超声激励信号工作一次,光源闪烁一次;配合专用软件可实现声场的实时动态观测,成本低廉,效果良好,便于动态光弹技术的推广普及。

本文研制的高精度声光同步延时控制系统即为配合冻结时刻频闪光源法实现不同时刻声场的图像的采集。

2 声场动态光弹观测仪系统构成及工作原理

2.1 声场动态光弹观测仪系统构成

如图1所示为本系统的结构框图,系统主要由以红色LED为核心的光学系统、以FPGA为核心的高精度声光同步延时控制系统、以具有外触发功能的超声脉冲发射系统以及使整套系统协同工作的上位机软件构成。与其他系统有所不同,本系统的超声换能器的激励功能是通过触发专用超声发射系统来实现的,这样不仅可以完成对专用超声换能器在不同的激励条件下的声场观察,还可实现专用超声换能器与专用超声发射系统之间整体匹配度的测试。

图1 系统结构框图

2.2 声场动态光弹观测仪工作原理

整套系统的工作原理为:上位机软件将每次控制光源闪烁的延时数据通过串口传送给FPGA,并启动FPGA内部的声光同步延时器;在该启动信号的作用下,声光同步延时器开始计数延时,与此同时启动信号也将作为同步高压激励系统的外触发信号,使超声脉冲发射系统单次动作,实现探头单次高压激励;当FPGA内部声光同步延时器延时完成后,FPGA将输出一个延时完毕信号,该信号将用以触发LED光源,实现一次光源闪烁,并配合CCD摄像机完成一次图像采集;通过设置FPGA内部声光同步延时器的延时数据值,可实现声场不同时刻的图像采集,从而实现探头声场的动态观测,其中声光同步延时器的计数精度将决定采集到声场动态图像的完整度。

3 声光同步延时控制系统的设计与实现

声光延时系统是整套系统设计的核心部分,是系统能否正常运行的关键,将其做在FPGA内部主要出于以下几点考虑:

(1)FPGA作为一种超大规模可编程逻辑器件其具有先进的制作工艺、丰富的逻辑存储资源、强大的自动布线方案,在实现电路系统高速运转的同时,还保证了系统具有极高的稳定性[8];

(2)任何的电路设计方案都是要经过不断实验、不断调整、不断完善的过程,FPGA具有可重复编程性,且程序烧录便捷,可快速实现设计方案验证,既缩短了设备的开发周期又节约了研制成本;

(3)所有电路均实现在一片FPGA中,可缩小设备体积,提升设备的便携性。

针对探头辐射声场成像高精度控制的需求,再综合设备开发成本,在此设计中选用CYCLONE V系列的FPGA,该芯片有77 kbit的可编程逻辑资源,4 884 kbit的内嵌式存储单元,6个小数级锁相环,内核工作频率最高可达550 MHz。价格低,完全可实现低成本高性能的设备研制方案。

整套系统主要由以8051软核为核心的微控制模块、以高精度差分计数器为核心的声光延时模块以及输出脉宽调节模块协同工作实现。

3.1 FPGA内8051软核的应用

FPGA作为一种大型的可编程逻辑器件,其内部有大量的可编程逻辑、存储单元,但其本身并不具备例如通信、运算等功能,若要仅用一片FPGA实现整套系统的控制,必需在其内部引入微控制单元。在此系统设计中,通过引入8051软核,实现这一功能。该核拥有标准8051完全兼容的指令系统的CPU,外部总线可以连接256字节的内部数据存储器RAM和最大至64 kbit字节的程序存储器ROM,且其成熟可靠,为本设计中的最佳选择[9]。图2为基于8051软核的片上最小单片机系统的原理图。

由于整套微控制系统均在FPGA内部实现,使其性能有了极大的提高,据相关资料显示,其最高工作频率可达200 MHz。

图2 基于8051软核的片上最小单片机系统

3.2 高精度延时系统的实现

实现定时控制主要有软件定时和硬件定时2种方案,软件延时计算不便、精度低且会占用CPU资源。硬件延时则可通过合理选择计数时钟源,实现高精度延时控制,且其延时值计算方便、不占用CPU资源。出于对本套系统技术指标的考虑,系统设计采用的是硬件延时方案,但使用该方案还需要解决2个问题:如何实现高频高精度时钟源;如何在既定的硬件条件下控制计数启动的触发误差。

要实现2.5 ns的延时精度,理论上需要400 MHz的时钟源信号,若按惯常利用晶振来提供基准时钟源的方法很难取得理想效果。在本设计中通过使用FPGA的内置锁相环倍频来解决这一问题,与直接使用外部的时钟相比,这种片内时钟几乎不受外界干扰,且精度优于晶振类时钟,适用于实现高精度延时。

如图3所示,计数器一般仅对时钟源的上升沿或下降沿敏感,当计数启动信号触发计数器开始计数时,由于触发信号出现的随机性,会导致计数器有一个计数周期左右的延时误差[10],且此误差难以避免。在本例400 MHz的计数时钟源下,大概会有2.5 ns的延时误差,而此延时完毕输出信号将用于触发LED光源,对系统而言也仅实现2.5 ns的控制精度。出于系统精度冗余度的考虑,在本设计中采用差分法进行计数延时,即用2路计数器分别对2路频率一致、相位相差180°的时钟信号进行计数,然后将2路计数器的输出结果相与,理论上可将触发误差控制在1/2个计数周期内[11]。其理论示意图如图4所示。用这一信号去触发光源便可将误差控制在1.25 ns以内。完全可满足2.5 ns的精度要求。

图3 计数误差成因示意图

图4 差分计数实现示意图

3.3 FPGA内高精度脉宽可调脉冲电路的实现

出于对高控制精度的考虑,在FPGA内部所设计的器件之间的触发均是边沿敏感的,所以当延时完毕时计数器输出的仅仅只是一个上升沿,然而有些待FPGA触发的外围器件却是电平敏感型的,且不同器件对触发信号的脉宽还有不同的要求。为解决这一问题,在本系统中设计了一个由D触发器、计数器构成的脉冲信号形成电路,且脉宽可调,调节精度取决于计数器的计数时钟源精度[12]。

如图5所示,CHUFA_IN为脉冲形成电路的触发信号,当计数延时完毕后由延时计数器产生,CLOCK_W_IN为计数器的计数时钟源信号,由锁相环给出,其精度决定了脉宽调节精度。PLUSE_WIDE为变换调节后的脉冲信号,其脉宽数值由计数器的计数值决定。

电路工作的过程:当没有触发信号作用时,D触发器处于稳态,其Q端为低电平,计数器的清零端aclr为高电平,使能端cnt_en为低电平,此时计数器停止计数工作,计数器输出端cout为低电平,D触发器的清零端CLRN为高电平;当有触发信号来临时,D触发器的输出Q变为高电平,计数器的计数使能端cnt_en变为高电平,计数器的清零端aclr为低电平,计数器开始对时钟源进行计数,当计数完毕时,计数器输出端变为高电平,D触发器清零端变为低电平,此时Q又重新变为低电平,电路返回稳态,并完成一次脉宽展宽工作,具体的展宽数值由计数器的计数值确定。

图5 高精度脉宽可调脉冲产生电路示意图

4 系统专用软件设计

基于FPGA的高精度动态光弹声光同步延时系统由硬件和软件2部分组成,其中硬件部分负责实现高精度的延时控制,软件部分负责计算每次声场图像采集的声光延时间隔,软硬件相互配合才能实现高精度的声场图像采集。在本设计中为系统编制了一套专用的上位机软件,软件具体的流程图如图6所示,图7为软件的主操作界面图。

图6 系统专用上位机软件流程图

图7 上位机软件操作主界面

5 系统测试结果

整套系统的测试平台由示波器、系统专用上位机软件和以FPGA为核心的声光同步延时模块搭建而成,测试平台的连接实物图如图8所示,通过上位机软件给声光同步延时计数器置不同的延时值,再配合双踪示波器观测超声激励信号与光源触发信号之间的时间间隔,并通过比对看两者是否相互应证。

图8 测试系统实物连接图

图9、图10、图11分别为软件置延时值为195、197.5、602.5 ns时示波器的实测值。

图9 理论置数195 ns时示波器实测值

图10 理论置数197.5 ns时示波器实测值

图11 理论置数602.5 ns时示波器实测值

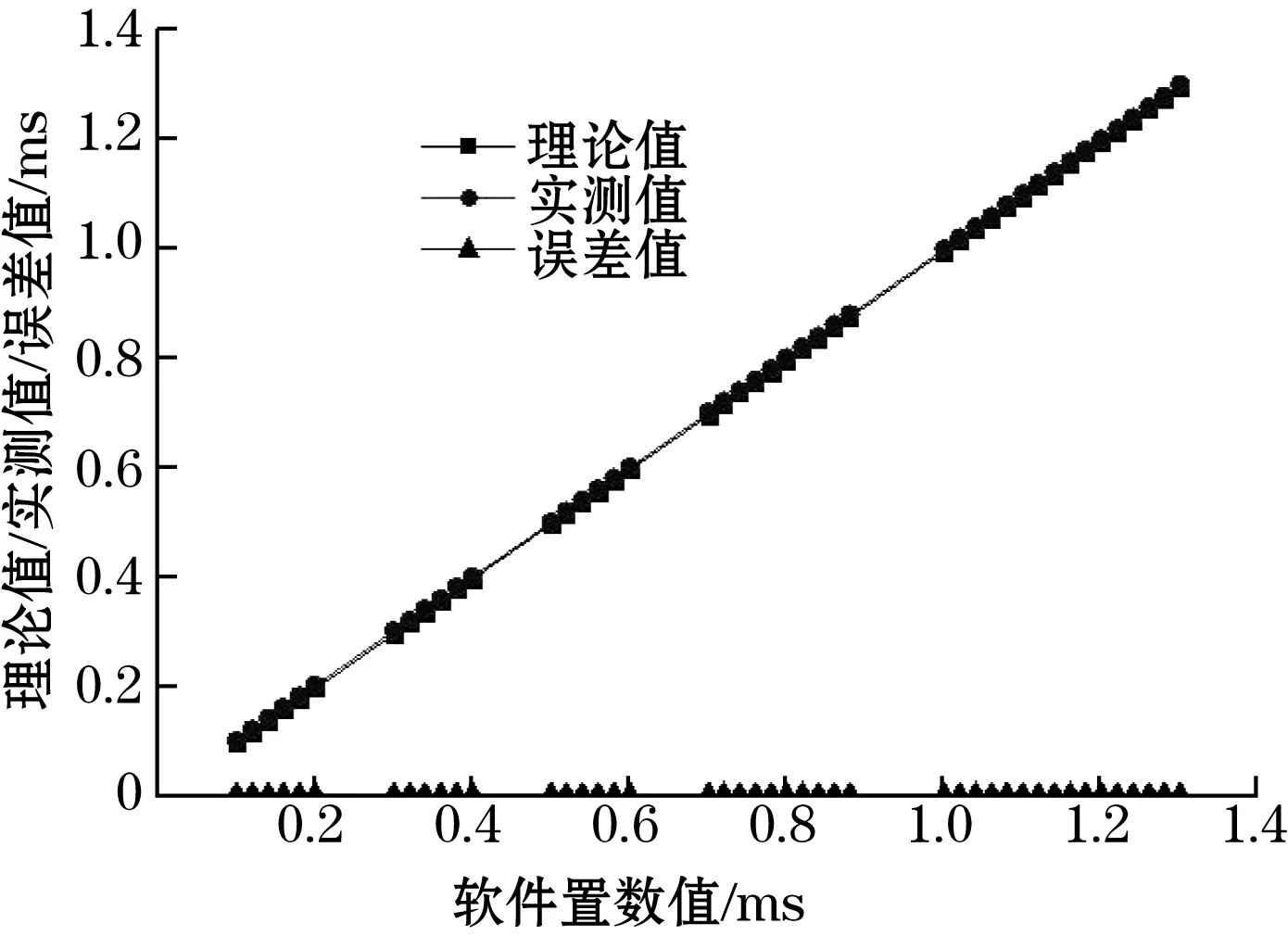

图12 理论值与系统实测值误差波动图

实测值分别为200、202、605 ns。为进一步探究软件所置延时值与系统实际延时值之间的对比关系,在以上实验的基础上还进行的大量的实际值与软件置数值验证,为便于观察,在此处将多组实验的结果绘制成误差比对图,如图12所示。综上,受器件固有延时、人手工读取延时数据以及示波器本身测试精度等因素影响,本系统实测值与理论值有5 ns左右的固定延时误差,经多次实验,该误差以5 ns为基准,上下浮动不超过1 ns,符合系统精度要求。

6 结束语

本文设计了一套基于FPGA的声场动态光弹观测仪声光同步延时系统,并提出了一种高精度、低成本的技术方案,且取得了良好的实验测试结果。整套系统运行稳定、集成度高、便携性好且成本低廉。可与专用光学系统配合实现声场图像高精度采集。其对高精度声场动态光弹技术的推广、检测声学的研究具有积极意义。