基于AD9852频率信号源设计

2019-07-04陆玉兵

陆玉兵

(中国电子科技集团公司第四十一研究所,安徽 蚌埠 233010)

一、引 言

AD9852是近年推出的高速芯片,其时钟频率为300MHz,并带有两个12位高速正交D/A转换器、两个48位可编程频率寄存器、两个14位可编程相位移位寄存器、12位幅度调制器和可编程的波形开关键功能,并有单路FSK和BPSK数据接口,易产生单路线性或非线性调频信号。当采用标准时钟源时,AD9852可产生高稳定的频率、相位、幅度可编程的正、余弦输出,可用作捷变频本地振荡器和各种波形产生器。AD9852提供了48位的频率分辨率,相位量化到14位,保证了极高频率分辨率,相位分辨率,极好的动态性能。其频率转换速度可达每秒100X106个频率点。在高速时钟产生器应用中,可采用外接300MHz时钟或外接低频时钟倍频两种方式,给电路板带来了极大的方便,同时也避免了采用高频时钟带来的问题。在AD9852芯片内部时钟输入端4至20倍可编程参考时钟锁相倍频电路,外部只需输入低频参考时钟60MHZ,通过AD9852芯片内部的倍频即可获得300MHz内部时钟。

二、频率合成器整体设计原理

信号源整体设计的原理框图如图1所示,锁相环(PLL)由输入参考频率、鉴频鉴相器、低通滤波器、压控振荡器、分频器、数字频率合成器、微控制器及存储器构成,是整个信号源设计的关键部分,其设计的好坏直接影响了输出信号的指标,鉴频鉴相器将参考频率信号与DDS输出的频率信号进行鉴频鉴相,输出相位固定的信号经低通滤波器滤除高频分量去控制压控振荡器,使压控振荡器的输出锁定在设计的频率上,在这里DDS采用微控制器对其进行串行接口控制,DDS所需的频率控制字及环路参考电压存储在EEPROM里,存储器与微控制器采用SPI总线进行通信,VCO输出信号经功率放大器进行放大。

图1 信号源设计原理框图

(一)低通滤波器(LPF)设计

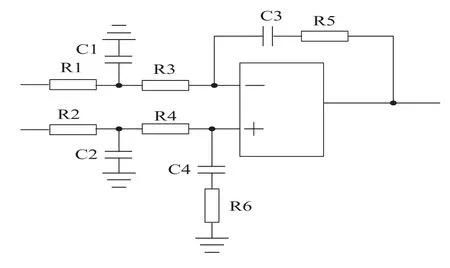

本文锁相环设计基于鉴频鉴相器HMC439,其两路输出分别为正脉冲与负脉冲,再加之VCO调谐电压较高,故采用有源差分环路滤波器。环路滤波器设计是锁相环设计中影响整体性能的关键环节,其阶数、环路带宽与相位裕度是重要参数,为使系统稳定,一般要求环路相位裕度达到45度以上,常用有源环路滤波器的结构上下对称,本文采用三阶有源滤波器的设计,在前端增加了一组RC低通滤波器,可以减少不适合作为运算放大器输入的高频信号,有利于防止混入噪声,增加对杂散的抑制,其电路图如图2所示。其中R1=R2=R3=R4,R5=R6,C1=C2,C3=C4。

图2 三阶有源环路滤波器

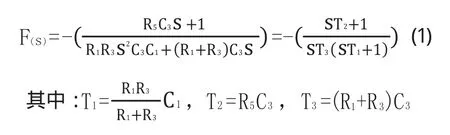

计算得到三阶有源环路滤波器的传递函数为:

将式(1)代入锁相环可计算开环增益为:

由式(2)可得出开环增益的相位裕度,令其为Φ(s)。开环增益幅值在环路带宽ωc处满足|G(s)|s= jωc= 1,相位裕度在环路带宽ωc处倒数为0,即Φ(s)′s = jωc= 0,且Φ(s)在s=jωc处应是45度以上的值,联立对应关系式可计算出滤波器中各时间常数与各元器件值,该计算过程较复杂,这里只给出了求解方法,一般我们在设计滤波器时不会进行如此的计算,而是使用滤波器仿真工具进行仿真运算,一些PLL IC供应商也会提供相应的软件给用户使用,如ADI的ADIsimPLL、安捷伦公司的ADS工具,这样大大节省了设计时间,并为我们设计滤波器时指明了方向。

(二)数字频率合成器(DDS)控制电路设计

DDS采用ADI公司的AD9852芯片,内置高达300MHz的内部时钟,2个48位的可编程频率字寄存器,具有10MHz两线或三线SPI兼容串行或100MHz并行8位编程接口,能工作在单音、FSK、斜升FSK、Chirp、BPSK五种工作模式,根据设计要求本AD9852工作在FSK双频点模式,频率切换速率为100kHz,采用三线SPI串行通信,AD9852控制电路原理框图如图3所示。

图3 DDS控制电路原理框图

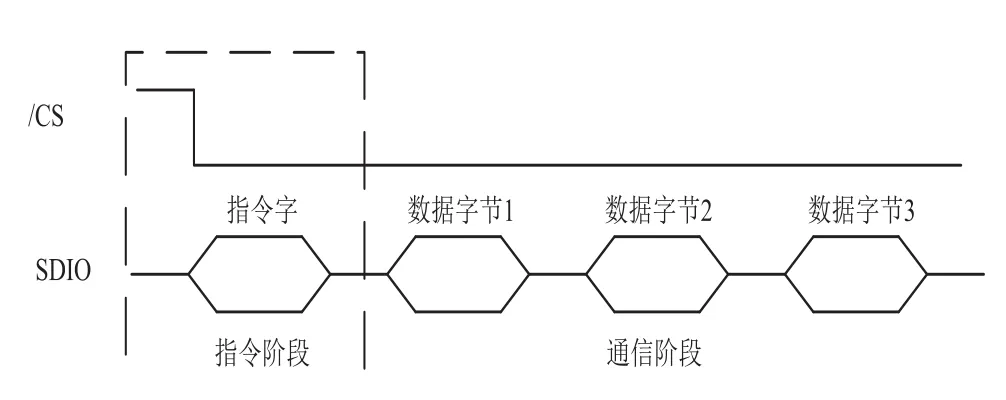

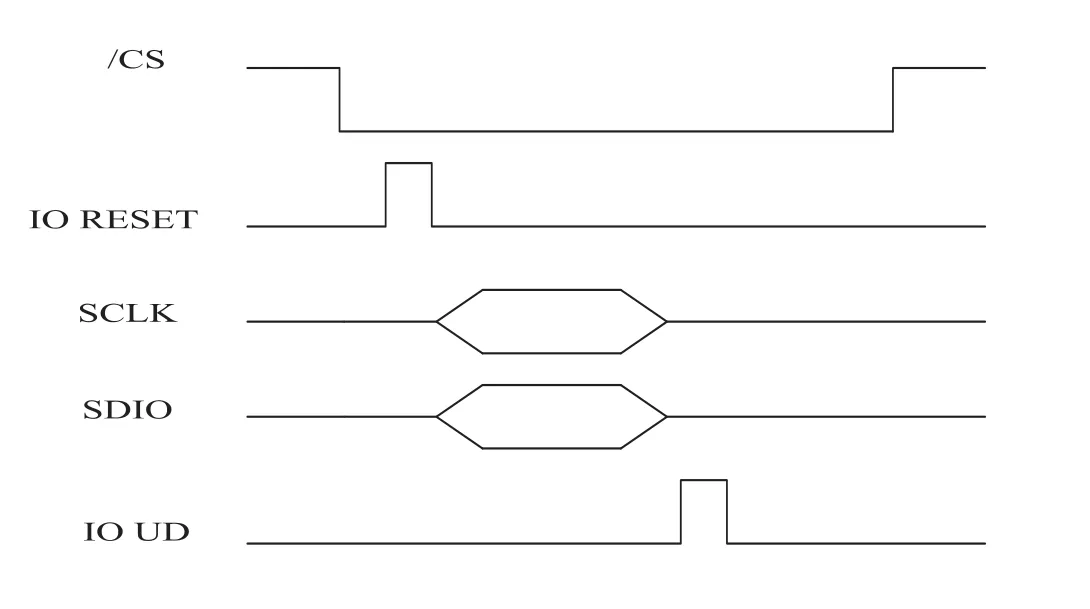

参考时钟(F1)来自VCO经32分频的信号提供,为了提高抗干扰性,参考时钟采用差分时钟模式供给,最终频率输出信号(Fout)供给鉴频鉴相器。AD9852的串口与大多数同步传输格式串口兼容(包括Motorola 6905/11 SPI及Intel 8051 SSR协议),将其设为单引脚I/O(SDIO),即输入/输出信号共用一根线,通信周期如图4所示。

图4 采用SDIO作为输入输出线的通信周期

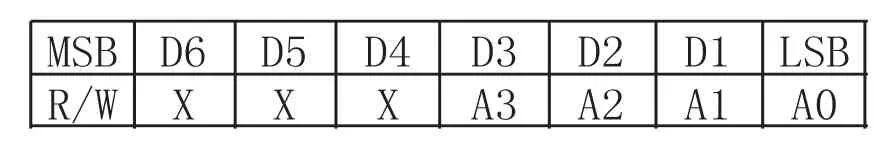

AD9852的串行通信周期分为指令阶段和通信阶段。指令阶段对应于系统时钟的前8个上升沿,对应的指令字包含以下信息:

?

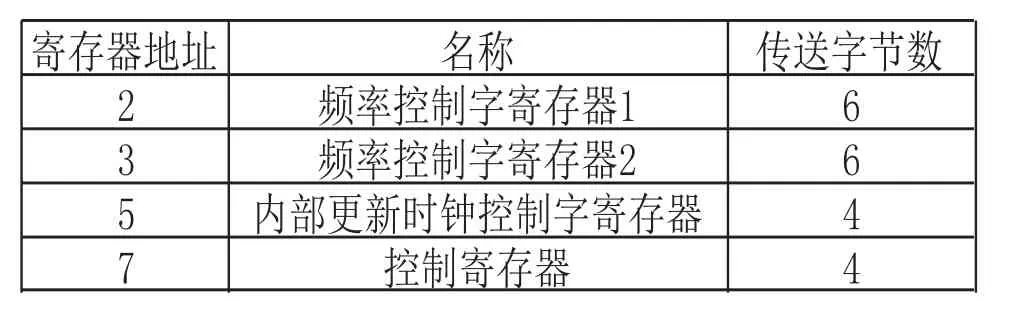

R/W位决定了指令字后的操作是读出或是写入,高电平为读出,低电平为写入,6、5、4位与操作无关,低4位指示了操作串行寄存器地址。串行寄存器的地址信息同时包含了与该指令字所在指令阶段对应的通信阶段的传送字节数。表1列出了部分串行寄存器地址以及与之对应的传送的字节数。

表1 寄存器地址对应的传送字节数

当完成了通信周期后,AD9852的串口控制器认为接下来的8个系统时钟的上升沿对应的是下一个通信周期的指令字,当IORESET引脚出现一个高电平,将会终止当前的通信周期,当引脚状态回到低电平,串口控制器认为接下来的8个系统时钟的上升沿对应的是下一个通信周期的指令字,这点对保持通信的同步十分有益。所有输入AD9852的数据在时钟的上升沿写入,在下降沿读出,首先将写入的数据保存到缓冲器,只有外部更新信号来时这些数据才会被写入相应的寄存器,这时才能按要求完成相应的功能。本设计中微控制器选用PIC单片机,通过对其通用的IO口编程,实现对AD9852的串行控制,其通信时序如图5所示。

图5 串行通信时序

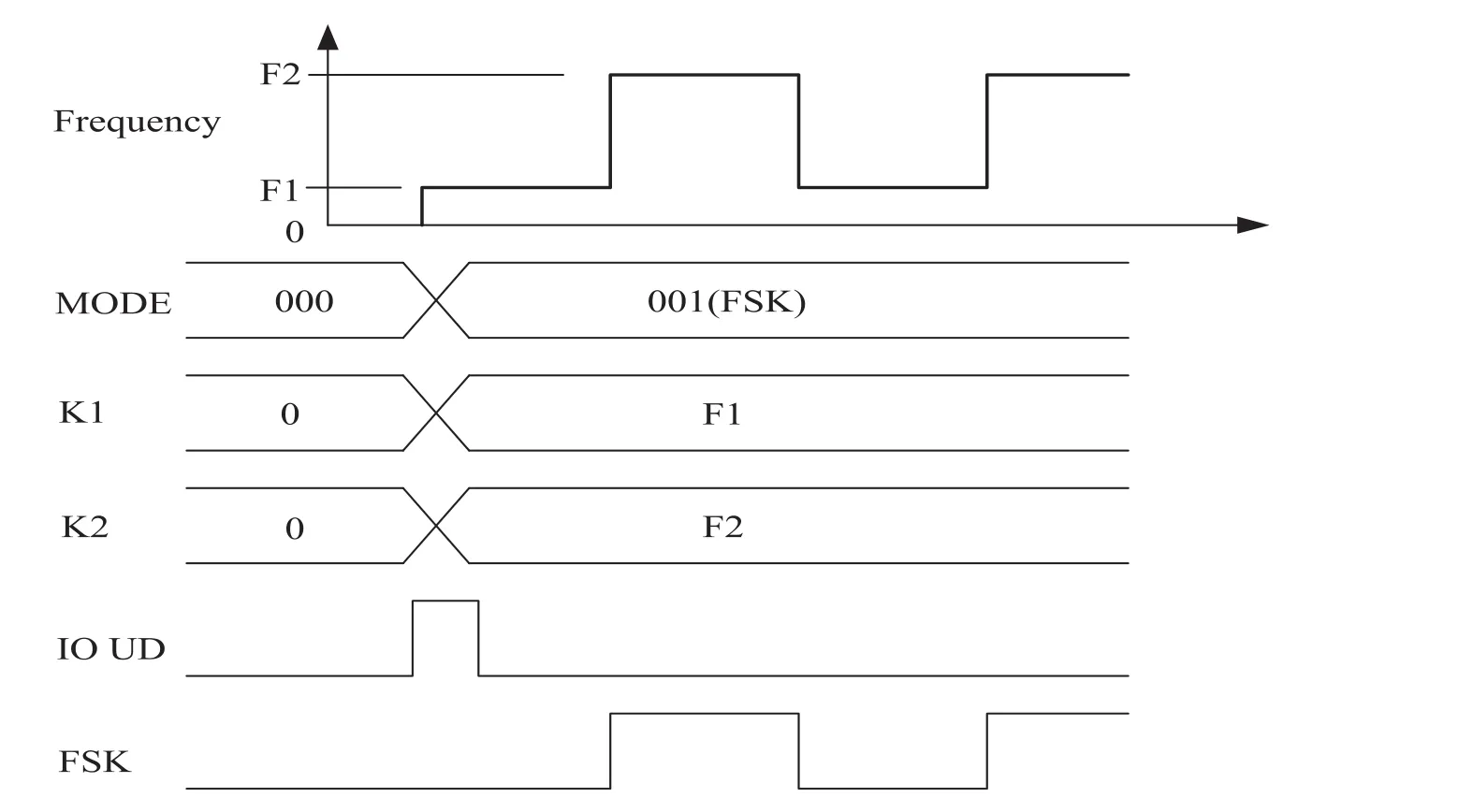

AD9852在FSK模式下控制的时序图如图6所示,从图中可以看出在频率切换信号的高低电平对应高低频率控制字,从而按顺序以切换频率信号的速率输出高低频率信号F1和F2。

图6 FSK模式控制时序图

按照上述方法设计的频率信号源输出波形如图7所示:

图7 频率信号源波形

三、结语

本文介绍了一种基于AD9852频率信号源设计方法,从实验可以看出,AD9852频率合成器设计方法提高了系统控制的稳定性和可靠性,降低了成本。