一种近阈值电压标准单元特征化建库方法

2019-06-08胡伟安文婷袁甲

胡伟 安文婷 袁甲

摘 要:面向近阈值电压下库单元的实际使用情况,针对传统库文件查找表误差较大的问题,提出了一种近阈值电压下对标准单元的特征化建库方法.通过对标准单元实际应用情况的分析,重新界定了查找表的边界;通过分析电路综合结果与电路仿真结果的相对误差,重新确定了查找表的规模;从而提高了近阈值电压下标准单元库准确性.该方法对smic55nmCMOS工艺的库文件在0.6 V电压下特征化建库,并进行误差评估,结果表明,该方法相较于传统方法建立的库文件,准确性提高了16%~63.51%,减小了查找表误差,有效提高了库文件的准确性.

关键词:近阈值;标准单元库;查找表;库文件

中图分类号: TN492 文献标志码:A

A Characterization Method for Standard Cell Library

at Near-Threshold Voltage

HU Wei1,AN Wenting1,YUAN Jia2

(1. College of Physics and Microelectronics Science,Hunan University,Changsha 410082 ,China;

2. Institute of Microelectronics,Chinese Academy of Sciences,Beijing 100029,China)

Abstract:According to the actual application of a standard library cell operating in the near-threshold voltage region,and due to the problem of large error in the lookup table of traditional library files,this paper proposed a method to characterize the standard cell in near-threshold voltage region. The method redefined the boundary of the lookup table by analyzing the actual application of standard cell in near-threshold voltage,and by analyzing the relative error between the circuit synthesis result and circuit simulation result,it re-determined the scale of the lookup table,in order to improve the accuracy of standard cell library in near-threshold voltage region. This method was then used to characterize the smic55nmCMOS process library file in 0.6 V voltage and evaluate the relative error,and the results show that when compared with the library file established by traditional characterize method,the proposed method improved the library file's accuracy by 16%~63.51%,reduced the error of lookup table,and effectively improved the accuracy of library file.

Key words:near-threshold;standard cell library;look-up table;liberty file

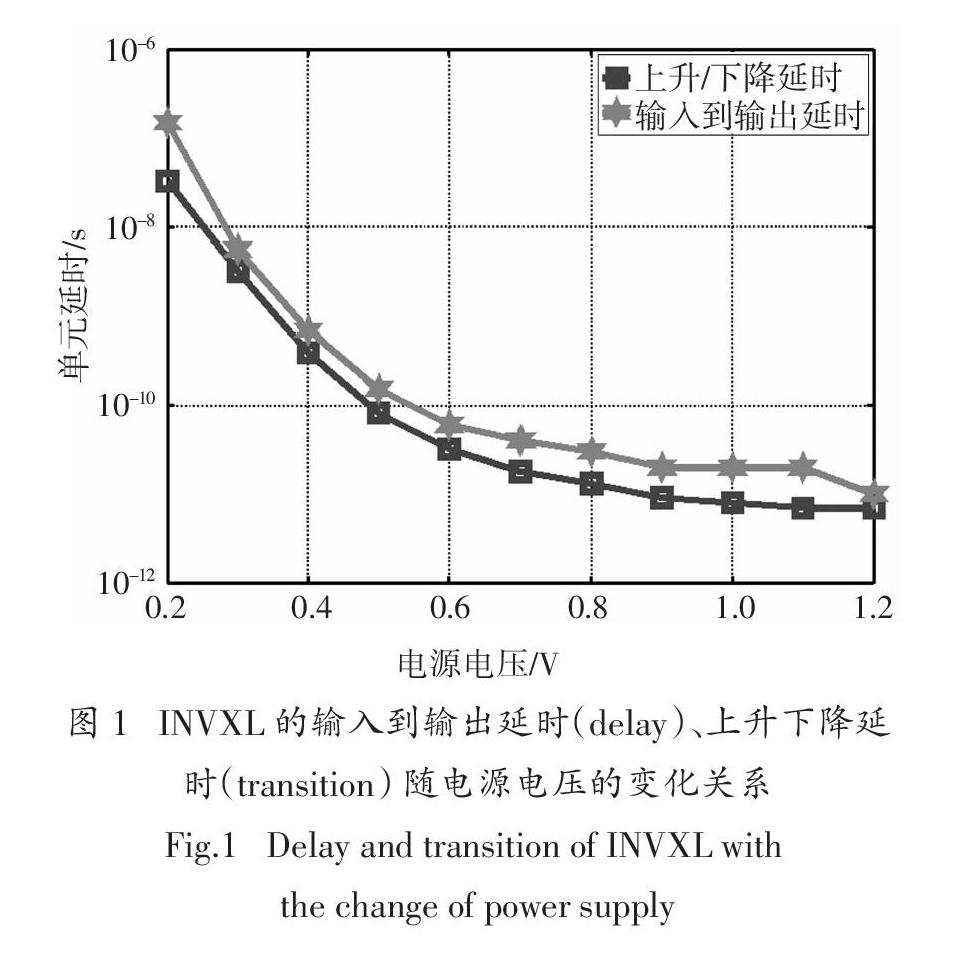

近些年,無线传感节点、医疗电子、 RFID极低功耗(纳瓦级功耗)技术逐渐兴起,具有广阔的市场前景[1],然而常规的低电压(0.8~1.2 V)技术,不能达到这些极低功耗设备的功耗指标要求,需要进一步降低电路的供电电压,即电路工作在近阈值(0.5~0.6 V)附近.近阈值技术是数字电路近阈值电压实现的关键,是实现系统极低功耗的必然途径.然而近阈值电压下,标准单元的输入到输出延时、上升下降延时呈指数值变大,给近阈值数字电路设计带来严峻挑战.在近阈值数字电路设计流程中,标准单元库把设计实现的硬件语言翻译成门级网表,是电路逻辑综合的基础,而库信息的准确性决定了时序分析的准确程度,是数字电路功能正确的保证.然而对近阈值标准单元,用传统特征化方法建立的标准单元库信息与hspice仿真结果误差极大,无法通过库信息来准确把握整个电路设计.

为支持近阈值数字电路的设计流程,本文提出了一种近阈值电压下标准单元的特征化方法:通过对库单元实际使用时可能的负载与上升下降延时情况的分析,确定标准单元库查找表的边界;用相对误差统计的方法,确定标准单元库查找表规模;从而得到与正常电压下商用标准单元库精度相当的近阈值电压下标准单元库.

本文首先分析了商用标准单元库的非线性模型及不同电压下标准单元的延时变化情况,确定了提高库信息准确性的改进方法,并采用该方法对0.6 V smic55nmCMOS工艺的标准单元进行特征化建库;最后采用反相器链路、ISCAS'85基准测试电路C17、ISCAS'89基准测试电路S27,分别进行hspice仿真和基于所建库文件进行DC综合,验证该标准单元特征化方法的建库准确性.