硅基光波导开关技术综述*

2019-06-04涂鑫陈震旻付红岩

涂鑫 陈震旻 付红岩

(清华大学,清华-伯克利深圳学院,深圳 518055)

1 引 言

近年来,互联网通信数据容量每年以50%—60%的速度迅速增长,人们对带宽的需求越来越大.运营商在电信长途骨干网和城域网建设中遇到了电交换的瓶颈:电交换设备单机容量达到上限;5G网络的回传时延指标对交换节点的性能提出了更严格的要求;网络节点的电交换设备功耗高达万瓦,耗电量接近了许可极限,耗电量的80%源自光电/电光转换和电交换开关.因此光交换技术的优势日益凸显,基于波长选择开关(wavelengthselective switch,WSS)和自由空间微电子机械系统(micro-electromechanical system,MEMS)的光开关技术已被部署用于关键网络节点的可重构光分插复用(reconfigurable optical add-drop multiplexer,ROADM)设备中,实现了波长和端口通道毫秒量级的数据链路切换时间[1-3].

在短距数据中心网络中,经常需要根据动态需求进行网络重构.目前,数据中心网络中的重配置主要是由高速电交换开关来完成:输入光信号被转换成电信号,在电域完成交换之后再被转换回光信号输出.尽管电学信号的放大、整形和同步技术成熟,但是光/电/光(O/E/O)转换通常需要光收发器,即用于光/电转换的接收机和用于电/光转换的发射机,这给交换系统带来极大的转换功耗.同时,由于电交换与光波分复用技术(wavelength division multiplexing,WDM)不兼容,每条光链路都要通过复用器、解复用器以及多路O/E/O的转换,这就增加了交换节点的数据链路重构的复杂性和硬件成本.光交换与电交换相比,无需进行O/E/O转换,且对数据比特率、信号格式和协议是透明的,具有更低的功耗和硬件成本优势.虽然光开关的速度(从纳秒到毫秒取决于不同技术方案)仍然比电开关的速度慢(亚纳秒),但是它可以处理通信中缓慢变化的数据部分(例如数据流和长分组数据包),同时指定电交换来处理通信中的突发数据部分(例如短分组数据包),并各自发挥自身优势,有望成为未来数据中心网络最具潜力的交换技术[4].

此外,随着云计算的出现、物联网的发展以及人工智能的兴起,具有高带宽和大数据传输容量的动态数据交换技术将广泛地用于高性能的数据密集型计算中,服务于健康信息学、网络安全、市场营销、金融和国防等领域[5].这类应用场景要求开关芯片可实时处理大量具有随机性和探索性的数据,实现对频繁的短消息纳秒量级的快速交换.然而在过去二十年内,集成电路芯片中的带宽快速增长受到了管脚密度和金属引线等电子瓶颈.芯片功耗正以每三年翻倍的速率增长,并持续趋近电子器件的功耗所能够承受的温度极限,大部分能耗集中在主板的电信号传输线和O/E/O转换过程.因此,采用新的微处理器架构和光交换技术有望显著改善片上互连的带宽和时延特性.未来百亿亿次浮点运算要求功耗降低到pJ/b量级,成本控制在¢/Gb/s量级[6],采用传统的电信号交换技术将无法满足,光信号交换将为解决该通信需求提供新的途径与方案.

由此可见,无论是数千公里的电信网络交换还是几厘米的计算机核间并行计算,都需要光开关技术来实现特定数据流配置的业务模式.近些年几种典型的光开关被广泛地研究,包括MEMS[7]、硅上液晶(liquid crystal on silicon,LCOS)[8]、铌酸锂波导[9]、III-V族半导体光放大器[10]、马赫-曾德尔干涉仪(Mach-Zehnder interferometer,MZI)[11]和微环谐振器(micro-ring resonator,MRR)[12].与铌酸锂、III-V族平面波导回路芯片和MEMS平台相比,基于绝缘衬底上的硅(silicon-on-insulator,SOI)平台的硅基光电集成芯片具有以下优势:1)体积只有传统二氧化硅器件的1/1000,器件密度高;2)能够与III-V族有源光器件和互补金属氧化物半导体(complementary metal oxide semiconductor,CMOS)电路实现单片集成;3)加工工艺与先进微电子技术共享成熟的CMOS技术制造平台,波导侧壁粗糙度可控制在纳米量级以内;4)可以采用12英寸SOI晶圆量产,器件成本可降低到IIIV族器件的1/3以下[13];5)热光效应和等离子体色散等非线性效应强,驱动功耗低;6)硅材料在通信波段透明且响应速率快,极高带宽、超快传输与调制速率;7)与电子器件相比,硅光器件采用近红外光信号传输数据,不受电磁波干扰,具有高抗干扰性和高可靠性.此外,与传统的基于单一工艺和单一材料的光学器件相比,硅基光电集成芯片的材料与工艺的多元化特点决定了它的丰富功能,不仅实现了光开关集成回路(包括波导、相移器、探测器和模斑耦合器等),还实现了电子集成回路(晶体管和电容、放大电路等),从而节约了单个元器件的封装成本.

本文首先回顾近年来硅基光波导开关的发展现状,对不同原理和结构的硅基光波导开关的特点进行分析和总结,包括MZI型、MRR型和MEMS驱动波导型.随后介绍自己最新的研究成果,分析影响开关矩阵性能的关键技术.最后,对硅基光波导开关技术研究的技术挑战进行分析,并提出了硅基光波导开关技术未来的潜在研究方向.

2 硅基光波导开关引擎

2.1 MZI型

MZI型光开关单元是最简单的大宽带干涉型开关引擎.由于其不受信道间隔和网格配置的限制,非常适用于WDM系统中的多波长复用光链路的空间端口切换场景.典型的MZI型2×2光开关单元如图1(a)所示,由两个50:50的分束器和两个长度相同的波导组成,并在其中一臂上制作电极,利用硅的热光效应或者注入载流子产生的等离子色散效应,改变一臂的波导折射率,形成相移器.当两臂光信号的相位差达到0或 π,输出端口的光信号发生相干相长或相干相消,实现光信号切换.热光波导开关可以实现亚微秒至毫秒量级的端口切换,适用于大型数据中心间互联(Data Center Interconnection,DCI).由于硅在室温下具有较高的热光系数=1.86×10¯4/K[14],因此硅波导热光开关比二氧化硅热光开关具有更高的效率.热光相移器的相移 Δφ可以表示为

图1 (a)MZI型2×2光开关单元结构示意图.硅基波导开关相移器的横截面图(b)金属薄膜热电极热光相移器;(c)掺杂波导热光相移器;(d)空气隔离层的热光相移器;(e)注入载流子型电光相移器Fig.1.(a)Schematic of 2×2 MZI switch cell.Cross-sections of waveguide phase shifters:(b)Thermo-optic phase shifter using a metal heater;(c)thermo-optic phase shifter using a doped resistive heater;(d)suspended thermo-optic phase shifter using a metal heater (e)carrier injection phase shifter.

其中λ是波长,ΔT是相移器上热调谐的温度改变量,L是相移器的长度.热电极通常有两种结构[15],一种是位于硅波导上方的金属薄膜热电极(TiN,Pt,W等),如图1(b)所示.注入的电流产生的焦耳热通过波导的包覆层二氧化硅传递给硅波导,并改变其温度和折射率.这种金属薄膜热电极的热效率受到包覆层热导率和热电极与波导的间距的限制,开关功耗通常在毫瓦量级.另一种是在脊型波导的中心进行轻掺杂,两侧部分刻蚀平台区重掺杂,形成欧姆接触电阻,如图1(c)所示.这种热电极,由于直接与硅波导的光信号模场中心重合,具备更快的时间响应特性和更高的热效率,但掺杂材料对光信号会产生吸收,因此损耗更高.由于硅光集成芯片能耗大部分来自于热光相移器,降低热调谐功耗能够提升器件密度,一种有效的手段是在热电极附近通过各向同性硅刻蚀工艺引入空气隔离槽,如图1(d)所示,使加热的波导臂悬空,降低硅波导向四周的热耗散.然而,空气隔离槽提升加热效率的同时延长了热光相移器的时间响应常数.因此需要器件结构优化设计,获得开关时间与功耗之间的平衡.与热光波导开关不同的是,电光型波导开关可以实现纳秒量级的端口切换,适用于数据中心内网络(Data Center Network,DCN)交换和微处理器片上的互连.注入载流子型相移器是正向偏置的PIN结二极管,如图1(e)所示.根据等离子色散效应[16,17],硅的折射率变化可以写成

其中 ΔN和 ΔP是电子和空穴的载流子浓度变化量.同时,载流子浓度的改变也影响硅的吸收系数,即

其中 Δα是系数的改变量,由(2)式和(3)式可以看出,当 ΔN和 ΔP增大(即正向偏置)时硅波导的折射率会降低,同时注入的载流子引起吸收系数的增大,导致光功率的损耗变大,从而MZI的两臂光信号损耗不相同,引起串扰的恶化.另一方面,由于硅的热光效应,正向偏置产生的热效应会增加硅波导的折射率,与注入载流子引起的折射率变化趋势相反,因此降低调制效率.为了改善此问题,人们提出采用推拉的双臂驱动设计[18,19]:即将两臂的初始相位差设置成 π/2,在两臂上分别通过注入载流子的方式产生附加的 ±π/2 的相位差,从而实现光信号端口切换所需的0或 π 的相位差.与传统的单臂驱动设计相比,双臂驱动的两臂上施加的驱动电流更小,引入的损耗和串扰更低.此外,PIN结二极管还常与热光相移器集成,用于补偿工艺容差带来的相位差,而不引入额外的损耗.

表1中列举了典型的MZI光开关研究现状.为了降低功耗,Fang等[20]采用隔离槽技术使得热光开关的功耗分别降低至0.5 mW,开关速度达到0.3 ms;Dong等[21]采用4 mm长的螺旋波导相移器有效降低了偏置电流,注入载流子开关功耗仅0.6 mW;Lu等[22]采用折叠波导相移器增加了热电极与波导的接触长度,热光开关功率低值50 μW.为了扩大光学带宽,Watts等[23]和Chen等[24]分别提出绝热耦合器和弯曲耦合器,使光学带宽超过100 nm.为了降低串扰,Suzuki等[25]提出采用可调谐3 dB耦合器去动态弥补另一个3 dB耦合器的加工误差,从而获得—50 dB的超低串扰;Dupuis等[26]报道了一种一臂内嵌MZI相移器,另一臂集成可调衰减器的光开关,这种结构通过内嵌MZI和可调衰减器的损耗平衡,在保持两臂损耗相同的前提下实现相位从0到 π 的调谐,从而实现了—34.5 dB的串扰.在我们最新的工作中[26],在IME的220 nm×500 nm SOI硅波导的平台上,采用标准的TiN热电极相移器,通过对多次折叠波导和空气隔离槽结构的优化,实现了两种情况下的热光硅波导开关单元:1)引入空气隔离槽层:开关时间1.34 ms,开关功耗0.5 mW;2)无空气隔离槽层:开关时间70 μs,开关功耗10 mW.

2.2 MRR型

与MZI型光开关不同,MRR型光开关单元是具有波长选择性的谐振型开关引擎[28],其谐振波长与谐振腔的尺寸关系如下:

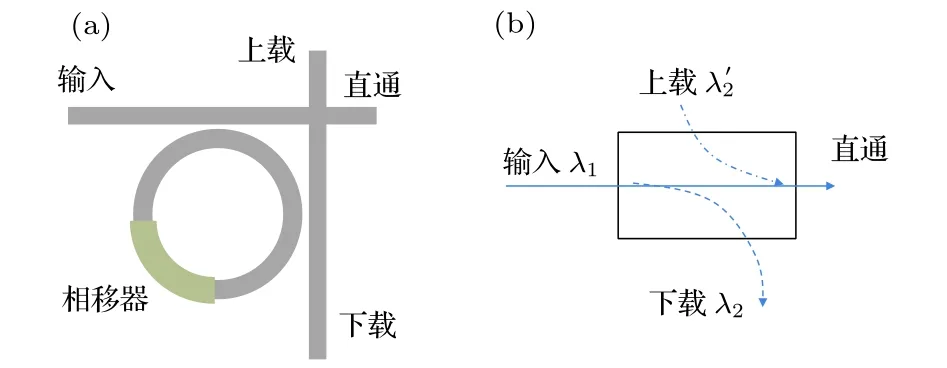

其中R是谐振器半径,neff是模式的有效折射率,m是模式的阶数,λ是谐振波长.由于谐振特性可以增强相位,它具有更低的功耗和更小的体积,受到大家的关注.典型的MRR型2×2光开关单元如图2(a)所示,由输入—直通波导、上载—下载波导和可调谐的微环组成.当WDM系统中的信道间隔和网格配置与微环谐振器的自由光谱程相和谐振频率适配时,波长交换可以通过热光效应或者等离子体色散的电光效应调谐MRR的相移器进行实现.如图2(b)所示,当输入光信号的波长λ2落入微环的谐振波长时,可以从下载端口输出;同时非谐振光信号波长λ1和上载端口输入的相同波长λ2’的光信号从直通端口输出,实现波长交换.尽管微环谐振器型光开关功耗低、体积小,但是实际应用中需要克服两个主要技术障碍:第一,单个微环的滤波谱线呈现洛伦兹线性,限制了光信号带宽和信道间串扰;第二,微环的谐振波长对芯片环境和加工误差非常敏感,实时锁定谐振波长,不受温度和激光器波长漂移是实际应用的关键保障.表2总结了近年来MRR型光开关单元的代表成果.为了增大带宽,级联微环的结构常常用来整形滤波谱线,实现近似矩形的两边陡直中间平顶的滤波窗口[29-33]和宽带无中断的调谐[34].近期,Lu等[35]提出了一种MRR与MZI相结合的结构,上臂耦合的MRR工作在波长λ1,下臂耦合的MRR工作在波长λ2.当调谐其中一个MRR的波长到(λ1+λ2)/2时,两臂产生π的相位差,开关状态发生改变.这种结构结合了MRR的共振增强和MZI的双光束干涉原理,具有更小的功耗.常用的稳定谐振波长方法包括被动型和主动型两类.被动型采用负热光系数的材料(例如聚合物[36,37],TiO2[38,39])与硅波导相结合,降低材料对环境温度的热敏感性.主动型则是将硅基波导上各种形式的光探测器与反馈算法相结合,实施调节微环的谐振波长以确保开关输出光强最大[40,41].随着片上光系统的扩容和模分复用的广泛研究,基于MRR的模式光开关技术也被提出,采用多模波导和模式转换实现不同阶数的模式之间的交换,进一步增加了片上光交换系统的容量[42-44].

表1 业界MZI型硅基波导光开关的代表成果Table 1.Comparison table of MZI optical waveguide switch cells.

图2 (a)MZI型光开关单元结构图示意图;(b)波长开关路径Fig.2.(a)Schematic of a MRR switch cell;(b)switching paths.

2.3 MEMS驱动波导型

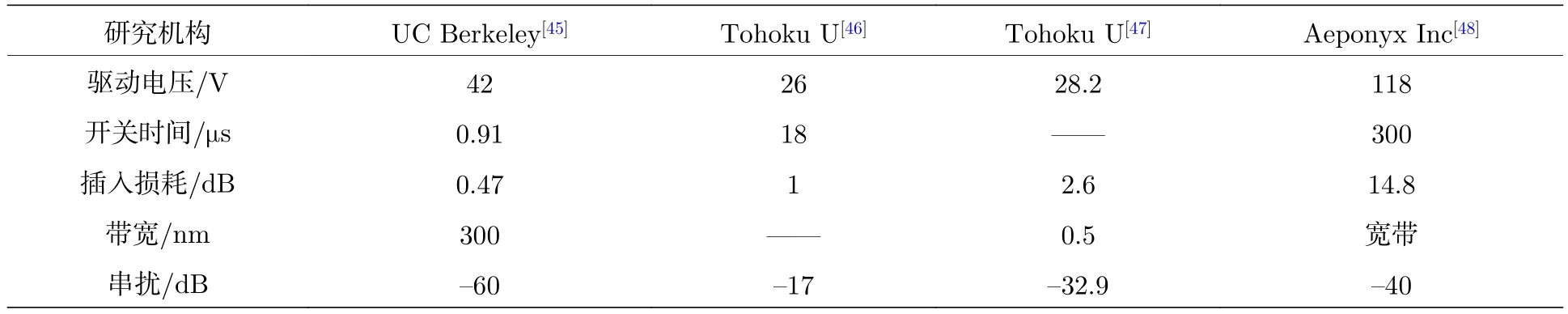

无论是MZI型还是MRR型光开关,都是基于光波导中光强的干涉与谐振原理实现信号传播路径改变,因此相位对工艺容差和环境的敏感性限制了单级开关的串扰和损耗,从而影响开关矩阵的规模.近期,一类新型的基于硅光子平台的静电MEMS驱动波导型光开关被广泛研究,相关代表成果如表3所示.Seok等[45]提出的在双层硅光子平台中的垂直波导绝热耦合器,通过静电调节两层波导形成的平行平板驱动器之间的垂直间隙来切换光信号.由于光信号总是在底层波导中传播,除非需要切换到其他路径,因此光信号重定向的功能与光开关节点处的直通传输的功能解耦,损耗和串扰不会在交换结构中积累.此外,上层波导和底层之间添加的止动部件实现了数字型驱动,简化了控制并实现了相当低的光学串扰.该器件在42 V的驱动电压下具有0.91 μs的切换时间和超过300 nm的带宽和—60dB的串扰.Abe等[46]和Takahashi等[47]采用水平梳齿驱动器实现了驱动电压更低、微秒量级切换速度的可动方向耦合器[46]与微环谐振器[47],是一种新型低串扰的波长选择性光开关.近期,Briere等[48]在硅基旋转型梳齿驱动器平台上集成低传输损耗的氮化硅波导,通过端面耦合实现了低于—40 dB串扰的1×N光开关.由于该器件采用端面对接耦合,具有超宽带的特性.然而缺点是由于可移动部件的质量很大,响应时间较慢(约300 μs),而且驱动电压高达约118 V.

表2 业界MRR型开关的代表成果Table 2.Comparison table of MRR optical waveguide switch cells.

表3 业界MEMS驱动波导型开关的代表成果Table 3.Comparison table of MEMS optical waveguide switch cells.

3 硅基光波导开关矩阵

在过去的几年中,硅基光电子集成技术得到了迅猛发展.随着CMOS工艺和晶圆技术的不断提升,在一块芯片上类似于电子集成电路那样单片集成数千个光子器件单元的愿景逐渐变成现实.不少研究机构和电信设备公司在硅基光电子集成平台上对大规模的硅基波导光开关矩阵进行了广泛的实用化研究.本节总结了业界大规模硅基光波导开关矩阵的代表成果,主要是基于上述三种光开关引擎的扩展应用.

3.1 MZI型开关矩阵

2011年至2015年期间,两种基于MZI技术的8×8硅波导光开关被Nakamura等[49,50]提出.它们作为转发聚合器(transponder aggregator)中的波长上传/下载开关矩阵,在城域网ROADM交换节点中具有无色、无方向和无冲突(colorless,directionless,contentionless,CDC)的功能.两种开关矩阵均采用1.5 μm厚的脊型硅波导层的SOI平台,通过热光调谐不仅实现了微秒级切换速度且偏振无关的开关特性,还使芯片与光纤之间的耦合变得更简单.2012年,Chen和Chen[51]报道了一种基于MZI的8×8硅波导光开关,这是首次在220 nm薄硅波导层SOI平台上实现的光开关矩阵,验证了高密度的光开关单元、交叉波导和脊型波导转化器等无源器件的集成.开关矩阵总面积为8 mm×8 mm,采用空气隔离槽提高热光相移器调谐效率,整块芯片的驱动功耗只有0.07 W,同时通过switch-&-select拓扑架构实现了片上最低损耗为4 dB,任意两个端口之间的串扰低于—30 dB.2014年,Dupuis等[52]和Lee等[53]分别报道了基于MZI型的4×4[52]和8×8[53]电光开关矩阵与数字型CMOS逻辑驱动电路的集成方案.这是第一个在90 nm硅光子集成工艺平台上实现光子芯片与CMOS逻辑驱动芯片单片集成的成果报道.驱动芯片包括标准逻辑单元,形成串行—并行接口,用于寻址连接到基于逆变器的驱动器的每个开关单元,并直接驱动开关电极.光子芯片包括电光相移器、热光补偿器和交叉波导等无源器件.8×8芯片总面积为0.675 mm2,开关时间为5 ns,总驱动功率小于50 mW.2015年,32×32的热光硅基波导光开关矩阵被Tanizawa等[54]第一次报道.此开关芯片是在45 nm CMOS工艺线上采用12寸SOI晶圆完成加工,芯片之间保持良好的一致性.开关矩阵总共包含1024个开关单元和961个方向耦合器型波导交叉,各条光路损耗具有良好的一致性.通过LGA转接板实现倒装焊电封装,芯片的总面积仅为11 mm×25 mm,是传统32×32 PLC芯片的1/46.芯片通过FPGA控制热光相移器,采用脉冲宽度调制驱动方式,开关时间为30 μs.2016年,Lu等[55]报道了MZI型16×16 Benes架构的电光开关,可以通过热光调谐补偿工艺容差和环境变化带来的相位差.随后,目前业界端口数最多的MZI型32×32的电光开关矩阵[56]和64×64的热光开关矩阵芯片[57]被Qiao等报道.他们通过优化算法,在矩阵的中间级设置数目尽可能少的片上光电监控器,用于优化开关路径和驱动状态,并在电光开关中采用推拉的双臂驱动设计来将片上损耗降低到18.5 dB,串扰为—15 dB.

近期,我们报道了基于优化的Hybrid Dilated Benes拓扑架构的32×32热光开关[58].采用这种独创的新型拓扑架构,相同规模的光开关矩阵所需开光单元更少并获得更低的串扰.光开关芯片采用IME的8英寸晶圆工艺平台进行加工,总面积为12 mm×12 mm,包含 448个热光开关单元,1856个波导交叉,864个片上光电二极管监视器和68个模斑转换器.热光相移器和光电二极管通过FPGA和模数转换DAC驱动控制,用于开关单元的自动初始化和驱动电流的实时校准,以此保持最低的串扰.芯片的电学封装采用金属引线键合方式实现1560个焊盘与CBGA陶瓷基座的连接,并且通过CuW衬底和TEC进行散热控制;光学封装采用68芯保偏光纤,通过PLC连接器与硅光子芯片对接耦合,耦合损耗小于3.2 dB.开关矩阵中最短光路的片上损耗为13 dB,99%的端口之间串扰低于 —20 dB,采用隔离槽技术开关时间为1.4 ms,总功耗小于1 W.同时,我们还实现了支持双偏振光信号的16×16热光开关[59],用于400 Gb/s PDM-16QAM光传输系统中上传/下载波长信号.这是目前端口数最大的基于偏振分集技术的双偏硅基波导光开关,整个芯片包括416个热光开关单元,896个片上光电二极管监视器,48个偏振旋转分束器和48个模斑转换器,总面积为12.5 mm×12.5 mm.直通信号的偏振相关损耗小于0.3 dB,差分群速度时延小于0.1 ps,上载信号的偏振相关损耗小于1.1 dB,差分群速度时延小于3 ps.

3.2 MRR型开关矩阵

2009年,首个5×5的微环谐振器型硅基波导光开关的设计方案被Poon等[31]提出.它基于cross-bar拓扑架构,其中单个微环半径为20 μm,矩阵的总面积仅为0.1 mm×0.1 mm,与相同规模的MZI开关矩阵相比降低约2个数量级.微环集成了PIN二极管电光相移器,采用载流子注入驱动,开关时间达到1.3 ns,信道间串扰低至—11 dB.由于光开关中采用多模干涉交叉器件替代传统的平面交叉,因此具有更低的损耗和串扰,可以用于单波长或者符合微环谐振器自由光谱程的WDM系统的波长路由.2014年,DasMahapatra等[33]报道了基于高阶耦合微环单元的热光8×7微环谐振器型光开关.每个开关单元采用五阶级联的微环结构和平面二维阵列式热电极,将光学带宽提升至100 GHz,自由光谱程为350 GHz.考虑到各条光路上的微环个数不同,路径相关损耗在14.5—22 dB之间.光开关矩阵的性能和可扩展性受到损耗的限制.2015年,Yang等[60]实现了具有最少开关数的可重构无阻塞四端口微环光路由器.这个4×4交换芯片仅包含四个微环,在所有路由状态下,信道间串扰低于—15 dB.近期,一种1×N/N×1空间波长(解)复用器与低损耗的光纤或2D平面交叉波导转接板组装的方式被Nikolova等[61]提出.基于switch-&-select拓扑架构,波长(解)复用器包含N个硅基微环谐振器和与之耦合的总线波导,用于上传/下载波长信号.这种设计的特点是每条光路仅包含两个微环谐振器,并且只产生二阶串扰.实验结果表明,8×8的硅基微环光开关损耗为10 dB,串扰低至—39 dB.然而,对于未来更大端口的单片集成而言,平面交叉波导转接板越来越复杂,因此可能限制其实际应用前景.

3.3 MEMS驱动波导型开关矩阵

上述MZI和MRR的开关矩阵中的光路都存在损耗和串扰的逐级积累的缺点.近年来一种基于MEMS驱动器与硅基波导耦合器相结合的新型光开关技术得到迅猛发展.采用2.3节中介绍的Seok等[45]提出的双层硅光子平台中的垂直波导绝热耦合器,这种开关矩阵有效地利用了crossbar架构的无源交叉网格传输光信号,解决了各级开关单元的损耗和串扰的逐级积累问题,从而提升了端口数的可扩展性能.2016年,规模为64×64的MEMS驱动波导型光开关被率先报道[45].它包含4096个开关单元,片上最大传输损耗为3.7 dB,开关时间为0.91 μs,串扰低于—60 dB.最近,规模为128×128的MEMS驱动波导型光开关被验证[62],驱动电压降至25 V.然而随着端口数增加,这种高密度的电封装越来越困难.对于N×N的开关,采用行列寻址的方式驱动可以将驱动的电连接数降低为2N个,但开关时间会因为顺序寻址相应增加[63].此外,采用倒装焊的电封装技术已在12×12的矩阵上验证,通过氮化铝的转接板将芯片与PCB板连接起来[64,65].然而,目前尚未报道4096个单元的封装方案,并且较高的驱动电压仍然是实现片上CMOS逻辑电路集成的主要瓶颈.规模为50×50的偏振无关的MEMS驱动波导型光开关也得到初步研究[66],它采用三维立体的交叉波导网格和同时适用于TE和TM模式的绝热耦合器,无需偏振分束和旋转器和两套偏振分集系统,其偏振相关损耗小于8.5 dB,偏振相关时延44 ps,与理论设计还存在一定差距,未来有希望通过改善工艺提升性能指标.

4 硅基光波导开关的关键技术

MZI型的宽带硅光子调制器已经逐步实现商用化,而MRR型的波长相关性器件由于工艺容差和复杂的控制等因素一直活跃在研究领域,尚未大规模商用化部署.尽管硅光子波分复用与解复用器能够适配粗波分复用(course wavelength division multiplexing,CWDM)系统,但是用于灵活处理密集波分复用(dense wavelength division multiplexing,DWDM)的波长路由还是存在一定困难.因此,我们主要研究了MZI型的宽带硅基波导开关.基于近年来的研究成果,在这里总结拓扑架构、无源器件和光电封装等关键技术的现状和挑战.

4.1 拓扑架构

开关矩阵的总体性能在很大程度上依赖于拓扑架构的特点.对于同样规模的端口数,好的拓扑架构具有以下特点:1)开关单元总数目少,即芯片面积小;2)开关级数低,即传输损耗低;3)串扰抑制能力强,即信号信噪比高.常用的紧凑型拓扑架构包含Benes[56],Cross Bar[45],PILOSS[54]和switch-&-select[51]型.Benes型在开关级数上占有显著优势被广泛应用,但是其两条光路共用一个开关单元的特点产生较高的串扰,限制了应用场景;Cross Bar型控制简单,但是开关级数巨大,不适合大规模扩展;PILOSS型的每一条链路的开关级数相同,因此天然地具备较低的路径相关损耗,但是开关总数巨大,同样不适合大规模扩展;Switch& Select型消除了一阶串扰,其性能主要被波导交叉的二阶串扰限制.考虑到硅基光波导开关矩阵可以集成半导体光放大器来补偿片上光信号功率的损失,采用光信噪比代价(optical signal noise ratio penalty,OSNR penalty)来表征光开关矩阵的拓扑架构性能.当信号穿过开关矩阵时,逐级累积的串扰导致OSNR代价.在多波长交换场景(例如WDM系统中的RODAM节点)中,不同波长之间的串扰占主要因素.而在同波长交换场景(例如100GE的数据中心)中,同一个开关单元中具有相同波长的两路光信号会因为开关单元的加工缺陷泄漏到彼此的光路中,产生严重的串扰.针对这些问题,近期我们提出新的平面多级拓扑架构Hybrid Dilated Benes[67],结构如图3(a)所示.此矩阵采用1×2和2×1的开关单元分别作为入口级和出口级,并用Switch & Select拓扑架构的2×2矩阵替换中间级.在此开关矩阵中,每个单元仅通过不超过一路的光信号,有效地抑制了多级矩阵中的一阶串扰积累.图3(b)是针对Hybrid Dilated Benes型开关矩阵,建立交换链路的优化算法中开关单元的波长受限路由规则:同一个开关单元中不能同时导通两路相同波长的光信号,否则在输出端产生严重的串扰.考虑到未来数据中心的交换网络需要同步配置所有节点(即交换矩阵的各链路同时接受需要交换的光信号),而光网络应用中的链路建立是异步的(即任意业务在任意时刻加入到现有的交换网络中),Qian等[67]进一步通过VPIphotonics软件进行光交换系统仿真得到:对于未来数据中心同步光包交换的应用场景,这种拓扑架构对于串扰为—18 dB的典型开关单元具有零阻塞和0.2 dB的OSNR代价;对于光网络交换节点的异步交换的应用场景,这种拓扑架构对于—24 dB的典型开关单元,采用优化的路由算法可以获得小于10—6的阻塞率.

图3 (a)Hybrid Dilated Benes架构的拓扑结构[67];(b)开关单元的波长受限路由规则Fig.3.(a)Topology of 16×16 Hybrid Dilated Benes[67];(b)wavelength constrained routing rules of the switch cell.

图4(a)和图4(b)分别对比了上述几种拓扑架构的总开关单元数和开关级数,间接反映了各种开关矩阵的面积尺寸和损耗.从图中可以看出,当端口数大于32时,Hybrid Dilated Benes架构的开关总数和开关级数与其余四种拓扑架构相比占据明显优势,因此具有更好的扩展性.考虑到目前主流的硅光代工厂的一次性最大曝光面积约为24 mm×32 mm,假设其中20%的面积用于开关单元,40%的面积用于光电封装,40%的面积用于波导连线,对于开关单元的尺寸为100 μm×700 μm的热光开关单元可以实现128×128的最大开关规模.

4.2 无源器件

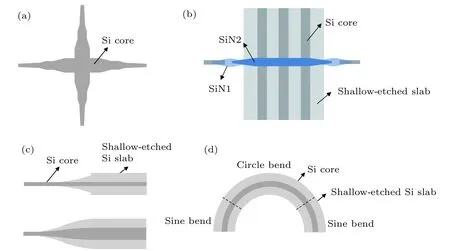

无源器件的设计和工艺直接决定光开关矩阵的损耗和带宽,从而限制其最大端口数.尽管多个研究小组采用片上集成的半导体光放大器(SOA)补偿链路中的光损耗,但是由于自发辐射带来的噪声,它引入的信噪比恶化问题不可避免[68-70].片上光路的总损耗主要包括开关单元、交叉波导和各种连接波导的损耗三大部分.这里重点讨论220 nm的SOI平台上的C波段(1530—1565 nm)的无源器件的现状和挑战.MZI中的50:50分束器的附加损耗和两个输出端口的光功率失衡是开关单元的损耗和串扰受限的主要因素.目前我们报道的热光开关单元损耗小于0.5 dB,其中多模干涉50:50分束器[71]的损耗为0.15 dB,两个输出端口光功率失衡小于0.3 dB,因此开关单元串扰低于—30 dB.交叉波导的性能不仅影响光路损耗,还限制着不同信道之间的串扰.近期两种不同类型的交叉波导被报道:图5(a)是基于一维高斯光束的三模式合成原理的平面多模干涉交叉波导,通过多段多模波导的级联,优化交叉区域的模式轮廓使损耗降至0.007 dB,串扰小于—40 dB[72];图5(b)是三层氮化硅-硅混合平台上硅-氮化硅-硅立体桥式交叉波导,采用前道工艺中的低压化学气相沉积法加工氮化硅层可以获得小于0.003 dB的损耗和低于—56 dB的串扰,是未来大规模交叉矩阵中最具潜力的器件[73].矩阵的总线波导的损耗是开关端口扩展的另一主要限制,主要依赖于硅波导加工过程中产生的侧壁的粗糙程度.我们在新加坡微电子所采用193 nm深紫外光刻工艺加工的0.5 μm宽的单模条形波导传输损耗为2.5 dB/cm,3 μm宽的多模脊型波导的传输损耗为0.5 dB/cm,因此矩阵中的开关单元之间的总线波导优先采用3 μm宽的多模脊型波导降低片上总传输损耗[74].事实上,精度更高和一致性更好的工艺可以进一步降低波导损耗,例如采用45 nm浸润式光刻,在12英寸硅光子平台上可以实现0.5 dB/cm传输损耗的单模条形波导[54],但是加工成本也更昂贵.图5(c)是我们报道的单模条形波导与多模脊型波导的转接波导,它的轮廓为优化的拉伸正弦曲线,长度为25 μm,损耗为0.029 dB.单模条形波导与单模脊型波导的转接波导轮廓为优化的凹椭圆型,在长度仅为10 μm的区域内损耗为0.002 dB[74].图4(d)是一种基于正弦—圆弧—正弦轮廓的半径为5 μm的单模脊型弯曲波导,通过优化曲率渐变的弯曲波导,可使损耗小于0.008 dB[75].

图4 几种不同拓扑架构的开关矩阵的(a)总开关单元数和(b)开关级数Fig.4.Switch matrix of different topologies (a)total number of switch cells and (b)total number of matrix stages.

图5 无源器件 (a)平面交叉波导[72];(b)立体交叉波导[73];(c)转接波导[74];(d)弯曲波导[75]Fig.5.Passive components:(a)In-plane waveguide crossing[72];(b)3D waveguide crossing[73];(c)transition waveguide[74];(d)bend waveguide[75].

4.3 光电封装

与硅基波导收发端器件不同,光开关芯片需要大规模高密度的光学耦合和电学封装.近期我们报道了规模为32×32全功能光电封装的硅基光波导开关芯片和系统样机[58,76].具有大规模量产潜力、大端口数的光学封装的光学耦合方案主要有:聚合物波导倏逝波耦合器[77],阵列光栅耦合器[78],SiO2-ZrO2波导高折射率差PLC连接器[79]以及离子扩散型PLC光纤间距转换器[80].我们采用离子扩散型PLC光纤间距转换器的扇出功能,将保偏光纤阵列中纤芯间距为127 μm的光纤与芯片上间距为20 μm的模斑转换器进行逐一端面耦合和固化.实验表明,耦合损耗和连接器的传输损耗总共是1.1 dB,连接器与光开关芯片的模斑耦合器阵列的耦合损耗是1.2 dB,不同通道的对准容差导致的误差损耗为0.5 dB,最后经过紫外固化引入0.4 dB的附加损耗,单端耦合的总损耗小于3.2 dB.针对当前通道数小于2000,速率低于MHz量级的电封装需求,我们采用了陶瓷球栅阵列技术.先将每个光开关的驱动和监控信号通过片上金属走线扇出到芯片四周,再通过引线键合工艺与陶瓷基座连接,最后采用表面贴装技术将陶瓷基座与转接板焊接.转接板通过A/D模数转换芯片将监控探测器的信号送入FPGA主板,并通过驱动板的D/A数模转换芯片控制光开关单元.这种电封装方案通常受到引线数量的限制,对于更大端口数的开关矩阵,倒装焊[54]和硅穿孔技术[81]可以将电路与光路分离,消除电封装对光信号的影响,更具有优势.

5 挑战与展望

光纤通信、数据中心和光计算不断增长的互连需求推动了光开关技术的商用部署.硅基光波导开关技术已经受到广泛关注,在解决带宽、成本和功耗等方面存在潜在的优势.本文回顾了业界目前最先进的MZI型、MRR型和MEMS驱动波导型光开关技术,并从拓扑架构、无源器件和光电封装等方面分析了大端口开关矩阵的技术挑战.尽管近年来硅基波导光开关技术发展迅速,但仍有若干技术挑战制约它的实际应用,需要进一步研究.

第一,偏振管理.商用的光开光模块通常具有偏振无关的特性,即对任意偏振态的光信号都可以实现开关功能.而大部分的硅基光波导开关只适合单一偏振态的光信号传输,因此具有高度的偏振敏感性.硅基光波导开关的光信号偏振管理的方法通常可以分为四类:保偏光纤技术、偏振分集技术[59,82]、偏振不敏感波导技术[50]以及偏振控制技术[83].保偏光纤技术采用保偏光纤阵列与芯片上硅基光波导耦合器对接,将光纤里传输的不同偏振态的光信号分别耦合到硅基光波导的TE或TM模式中交换.相对于普通光纤阵列而言,保偏光纤阵列的制作涉及偏振轴的精密调整,具有较高的成本,一般只用于少量端口数或实验室级测试和验证.偏振分集技术将光链路中不同偏振态的光信号分离或进一步偏振转换,使之通过两路单偏振光路和器件,分别完成不同偏振态的光信号的空间交换,最后再通过偏振合束器将分离的两路光信号合波.由于两路单偏振态的光信号采用不同的光路分别交换,合理的管理和配置两路不同偏振态的光信号的差分群时延和偏振相关损耗是偏振分集交换系统中低误码率的重要保证.首先,传统的光纤型偏振分束/合波器难以将两路光纤的长度差控制在1 mm以下,导致两路不同偏振态的光信号的相位差无法精准控制,因此这种方法不仅需要高偏振消光比的片上偏振/旋转分束器件,还需要在两路单一偏振的硅基波导光开关光链路上补偿相位延时波导和光功率可调衰减器件.其次,同一芯片上的两个硅基光波导开关矩阵的每一路都需要通过偏振分束/合波器连接,必定产生大量的波导交叉器件,因此芯片的布局需要精心优化,以实现每条光链路包含相同数量的平面波导交叉器件和尽可能相同长度的延时波导.最近,Tanizawa等[84]提出在PILOSS架构的8×8开关矩阵中反向传输两种偏振信号的方法,实现了仅需一个开关矩阵的偏振分集方案,偏振相关损耗小于2 dB且差分群时延小于1.5 ps.偏振不敏感波导技术采用微米尺度的偏振不敏感波导或偏振不相关器件构建光开关单元,实现不同偏振态的光信号的同时切换.这类技术通过在厚硅平台(1.5 μm厚的顶层SOI晶圆)上对脊型波导纵横比的优化获得尽可能小的双折射效应.与220 nm的薄硅平台相比,此技术的优点是偏振相关性低且硅基波导与光纤的耦合损耗低,缺点是厚硅平台通常具有更大的弯曲半径,因此器件的集成密度较低.偏振控制技术不仅包括偏振/旋转器件的研究,还涉及到随机偏振态的实时跟踪和矫正算法,因此存在硬件和软件的实现,在多路并行光链路中尚未大规模应用.总之,偏振分集技术和偏振不敏感波导技术是近期可能商用的硅基光波导开关偏振管理技术,需要进一步优化偏振/旋转器件的设计和波导工艺.随着半导体加工工艺和晶圆质量的提升,更好的波导一致性有助于进一步降低偏振相关损耗和差分群时延,提升硅基波导光开关的偏振特性.

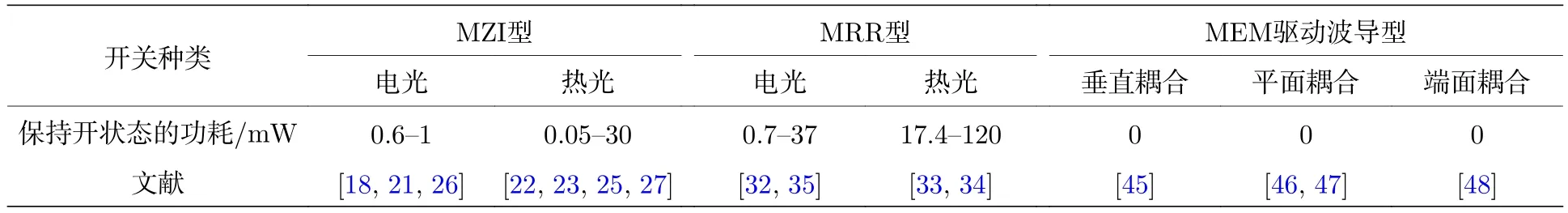

第二,能耗效率.为了在能耗效率上具有竞争力,要求硅基光波导开关在每条光链路的平均功耗不超过每路光收发器的功耗.考虑到长途骨干网和城域网中的DWDM传输系统中的收发器功耗通常处于瓦量级,交换节点处的硅基波导光开关的功耗与之相比较低,因此很容易满足上述要求.然而,在数据中心的短距光包交换和光计算应用中,由于光收发器功耗大幅降低,能耗的主要来源是高速电交换和O/E/O转换过程,因此如何将数据交换的平均能耗降低到1 pJ (即数据带宽为100 Gb/s的光链路功耗小于100 mW)是保证绿色低功耗硅基光交换的竞争力的关键.硅基波导光开关的能耗主要来源于开关引擎保持开关某一状态所需的能量、补偿工艺误差的热调谐相位补偿器以及控温/散热组件的耗能等.表4总结了不同的光开关引擎保持在开启状态的功耗.MZI型电光开关引擎采用双臂推拉的驱动方式将光开关的切换功耗降低到1 mW左右[18,21,26],而MZI型热光开关引擎通过隔离槽技术和折叠相移器构型实现了低至0.05—30 mW的开关功耗[22,23,25,27].MRR型光开关引擎由于需要同时驱动多个相互耦合的高阶微环谐振器,通常需要数十到上百毫瓦的开关功耗[32-35].值得关注的是,MEMS驱动波导型开关引擎由于通过静电驱动器控制光耦合器的波导位移实现光路的切换,因此这类光开关在开启状态时的驱动功耗为零[45-48],在上述三种开关引擎中具有最低的能耗.当MEMS驱动波导型开关在兆赫兹量级的频率下高速切换时,由于静电驱动器的电容反复充放电,回路中产生的焦耳热消耗的平均功率一般小于10 mW.对于我们研究的32×32 MZI型热光开关,当每路通过100 Gb/s光信号时,每个开关单元功耗小于5 mW(其中1 mW引擎驱动,2 mW工艺补偿,2 mW温控),即功耗效率约为0.8 pJ/bit,比电交换低两个数量级.未来,为了进一步提升光交换系统中的信号质量,人们可以在硅基波导光开关芯片上集成高密度、低成本的SOA.例如,对于8通道100 Gb/s的WDM系统的光链路而言,典型的功耗为0.5 W的非制冷SOA在上述功耗效率的基础上增加0.6 pJ/bit.另一方面,逐渐成熟的300 mm晶圆加工工艺将具有更好的一致性,因此用于工艺补偿的热相依器的功耗有望进一步降低.总体来说,通过提高芯片加工的一致性和SOA的能耗效率是实现绿色低功耗的主要研究方向.

第三,集成驱动.目前大部分的研究组采用引线键或者倒装焊的封装方式将开关芯片与外部控制电路连接,通过驱动板上的电压或电流信号控制开关的状态并优化偏置信号,通过监控板标准的通信协议和逻辑接口完成校对、监控和控制等功能.驱动板包括数据缓存、DAC或脉冲宽度调制(PWM),而监控板包括跨阻放大器(TIA),ADC和低通滤波器.这种控制方案不但体积庞大,而且随着开关端口数的增加,开关芯片上的引脚密度限制了开关端口的进一步扩展.目前,常见的硅光芯片代工和封装平台提供3层金属沉积和4圈金属焊盘键合工艺.如果要进一步提升电封装,人们通常将硅光芯片倒装焊接到高密度的陶瓷转接板,再进一步焊接在PCB线路板上.由于高密度的电封装极具挑战,发展基于CMOS工艺兼容的硅光芯片上的数字晶体管逻辑控制电路变得更具吸引力.片上逻辑电路通过驱动向光子器件提供模拟的电压或电流控制信号,同时通过数字串行通信接口实现逻辑电路单元与外部电路的通信.因此,大量的器件引脚被少量可编程的串行逻辑单元引脚取代,从而大大降低了电封装的挑战.IBM在此领域率先进行了多年的研究[52,53],已经在8×8电光开关矩阵芯片上验证了数字晶体管逻辑控制集成驱动方案.此外,更近的逻辑驱动与光器件的连接有利于降低光开关的功耗,并提高逻辑电路对物理参量(光功率、温度或电压/电流)的监控和反馈控制的优化算法效率.

表4 不同的光开关引擎在保持开状态时的功耗Table 4.Comparison table of the power consumption of the switch engines at ON state.

第四,工艺平台.硅基光电子技术作为CMOS工艺平台上成长起来的一个新技术,从设计方法、工艺流程和封装测试等方面看,很大程度上参考并借鉴了微电子技术的发展经验.硅基光电子的未来商业化模式取决于制造代工厂的能力和可获得性.从商业模式看,在过去几十年里,无晶圆设计(fabless design)和标准化工艺的代工厂相结合占据主要模式.设计者通过中介机构(例如美国的OpSIS,加拿大的CMC,欧洲的ePIXfab和中国的重庆联合微电子中心等)与代工厂(例如新加坡的IME,欧洲的IMEC和LETI,美国的Global foundry,中国科学院电子研究所集成电路先导工艺研发中心和上海微技术工业研究院等)合作,按照标准的设计和工艺流程(PDK设计工具包)采用多项目晶圆服务(muli-project wafer,MPW)模式完成芯片加工.这种模式成本低廉,提供了硅基光电子器件所需的光刻、腐蚀、沉积和掺杂等基础工艺,适合科研机构和小规模中试平台的开发和验证.然而,针对未来越来越多各式各样的产品和应用需求,这就要求代工厂能够提供各种定制化的材料集成、加工和封装工艺.近期,IME为部分用户提供了定制的双层氮化硅平台和深刻蚀槽[73],改进了波导的传输损耗和热调谐相移器的性能,为大规模的硅基波导光开关阵列和光学相控阵列的研发提供了良好的平台.从工艺技术看,硅光子技术的特征尺寸一般约为500 nm,最小尺寸约为100 nm左右,因此采用193 或者248 nm的深紫外光刻技术可以满足加工要求,无需像微电子技术采用更低的工艺节点.然而,更小的工艺节点通常具有更好的一致性和重复性,却产生更高的成本,这就需要按照应用需求选择合理的工艺技术.此外,硅基光电子器件对尺寸和工艺误差非常敏感,不但纳米量级的工艺误差足以对硅光子器件的波长和相位带来明显的影响,而且波导器件的侧壁粗糙度也限制着光信号损耗.随着国内外CMOS硅基光电子工艺线逐渐从8英寸升级为12英寸晶圆,大规模的硅基波导阵列的一致性和重复性会进一步改进.同时,以硅材料作为基底的各种III-V族、聚合物集成技术和硅锗外延集成发光技术多路径发展将成为硅基光电子的必然选择.硅基光电集成芯片通常可分为单片集成和混合集成两大类.单片集成是采用完整的CMOS工艺将光子器件和电子器件集成在同一硅衬底上,尽管大规模实用化是终极目标,但是设计和工艺相互受限,仍然存在一些尚未解决的技术难题,例如金属走线与波导的间距、多晶硅的应力以及氮化硅和氮氧化硅的沉积等会影响光器件的损耗;锗及其化合物的外延生长和掺杂工艺的精准控制等会影响器件的高频特性.另外,硅在常温电泵浦发光的问题还在挑战中.混合集成采用各种简单的工艺(例如倒装焊、键合和异质外延等)将各种基于III-V族化合物和高非线性的聚合物材料的器件集成到硅基衬底上,工艺灵活且互不干扰,发挥了各种材料体系器件的优势,不仅取得了优异的性能还降低了工艺难度.然而,混合集成的工艺兼容性差,封装和耦合成本高.总体而言,硅基光波导开关芯片正从混合集成向单片集成不断发展,逐步提升端到端的光交换性能.

6 总 结

随着硅基光电子器件和半导体工艺的不断演进与发展,先进的制造工艺将为硅基波导光开关的低功耗、低成本、小尺寸、高集成度等提供良好的解决方案.与传统电开关技术相比,硅基波导光开关技术的优势将越来越显著,硅基波导光开关阵列伴随技术的不断发展,整体性能必将超越电开关,这将为硅基波导光开关迎来更为广泛的应用场景.硅基波导光开关技术在不久的将来将为整个光通信领域带来更加重大的进步,尤其在能耗、成本、设备体积等方面取得显著进步,成为推动各行各业进步不可或缺的重要光电子技术之一.