基于RocketIO可靠性传输改进方案的研究与实现*

2019-05-31曹健辉鲁战锋

曹健辉,周 刚,鲁战锋

(中国电子科技集团公司第三十研究所,四川 成都 610041)

0 引 言

本项目需要在多张信号处理板卡之间传输实时、可靠的数据,而并行传输需要在背板上布置多路并行信号线,设计复杂,不能满足本项目的要求。因此,本项目采用现场可编程门阵列(FPGA)实现高速串行接口。

Xilinx公司Virtex-5 FPGA内嵌的RocketIO GTP收发器为物理层,利用基于自定义协议的传输模型,实现两者间单向多通道高速串行传输。设计时,RocketIO收发器采用一对差分线,仅需要两根数据线,大大节省了I/O口资源,也使印制板的布线更加方便。

1 RocketIO收发器

1.1 RocketIO主要特点

Xilinx公司65 nm工艺的Virtex-5系列FPGA的LXT和SXT平台内嵌了RocketIO GTP(Gigabit Transceiver with Low Power)高速收发器,主要特征为[1:]

(1)每个通道收发器支持0.1~3.2 Gb/s的速率,支持5X的数字过采样(当数据率处于100 ~500 Mb/s);

(2)收发器内嵌发送时钟生成电路和接收时钟恢复电路;

(3)支持可编程差分输出电压摆幅和可编程预加重,用于改善信号的完整性;

(4)收发器支持直流和交流耦合方式,可兼容多种高速接口标准;

(5)片内集成可编程差分终端电阻,50 Ω用于芯片间互连,75 Ω用于电缆连接;

(6)支持片内多种环回测试模式;

(7)支持8b/10b编码,可编程边界检测符(Comma),提供对多种标准协议的支持。

1.2 RocketIO主要组成部分

一个完整的RocketIO收发器主要包括两个子层:物理媒介适配器(PMA)和物理编码子层(PCS)。其中,PMA子层主要用于数据串行化和解串、高速时钟生成及恢复,包括发送预加重、接收均衡器等在线配置技术,以实现最优信号完整性。PCS子层主要包括Comma检测对齐、8b/10b编解码、CRC校验和用于通道绑定和时钟修正的弹性缓冲[2]。

数据串行化和解串。在发送端,收发器把输入GTP的参考时钟作20倍频,作为发送线路的参考时钟,然后将经过编码的并行数据转化为串行数据,从串行差分端发送出去;在接收端,时钟恢复电路从比特流中提取出时钟相位和频率,恢复出接收时钟,将串行数据解码并转化为并行数据送入用户接口,以进行其他操作。

8b/10b编解码:RocketIO收发器采用标准的8b/10b编码机制将8位字符转化为10位字符,保证了良好的直流平衡特性,有利于交流和直流耦合和时钟恢复。

CRC校验:CRC循环冗余检测用于对被接收数据的出错检测,RocketIO收发器CRC循环冗余检测逻辑直接32位产量CRC,被用于如Gigabit Ethernet、Fibre Channel、InfiniBand 和 User-defined等通信模式[3]。

PRBS为伪随机二进制序列,用于测试高速串行通道传输误码率。

CDR(Clock and Data Recovery)为时钟数据恢复电路,和接收均衡器协同负责从一个复合信号中把时钟和数据都正确恢复出来[4]。

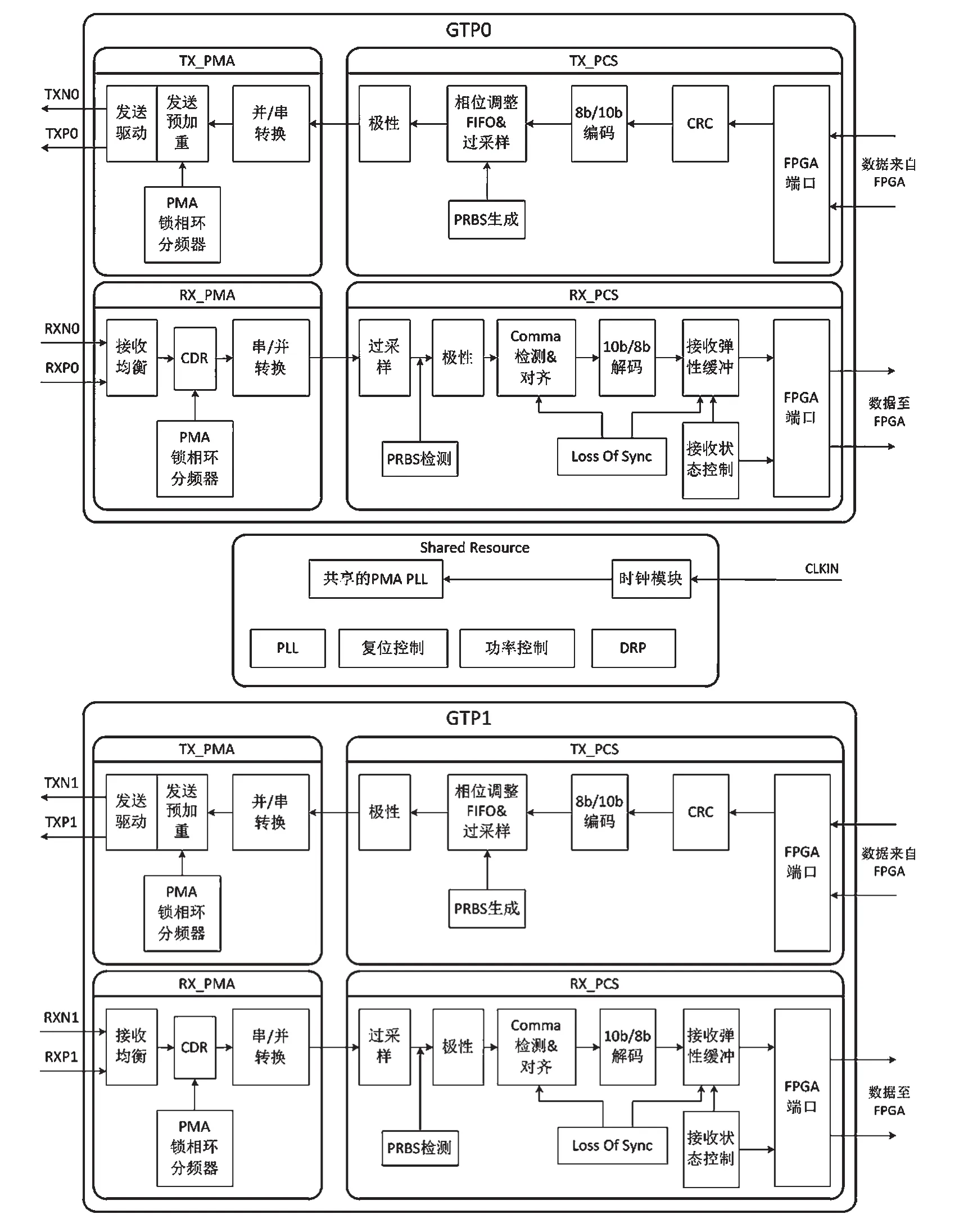

在Virtex-5 LXT和SXT器件中,每个GTP_DUAL模块包含2个GTP(GTP0和GTP1)。GTP_DUAL的模块框图见图1。

2 系统架构

本文构建了一个多张信号处理板卡使用RocketIO的系统。FPGA选择Xilinx公司的Virtex-5系列的XC5VSX95T,逻辑密度范围是35 000~95 000逻辑单元。采用RocketIO实现多张信号处理板卡之间的数据传递,信号处理板卡A和信号处理板卡B为RocketIO发送端,信号处理板卡C和信号处理板卡D为RocketIO接收端。信号处理板卡A和信号处理板卡B分时使用,信号处理板卡A同时发送实时数据到信号处理板卡C和信号处理板卡D,信号处理板卡B同时发送实时数据到信号处理板卡C和信号处理板卡D。本文RocketIO系统架构如图2所示。

2.1 RocketIO时钟

GTP_DUAL的参考时钟有以下三种方式[5]:

(1)使用外部晶振驱动GTP专用时钟线路。当时钟源满足器件手册上的指标要求时,设计具有最佳性能;

(2)通过专用时钟走线,使用来自相邻GTP_DUAL的参考时钟。同一列上,时钟布线跨线从源端到目的端,中间相隔的数量不超过3,且禁止GTP_DUAL之间时钟交叉走线;

(3)使用FPGA内部的时钟(GREFCLK),虽然用法灵活多样,但性能最差,因为会引入较大的时钟抖动,只适合低传输速率、低误码率要求的场合。

本项目最开始使用的是FPGA内部的时钟来驱动RocketIO。

2.2 RocketIO协议

RocketIO支持基于标准协议的可靠通信模型和基于自定义协议的实时传输模型,标准协议包括Aurora、Serial RapidIO、PCI Express和 XAUI等[6]。

图1 GTP_DUAL的模块

图2 RocketIO系统架构

由于本项目需要实时发送引导数据,而引导数据量不大,但对及时性和可靠性要求较高,因此未采用标准协议,采用的是自定义协议。本项目对RocketIO外部接口进行了封包处理,满足了通用化和模块化的使用需求。

3 RocketIO参数配置

3.1 设置PMA_PLL速率

PMA_PLL速率确定需遵循以下原则,并通过以下公式计算得出。

(1)PLL_DIVSEL_REF={1,2};

(2)PLL_DIVSEL_FB={1,2,3,4,5};

(3)当OVERSAMPLEMODE=TRUE或OVERSAMP LEMODE=FALSE且INTDATAWIDTH为高时,DIV=5;当OVERSAMPLEMODE=FALSE且INTDATAWIDTH为低时,DIV=4;

(4)系统时钟f PLL CLK=f CLKIN*PLL_DIVSEL_FB* DIV/PLL_DIVSEL_REF,f PLL CLK必须处于1.5 ~ 3.25 GHz;

(5)一旦f PLL CLK确定,发送和接收线速率即可基本确定,具体计算公式如下:

①接收端串行时钟速率=2*f PLL CLK/PLL_RXDIVSEL_OUT_n;

②发送端串行时钟速率=2*f PLL CLK/PLL_TXDIVSEL_OUT_n。

3.2 设置RocketIO时钟

由于RocketIO高低温试验时出现了传输误码的情况,因此改为外部专用晶振加硬件锁相环作为专用时钟源。专用时钟经过倍频分频,最后供给GTX_DUAL_TILE的时钟频率为200 MHz(例化时需要使用IBUFDS原语)。

在配置共享PMA锁相环时钟时,需要根据输入时钟的频率确定共享时钟的属性。本系统中输入时钟为200 MHz,所以CLK25_DIVIDER需要配置为10。

本系统采用的时钟配置如下。

TXUSRCLK是RocketIO发送端PCS的内部时钟,该时钟的频率由以下公式计算求得:

TXUSRCLK Rate=Line Rate/Internal Datapath Width

TXUSRCLK2是RocketIO发送端的主要同步时钟,速率值由TXDATAWIDTH值和TXUSRCLK共同决定。

TXDATAWITH={0,1,2},其中0代表F_TXUSRCLK2=2*F_TXUSRCLK;1代表F_TXUSRCLK2=F_TXUSRCLK;2代表F_TXUSRCLK2=F_TXUSRCLK/2。

TXUSRCLK和TXUSRCLK2必须为同源时钟,且两者上升沿需对齐。本设计使用REFCLKOUT时钟结合专用的分频倍频模块来产生所需的TXUSRCLK和TXUSRCLK2时钟。

3.3 设置复位选项

系统复位很重要。工程实践中发现,若使用恢复时钟接收前不对GTX_DUAL进行复位,将无法正常收到数据。本系统复位通过以下方式实现:将GTXRESET拉高保持120 μs,然后拉低。

4 RocketIO发送端配置

4.1 RocketIO发送接口宽度设置

RocketIO发送接口宽度由以下参数决定。当以下三个参数不同组合时,发送接口宽度也不同。

(1)INDATAWITH={0,1},其中0代表内部数据宽度为16 bit,1代表内部数据宽度为20 bit。

(2)TXDATAWITH={0,1,2},其中0代表发送口数据宽度为8 bit或10 bit,1代表发送口数据宽度为16 bit或20 bit,2代表发送口数据宽度为32 bit或40 bit。

4.2 RocketIO发送端编码配置

本设计使用8b/10b编码。8b/10b编码是一种工业级编码策略,实现方法是每个字节会有2 bit的冗余码,以此提高数据传输的可靠性,且RocketIO自带的8b/10b编码不占用FPGA资源,并能降低传输误码率,因此本设计中采用了8b/10b编码功能模块。

设计中配置如下:

(1)TXBYPASSB10B[3:0]={0,1},其 中TXBYPASSB10B[x]=0代表相应的字节被8b/10b编码,TXBYPASSB10B[x]=1代表相应的字节不被8b/10b编码。

(2)TXENC8B10BUSE={0,1},其 中TXENC8B10BUSE=0代表相应的字节不被8b/10b编码,TXENC8B10BUSE=1代表相应的字节被8b/10b编码。

4.3 RocketIO发送端数据速率配置

RocketIO发送端数据速率配置如下:

Tx Line Rate=PLL Clock Rate*2/PLL_TXDIVSEL_OUT

当oversampling为高时,有:

Tx Line Rate=PLLClock Rate*2/PLL_TXDIVSEL_OUT*5

4.4 RocketIO发送端驱动配置

RocketIO发送端驱动有以下特点:

(1)支持不同的电压值;

(2)支持不同预加重值;

(3)可配置终端平衡。

本系统采用的是输出摆幅为1 100 mV。详细配置如下:

(1)TXDIFFCTRL[2:0]配置值为101;

(2)TXBUFDIFFCTRL[2:0]配置值为101;

(3)TXPREEMPHASISI[2:0]配置值为101。

经过实践证明,部分板卡在驱动摆幅不属于上述配置时,有些板卡常温情况下能正常通信,有些不能正常通信;还有一些板卡在常温下能正常,但在高低温环境下不能正常通信。本系统是基于此原因开展研究和实现的。

5 RocketIO接收端配置

5.1 RocketIO接收端CDR配置

接收端也由PCS和PMA两部分组成。接收端接收时钟数据恢复电路(CDR)并从中提取出恢复时钟,利用该恢复时钟能很好地将接收数据提取出来。在总线传输过来的数据可用前,嵌入在信号中的恢复时钟必须先被取出。

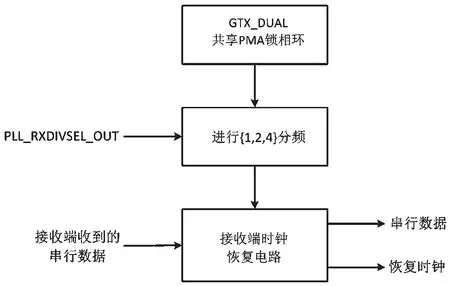

CDR电路从共享的PMA锁相环中取出高速、分频的串行时钟,并矫正它的相位和频率,直到该时钟的转换能够与发过来的数据相匹配,从而产生正确的串行数据流。选用恢复时钟后,必须在接收数据前先对时钟恢复电路进行复位,具体实现流程如图3所示。

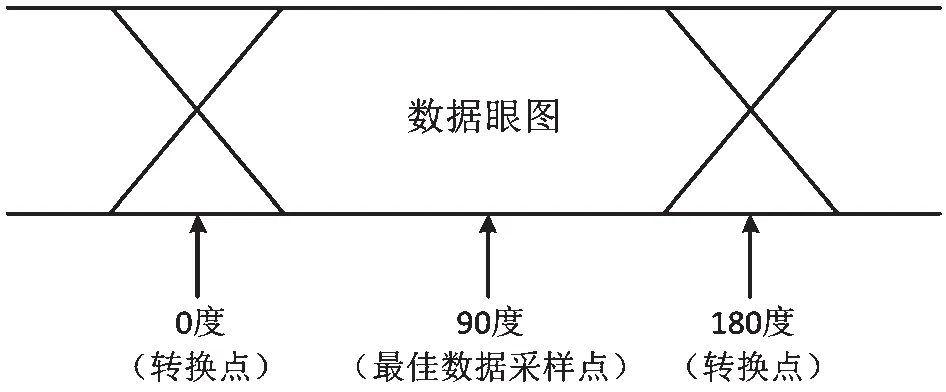

CDR能够在进来的数据中查找数据转换点,并用数据转换点恢复时钟。这些转换点能够辅助数据采样时刻的选择。为了降低数据采错的概率,CDR应选择距离转换点较远的地方进行数据采样,这个位置就是数据眼图的中心,如图4所示,此处的数据最稳定。

图3 CDR时钟恢复流程

图4 数据眼图

5.2 RocketIO接收端参数配置

根据本设计数据的传输需求,本设计的参数设置如下所示。

(1)过采样配置

因为本系统的传输速率为400 Mb/s,刚好处于过采样要求的传输线速率范围内(150~750 Mb/s),所以OVERSAMPLE_MODE设置为TRUE,PMA_CDR_SCAN的参数设置为27’h6404040,把90°位置作为数据采样点,达到了最优设计。

(2)接收线速率配置

RX Line Rate=PLL Clock*2/PLL_RXDIVSEL_OUT

(3)8b/10b解码器

8b/10b解码器对应的是8b/10b编码器的逆过程,本应用中使用了8b/10b解码器。

(4)时钟纠正

因本设计使用的是恢复时钟且进行了过采样,而过采样模块中包含了隐藏的buffer,可解决RXUSRCLK和RXRECCLK之间的相位差,所以不用RX elastic buffer,不用进行时钟纠正。因为不用RX elastic buffer,所以也不用进行通道绑定。

(5)接收数据位宽配置

R X D A T A W I D T H={0,1,2},其 中TXBYPASSB10B[x]=0表示接口宽度为8 bit;TXBYPASSB10B[x]=1表示接口宽度为16 bit;TXBYPASSB10B[x]=2表示接口宽度为32 bit。

(6)接收数据时钟配置

F RXUSRCLK配置选项如下:

① F RXUSRCLK=line Rate/16,当 INTDATA WIDTH=0;

② F RXUSRCLK=line Rate/20,当 INTDATA WIDTH=1。

F RXUSRCLK2配置选项:

①F RXUSRCLK2=2*F RXUSRCLK,当RXDATA WIDTH=0;

②F RXUSRCLK2=F RXUSRCLK,当RXDATA WIDTH=1;

③F RXUSRCLK2=F RXUSRCLK/2,当RXDATA WIDTH=2。

本设计中RXUSRCLK为RXRECCLK,RXUSRCLK2为RXRECCLK/2。

本设计接收端数据位宽配置如下,三条配置共同将接收接口位宽配置为32 bit:

(1)INTDATAWIDTH=1;

(2)RXDATAWIDTH=2;

(3)RXDEC8B10BUSE=1。

6 试验验证

多张信号处理板卡工作时出现了较高的误码,排除硬件故障后,对系统中RocketIO相关参数进行了如下优化。

(1)优化RocketIO时钟使用方式。由原来使用FPGA内部的时钟改为使用RocketIO内部专用时钟走线;接收端用数据恢复时钟代替本地时钟进行数据接收。

(2)降低RocketIO的传输线速率。由原来的2 Gb/s降低为400 Mb/s(经过技术验证,降为400 Mb/s不影响功能性能指标)。

(3)增大了发送端输出驱动摆幅,由原来的500 mV增大为1 100 mV。

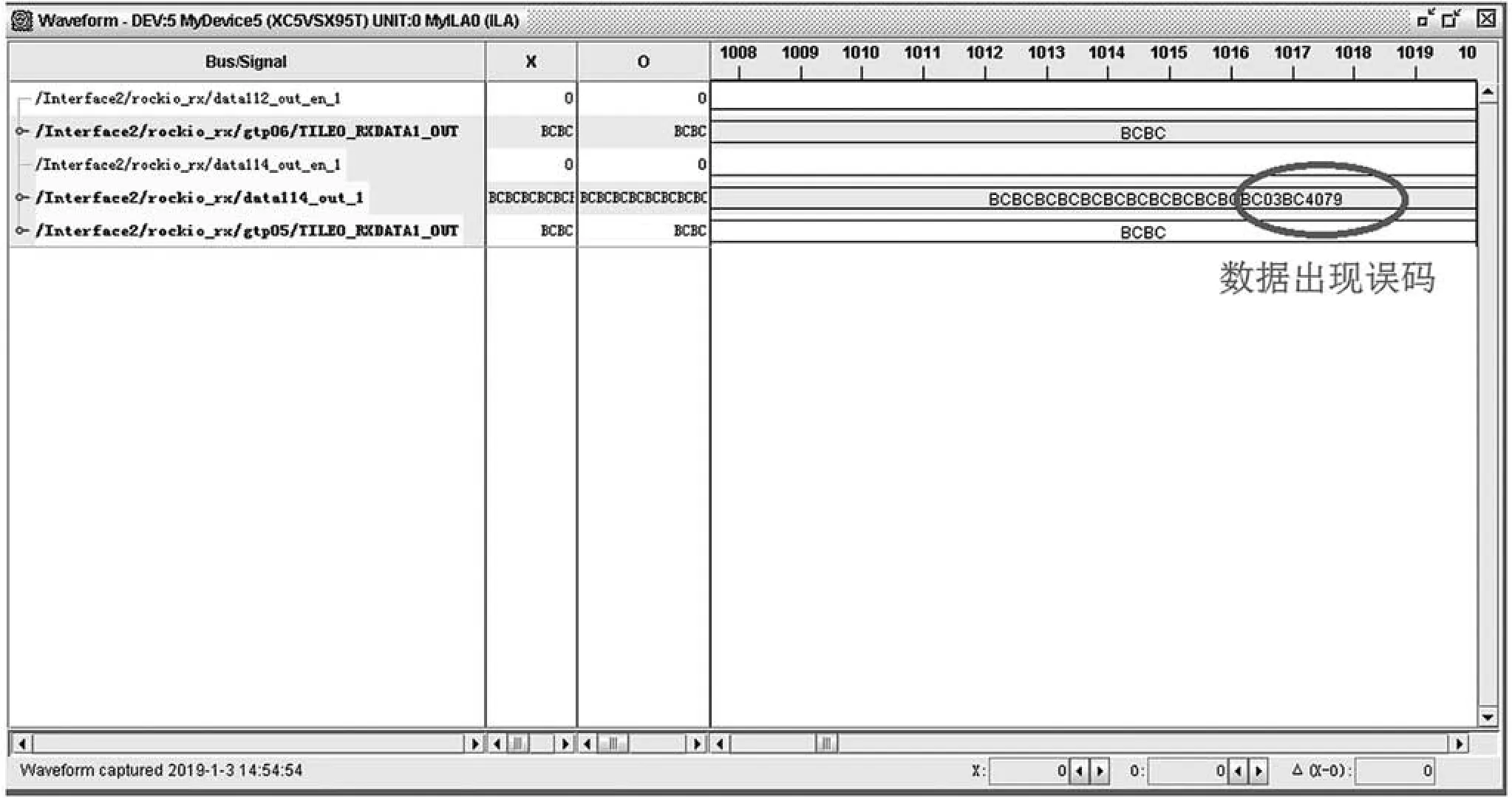

图5为改进前的Chipscope截图,出现了误码(BC03BC4079),正常情况下应该只有握手码(BCBCBCBC……)或者自定义协议报文(89ABCDEF……)。

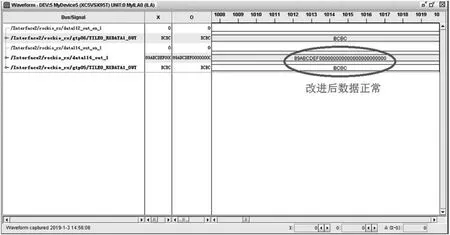

图6为改进后的Chipscope截图,收到的数据只有握手码(BCBCBCBC……)或者自定义协议报文(89ABCDEF……)。

图5 改进前Chipscope截图

图6 改进后Chipscope截图

升级发送端和接收端的FPGA程序,经过长时间常温和高低温(高温工作:+55 ℃,低温工作:-20 ℃)加电工作的试验,RocketIO接收端未再出现误码。

7 结 语

通过优化RocketIO时钟使用方式,降低了RocketIO传输线速率,增大了发送端输出电压摆幅,能够解决RocketIO出现较高误码的问题。