二次雷达显控终端的设计与实现

2019-03-19李红兵

李红兵

(中国电子科技集团公司第十研究所,四川 成都 610036)

0 引 言

显控终端是二次雷达信息输出和人机交互的重要设备,主要完成雷达系统的参数设置、图表和航迹显示、工作状态检测、参数查询等功能[1]。近年来,随着大规模集成电路的发展以及电子系统综合化思想在雷达整机技术中的广泛应用,二次雷达系统对显控终端的性能要求也越来越高。

在某型二次雷达显控终端的工程研制中,本文基于模块化设计实现了一种通用显控终端,接口丰富、标准,工作稳定、性能可靠,图形显示基于Linux操作系统,利用Qt和MySQL等相关软件进行开发。该型显控终端还可以扩展到后续任务,随雷达整机应用于不同舰船平台上,具有广阔的应用前景。

1 总体设计原理

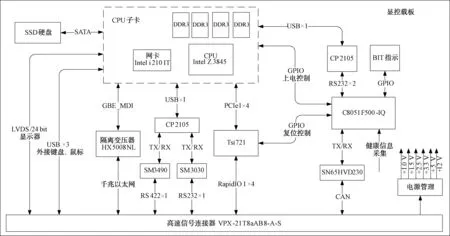

考虑显控终端的通用性和可扩展性,以CPU子卡为核心搭建二次雷达显控终端的硬件平台,图1为其原理框图,电路设计采用6U VPX的标准,对外接口兼容VITA46规范,主要由CPU子卡和显控载板构成,二者通过高速COMe连接器互联。显控载板提供电源管理电路、健康管理电路、通信接口电路和人机交互电路等功能。

图1 显控终端硬件设计框图

CPU子卡为板载X86架构的CPU、DDR3内存、千兆以太网卡、USB控制器等,外围电路只需扩展电子硬盘,提供直流供电,就具备独立工作的能力;电源管理将外部直流输入电源转换为多种电压,为显控终端提供稳定的二次供电;健康管理电路收集模块的温度、电压等信息,监控硬件电路的工作状态;通信接口电路完成数据的输入、输出功能;人机交互电路通过LVDS显示接口输出雷达系统的工作状态、航迹和ADS-B信息,雷达操作人员通过USB键盘按键操控,完成雷达控制命令输入。

2 硬件电路介绍

2.1 CPU子卡介绍

CPU子卡选用德国控创公司的COMe模块COMe-mBT10,该模块基于COMe Express标准,接口兼容PCIMG规范COM.0 Rev 2.1版本,尺寸为85 mm×54 mm;CPU为Intel的Z3845四核超线程低功耗处理器,运行频率最高达1.91 GHz,内部集成高性能GPU,具有较强的二维、三维图形绘制能力;子卡板载4 GB容量DDR3内存;对外提供1路4×的PCIe、7路USB、2路SATA和千兆以太网等高速接口,具有卓越的连接性,同时集成LVDS显示接口;操作系统支持Windows、Linux和VxWorks。

2.2 电源管理电路

电源管理是决定硬件平台是否稳定的重要因素之一,电源设计必须严格按照处理器手册上要求的上电时序和下电时序,否则可能引起电流过冲,导致芯片无法正常工作。

显控终端的电源管理由两部分组成,设计如图2所示。第一部分是输入滤波和短路保护电路,雷达系统通过VPX连接器提供直流+12 V和+5 V电压输入,为了提高模块的电磁兼容性,在每路电源输入端口处增加三端滤波器进行电源滤波,然后经过保险丝以防止模块内部电源输入端出现短路保护时拖垮系统电源。为了保证电源短路时保险丝迅速做出反应而又不发生误保护情况,选择的保险丝额定电流为模块电源稳态电流的3~4倍。第二部分是电压二次转换电路,+12 V电压经滤波保护后提供给CPU子卡,+5 V电压再经过DC/DC、LDO二次转换后产生+1.0 V、+1.5 V、+2.5 V和+3.3 V电压,提供给Tsi721芯片和外围电路、电子硬盘、USB鼠标键盘使用滤波、短波保护之后的+5 V电压。

图2 电源管理设计框图

2.3 通信接口电路

CPU子卡只具有PCIe接口而不兼容RapidIO,显控终端使用PCIe to RapidIO桥芯片Tsi721完成PCIe与RapidIO总线间之间的协议转换,Tsi721能够将数据传输从RapidIO总线转换到PCIe总线,或相反,并保证数据传输的流畅性、高效性和可靠性[2]。对于CPU,Tsi721只是一个普通的PCIe设备,对于RapidIO网络来说,Tsi721也只是一个拥有一个ID号的RapidIO设备节点。显控终端的RapidIO总线采用1×4的物理连接,速率2.5 GHz,提供8 Gbps的有效传输带宽。Tsi721需要100 MHz的差分时钟输入,因此在外部接入100 MHz的晶振。需要注意的是,PCIe与RapidIO总线速率较高,信号发送端和接收端分别需要端接一个100 nF的电容,隔离直流分量进行AC耦合,PCB布线时需要等长以及隔离处理,保证其信号完整性。

RS422、RS232和CAN接口用于低速设备的通信控制,芯片CP2105完成USB协议转换,然后选用深圳国微的SM3490和SM3030驱动器扩展RS422及RS232接口。MCU芯片C8051F00自带有CAN控制接口,选用TI公司的SN65HVD230Q作为收发器。

CPU子卡集成了千兆网卡,显控载板使用隔离变压器HX5008NL进行信号转换,就构成了10 M/100 M/1 000 M自适应以太网。

2.4 人机交互电路

人机交互包括键盘、鼠标信息输入以及显示输出,CPU子卡集成了USB host和USB otg控制器,显控载板将USB信号直接经VPX连接器引出,实现外接键盘、鼠标。

显控终端输出LVDS/24Bit视频信号,分辨率最高可达1 366×768,相对原VGA标准,由于采用差分信号传输,具有更好的抗干扰性能,传输线缆长度对信号影响较小,可以实现远距离的图像数据传输。

3 终端软件设计

显控终端软件总体框图如3所示,由操作系统、驱动程序、软件开发工具和应用软件等部分组成。

图3 显控终端软件总体框架

3.1 操作系统选择

由于Linux系统具有安全性高、开放源代码、实时性高等优点,已经在军事和民用电子设备中得到广泛应用,显控终端选用基于Linux内核的Centos 7桌面操作系统,在此平台下开发驱动及应用软件。

3.2 驱动设计

Linux内核已集成了以太网、串口、CAN总线等接口的驱动程序,本文把Tsi721桥芯片驱动设计为字符驱动,借助Linux字符设备的驱动模型将RapidIO端口虚拟为一个字符设备,驱动程序中实现open、close、read、write和ioctl等标准系统调用函数,应用软件通过字符设备文件(比如/dev/xyz)来访问对应的硬件设备[3]。Tsi721桥芯片驱动实现流程如图4所示。

图4 Tsi721桥芯片驱动实现流程

驱动加载的步骤主要如图4所示,tsi721_probe函数先根据Tsi721芯片的设备标识Device ID和供应商标识Vendor ID遍历内核中PCIE设备链表,一一进行匹配;匹配之后从pci_device结构中获取内核,分配给Tsi721芯片设备的资源;然后调用函数pci_enable_device,把Tsi721配置空间的Command域的bit 0和bit 1置成1,从而达到开启该PCIE设备的目的;再调用函数pci_request_regions,通知内核该设备对应的IO端口和内存资源已经使用,其它的PCIE设备不能再使用这个区域;调用pci_ioremap_bar,把刚刚申请到的物理内存映射成为虚拟内存以供驱动访问;再根据分配的中断号调用函数reques_irq,挂载中断服务程序;最后调用函数pci_alloc_consistent,申请DMA缓存。

内核集成的RapidIO子系统框架实现协议的封装、枚举等工作,将Tsi721虚拟为RapidIO网络中的一个节点。Tsi721字符设备的初始化步骤如图4所示,先调用cdev_init函数,初始化一个字符设备tsi721_cdev,并注册其操作函数结构体tsi721_file_operations;然后调用alloc_chrdev_region,为该字符设备动态分配“主设备号”和“次设备号”;再调用cdev_add函数,向内核中增加该字符设备tsi721_cdev,驱动最后调用class_create()函数和device_create()函数,在sysfs中注册该字符设备自己的class以及在/dev目录下创建一个tsi721的设备文件[4];当系统启动时,udev能自动产生相应的设备节点/dev/tsi721_rio。

3.3 软件工具移植

考虑到二次雷达显控终端应用软件的稳定性、可靠性、可移植性和实用性,开发环境IDE选用跨平台的Qt creator,应用软件开发选择Qt,数据库软件选择MySQL,采用Qt图形工具的面向对象编程方法,把各个功能的实现合理地分配到不同的类中[5],做到显控软件模块清晰,人机界面整洁、直观、逼真。软件工具移植流程如图5所示。

图5 软件工具移植流程图

先使用默认参数安装Qt creator,再根据自己的硬件特性选取相应的Qt配置参数,配置并安装Qt至/usr/local/目录下;然后安装数据库软件MySQL,最后针对MySQL编译QT中的插件库。

3.4 人机界面设计

在实际应用中,二次雷达显控终端通过RapidIO总线接收信号处理机输出的目标信息并显示,供雷达操作员观察;接收雷达操作员的控制输入,并且传送控制命令,实现操作员对雷达工作模式的切换和对雷达工作状态的监控[6]。显控终端软件利用Qt和MySQL实现后,运行速度快,稳定性高,显示画面美观、逼真,操作便捷。终端主界面画面如图6所示。

图6 显示终端主界面图

4 性能测试与分析

4.1 数据吞吐速率测试

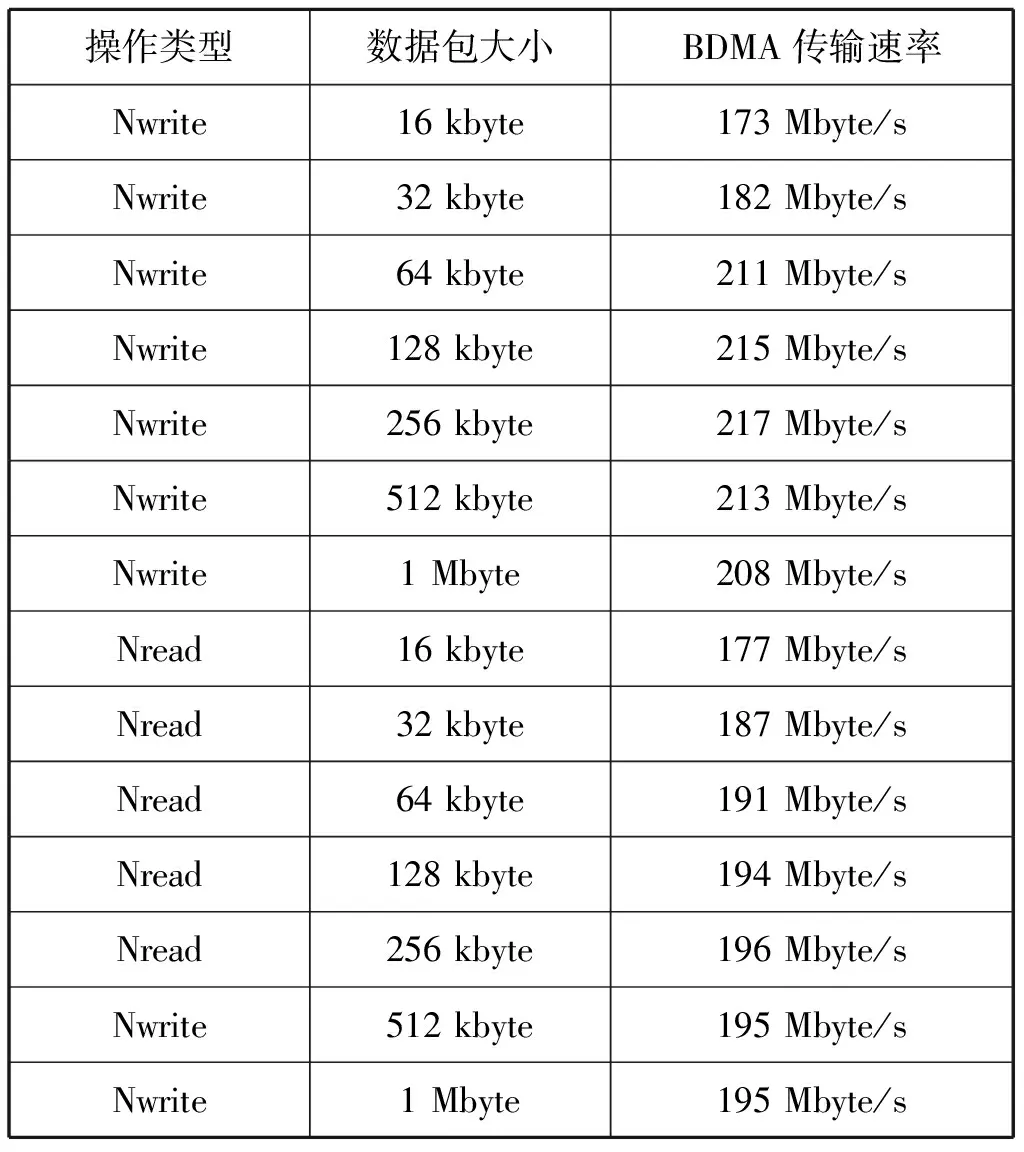

在二次雷达航迹显示的过程中,信号处理机和显示终端之间需要进行大数据的交互。数据传输吞吐的时间损耗是一个关键指标。因此,使用RapidIO高速接口着重对显控终端大数据搬移时间进行了测试。测试结果如表1所示。

通过测试发现,负载数据低于512 kbyte时,数据包越小则传输的速率越慢,而数据包大小增大到一定阶段时,则传输的速率变化不大。因此,在实际软件设计过程中,应尽量减少小块数据的传输,提供雷达系统数据实时处理能力。

表1 性能对比

4.2 功耗测试

当显控终端的四核CPU满负载运行时,平均功耗约为12 W,通过冷板被动传导散热方式,即可正常工作。

5 结束语

本文以模块化思想设计并实现了一款集成显示、控制等多种功能于一身的新型二次雷达显控终端,具有高性能、低功耗、可扩展性等优点。软件设计不仅充分满足了二次雷达显控终端的功能性,并充分考虑了雷达显控终端的人性化设计,具有友好、美观的人机界面。经过测试,此显控终端已经成功应用于某型雷达设备中,取得了良好的经济、社会效益。