多芯片组件电路封装的频域分析和仿真*

2019-03-05畅艺峰邹旭军李智荣雷群龙

畅艺峰,邹旭军,董 戴,李智荣,雷群龙

(深圳市中航比特通讯技术有限公司 专用通讯承载网络重点实验室,广东 深圳 518000)

0 引 言

多芯片组件布局布线算法一直是业界研究的主题之一[1-3],也取得了一定进展。本文通过对具体电路进行MCM设计和预仿真,制定布局布线策略,然后对该电路进行MCM封装。最后,仿真结果与设计结果吻合,达到了预期。

1 传输线的频域分析

以一小段传输线为例,用集中参数模型来描述,如图1所示。

图1 短传输线的集总参数模型

根据克希霍夫定律,得:

由式(1)和式(2)可得到传输线上每点的电压和电流。

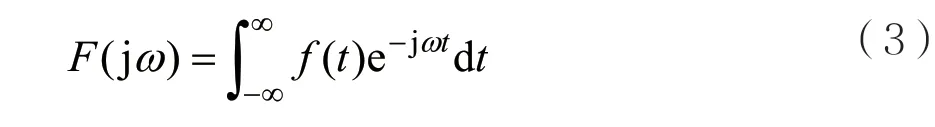

通过傅立叶变换:

式(1)、式(2)可变为式(4)、式(5):

式中V、I是υ、i的傅立叶变换形式,消去式(4)、(5)中的I,可得到二阶微分方程:

它的解为:

式中:

A、B、γ是ω的函数。

时域电压可由式(9)的傅立叶逆变换得到,如式(10)所示:

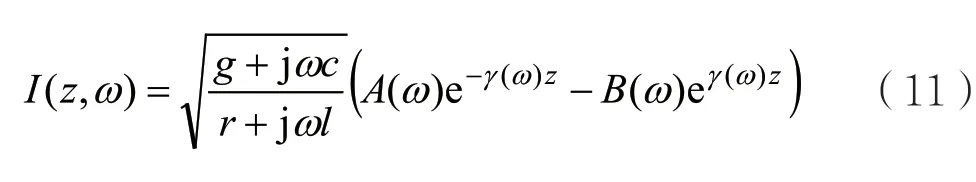

特性阻抗通过求解式(4)的I得到,将式(7)的电压代入可得到:

所以,损耗传输线特性阻抗为:

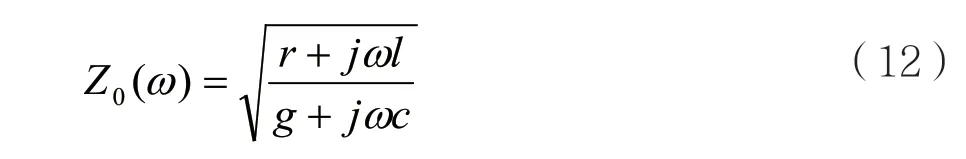

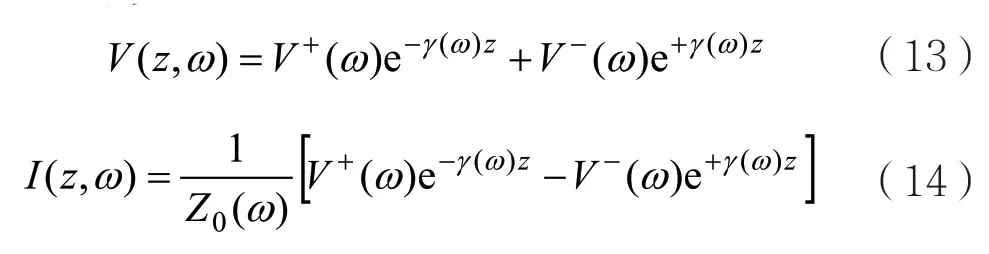

则式(7)、式(10)的电压和电流表达式分别变为:

式(13)和式(14)正是解决电路问题包括传输线问题的出发点。

2 电路的设计及MCM封装

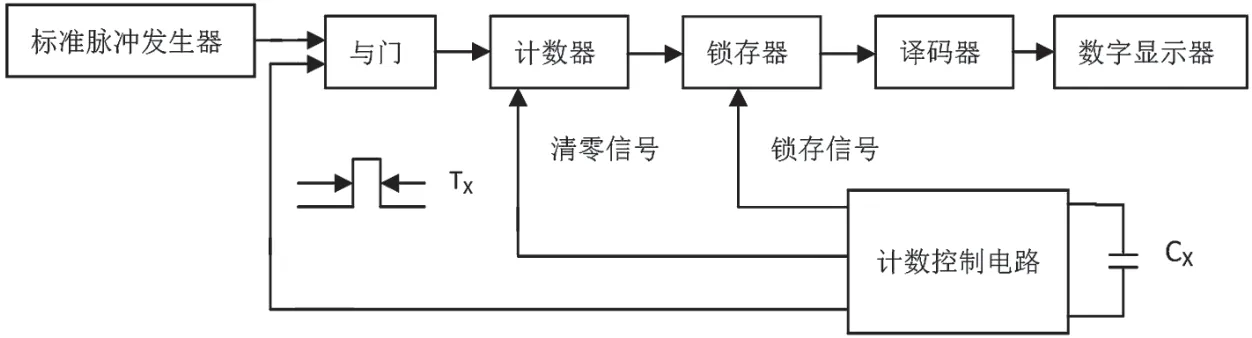

本文采用的具体电路,如图2所示。

图2 本文采用的大电容数显式测量方案

经推导得:

若取UR1=VC/5,UR2=VC/3,代入式(17)得:

由此可见,Tx不仅与三极管得饱和压降VCES无关,而且与电源电压VCC无关,这样就不会因VCES和VCC变动引起误差。

计数器与触发器所需要的清零信号是反相的。根据设计要求,清零信号的脉冲宽度应比清零端的延迟时间大,以保证有效的清零;时钟脉冲的宽度应比时钟脉冲周期小,以免引起误差。由于对脉冲宽度的稳定性要求不高,因此以反相器为主构成清零信号单稳电路,这个电路的时间常数RC应比输入电压的周期时间小。当输入一个方波脉冲时,两个输出端一个为高电平即为逻辑“1”,一个为低电平即为逻辑“0”。VR有时为负值,在每次方波的上升沿或者下降沿作用时,清零作用发生,可实现电路功能。由于该电路超过CMOS反相器的电源电压范围,因此需增加限流保护电阻R´,方可满足设计要求。

3 MCM封装的频域仿真

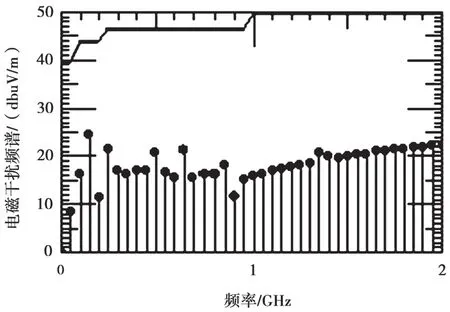

图3为MCM封装后的电路仿真结果。

图3 电磁干扰仿真结果

为更直观地观察EMI强度的变化,图3为上述仿真结果对应的频谱图,其中点线表示允许的极限。可以看出,图4波形的EMI强度(实线)均在限制(点线)以下。

图4 电磁干扰强度

图5为对应的眼图,也与上述分析结果保持一致。由上述频域和时域仿真结果可以看出,本文的MCM电路封装设计满足实际要求。目前,最后的工艺版图已完成设计开发,相关产品也已有流片。

图5 电磁干扰眼图

4 结 语

本文利用MCM技术进行设计、仿真和高密度封装,时域和频域仿真结果表明,所设计的电容显示电路满足实际设计要求,对MCM技术的应用具有一定的借鉴意义。