无片上电感的低功耗高线性度CMOS混频器

2019-02-25文枭鹏刘艳艳

文枭鹏,张 为,刘艳艳

(1.天津大学 微电子学院,天津 300072;2.南开大学 电子信息与光学工程学院,天津 300071)

0 引 言

以无线传感器网络为支撑的物联网技术在近几年吸引了学术界和工业界的广泛关注,根据预测,到2020年,物联网市场规模将超过1 500亿美元,因此物联网被认为是半导体产业的下一个增长引擎。无线传感网络节点需要大规模分布在森林、河流湖泊、建筑内部、以及可穿戴设备等环境中,需要满足小尺寸、低成本、低功耗等关键指标。尤其是功耗问题,由于工作在特殊环境中,电池无法更换,所以降低功耗、延长电池使用寿命正成为物联网大规模部署的重大挑战。对于无线传感器网络节点,无线通信系统消耗了大量的功耗[1],其中,相对于基带电路,射频前端占无线通信系统功耗的比重较大。因此,低功耗射频技术逐渐成为射频电路设计的关键。

在射频前端电路中,混频器(mixer)实现射频信号和中频信号的转换,通常级联在低噪声放大器之后。低噪声放大器作为射频前端电路的第一级,通常能够实现很小的噪声系数和较大的增益,降低了后级混频器对系统噪声的贡献,同时也增大了混频器的线性工作压力。因此,在混频器电路设计中,线性度是比噪声更值得关注的性能[2]。故而设计适用于无线传感网络的低功耗、高线性度的混频器是集成电路和物联网领域的研究热点和难点。

输入三阶交调点(input third-order intercept point,IIP3)是衡量混频器线性度的一项重要指标。国内外研究人员在提高混频器线性度方面已经做出了很多努力。文献[3]采用多栅晶体管技术,文献[4]采用负阻抗技术,文献[5]采用二阶交调注入技术,但这几种方法都需要增加额外的晶体管,增加了电路的功耗;文献[6]使用LC谐振技术,但较大的片上电感增大了芯片的面积。本文基于以上研究成果,设计了一种低功耗、高线性度吉尔伯特混频器。

1 混频器设计与分析

1.1 电路结构

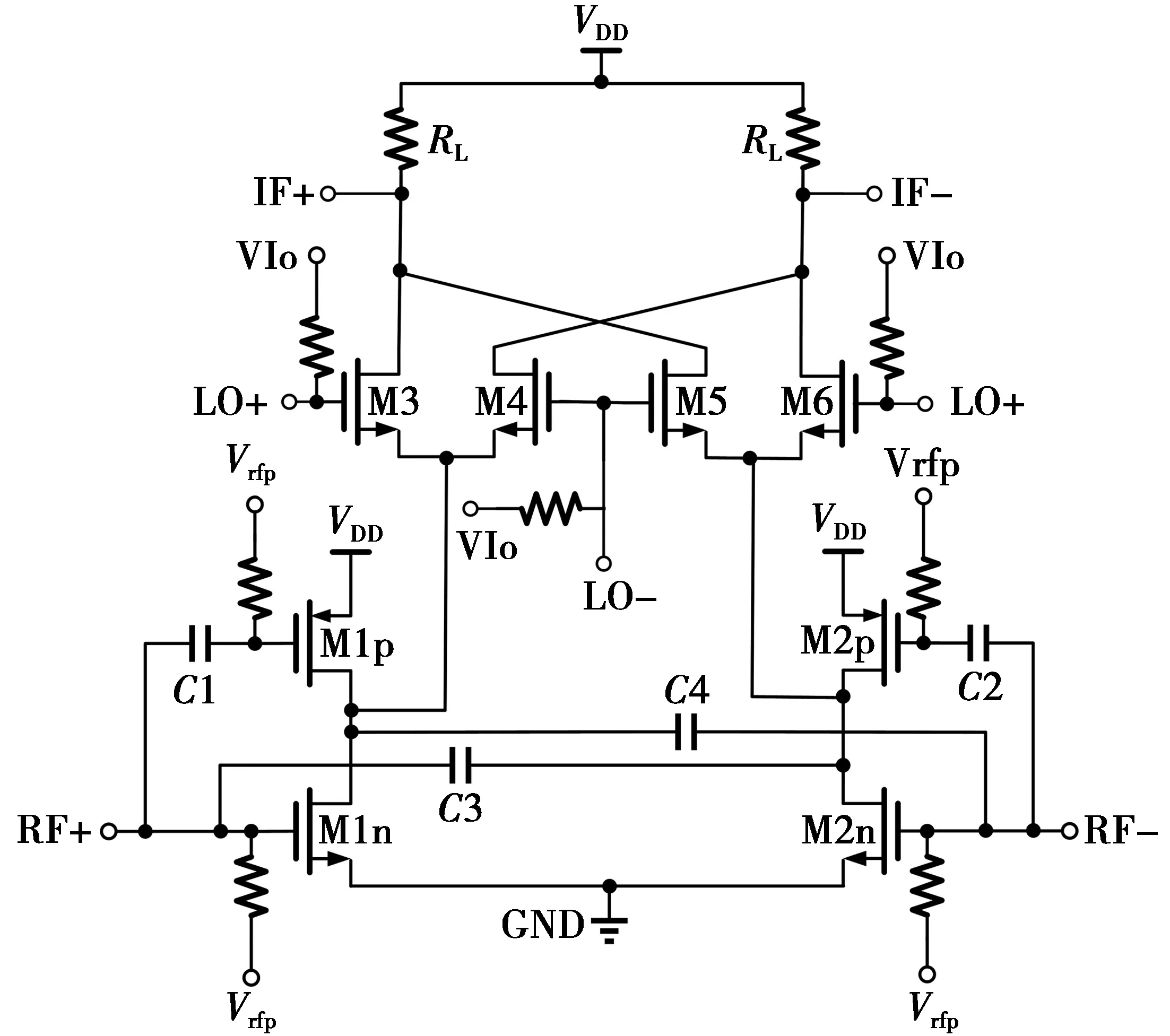

传统的双平衡吉尔伯特混频器由于其优越的端口隔离性能,在无线通信系统中广泛应用。其结构如图1所示,电路由跨导级(M1~M2)、开关级(M3~M6)和负载级RL组成。

本文在传统吉尔伯特混频器基础上,以低功耗、高线性度为目标对电路进行了优化设计:①跨导级晶体管工作在亚阈值区;②在跨导级(M1n与M1p,M2n与M2p)采用互补结构,即射频信号从PMOS与NMOS并联输入;③在跨导管的漏极和互补支路跨导管的栅极之间插入耦合电容C3,C4,在插入节点形成负阻抗[2]。电路结构如图2所示。

图1 传统吉尔伯特混频器电路图Fig.1 Conventional Gilbert mixer circuit diagram

图2 本文提出的混频器电路Fig.2 Proposed mixer circuit diagram

1.2 低功耗设计

为降低混频器功耗,本文提出的混频器工作电压为1 V,即通过低电压的工作方式降低直流功耗。

在低功耗混频器中,为降低直流功耗,往往将晶体管偏置在亚阈值区,为保证晶体管仍有较大的跨导,就需要增大宽长比。因此,在开关管源极形成较大的寄生电容,它的存在恶化了混频器的线性度。本文提出的混频器跨导级偏置在亚阈值区,为降低寄生电容的影响,在电路中增加了交叉耦合电容,在改善线性度的同时并未增加额外功耗。

此外,为解决低功耗带来的性能损耗问题,本文提出在跨导级采用PMOS/NMOS互补结构,这种结构的改进效果包括如下3个方面:①在功耗和增益方面,这是一种电流复用的跨导提升结构,即输入信号通过NMOS放大,同时也通过PMOS放大,在不增大晶体管电流的情况下,提高了转换增益;②在噪声方面,这是一种电流注入结构,PMOS管的直流电流注入NMOS管,减小了开关级的直流电流,从而减少了开关级噪声的贡献[7];③在线性度方面,这是改进的导数叠加(derivative superposition, DS)结构,提高了IIP3。即只增加一个晶体管,便同时实现了电流复用、跨导提升、电流注入以及导数叠加,从功耗、增益、噪声、线性度4个不同的方面优化了电路性能。

1.3 线性度优化设计

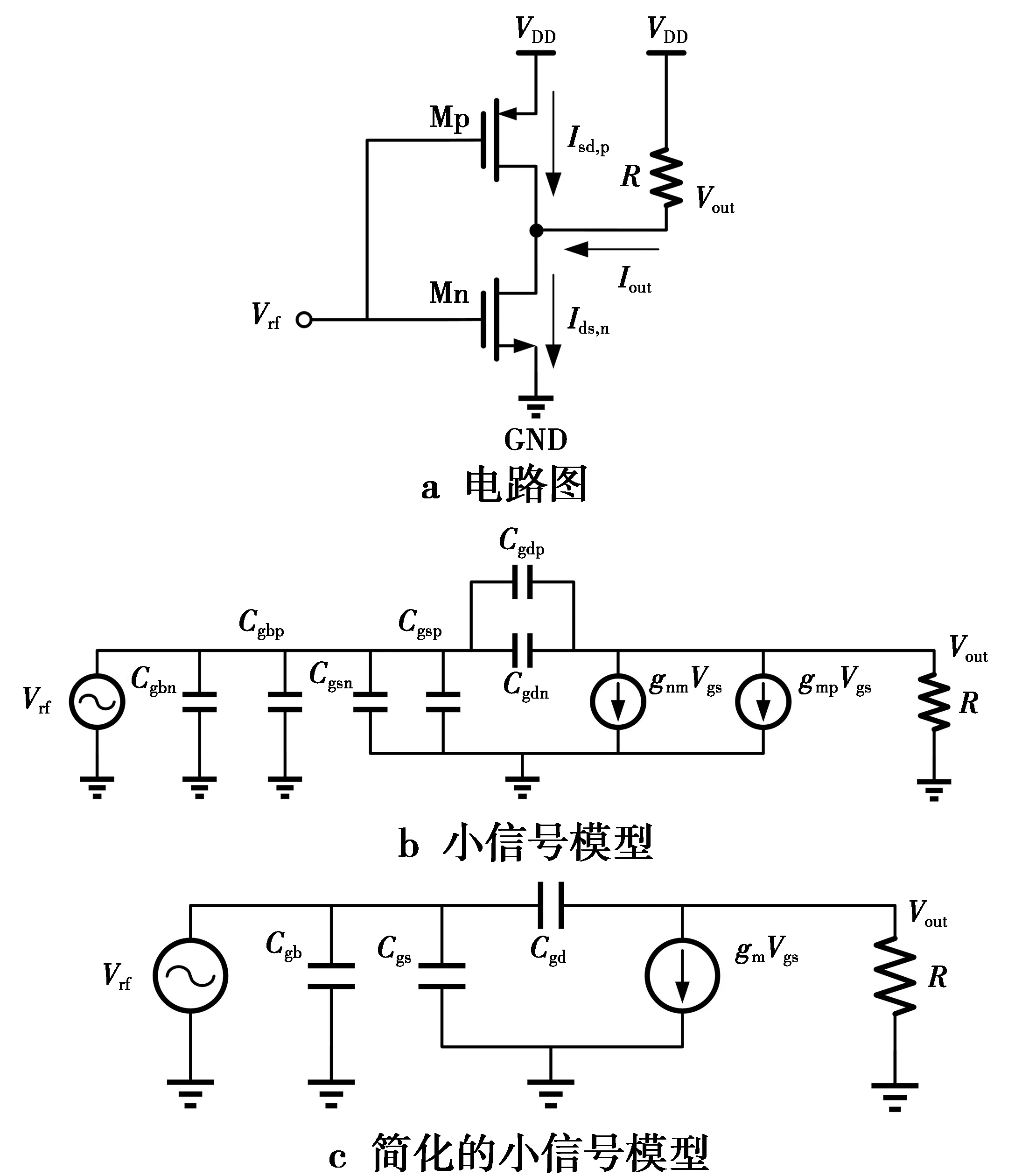

为方便分析,首先介绍混频器的小信号电路图。PMOS管和NMOS管的互补结构如图3a所示,其小信号模型如图3b所示。PMOS管和NMOS管的小信号模型并无差别,因此,在图3c中对跨导级的小信号模型做出简化。其中,gm=gmn+gmp。

图3 互补结构Fig.3 Complementary structure

经过简化之后的混频器小信号电路如图4a所示。开关管设定可以理想导通和关断,因此从源极看进去的阻抗是1/gm3~1/gm6,VX,-VX分别是开关管M3,M6源极处的小信号电压,CP是开关管源极寄生电容。因电路的对称性,故对其半边等效电路进行分析,如图4b所示。其中,Z1,Z2,Z3分别是从跨导管栅极、源极、漏极看到的阻抗。

图4 本文提出的混频器小信号电路图及其等效半边电路Fig.4 Small-signal circuit diagram and its equivalenthalf-circuit of the proposed mixer

跨导管小信号漏电流ids与栅源电压vgs的Taylor展开关系为(只展开至三阶项)

…

(1)

(2)

(2)式中:RS是源阻抗;|A1(ω)|是从vrf到vgs的传输函数;|H(ω)|是从vrf到ids的三阶非线性传输函数;

Δω=ω1-ω2

(3)

|ε(Δω,2ω)|=g3-goB

(4)

(5)

g(ω)=

(6)

Z(ω)=Z2(ω)+jωCgd1[Z1(ω)Z2(ω)+

Z1(ω)Z3(ω)+Z2(ω)Z3(ω)]

(7)

Z1~Z3根据不同电路的实际情况推导,本文的电路可由文献[2]的方法推导出

Z1(ω)=(jωCgb1+1/ZC1)-1

(8)

Z2(ω)=0

(9)

Z3(ω)=(gm3+jωC+Y)-1

(10)

(8)~(10)式中:

(11)

(12)

(13)

由(2)式的分母项可知,若想提高IIP3,可以通过减小|ε(Δω,2ω)|来实现。(4)式指出了三阶非线性的来源,一是源漏电流的三阶非线性,二是由于二次谐波和一次谐波分量相互作用产生的三阶非线性干扰。因此,可以通过减小跨导管三阶跨导,同时改变各端阻抗以减小二次谐波的影响。

通过(8)~(13)式可知,通过合理地选择耦合电容C3,C4的值,可以改变Z1和Z3的大小,实现对寄生电容CP的部分抵消,即对于寄生电容起到了负阻抗的作用,从而减小二次谐波对混频器三阶非线性的作用。

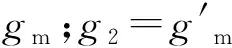

另一方面,根据(4)式对三阶非线性来源的分析,本文提出的互补跨导结构利用导数叠加技术,分别对二阶、三阶跨导进行抵消,实现了从上述两方面提高IIP3。根据文献[9]的指导方法可得,互补结构的输出交流电流iout对小信号输入电压vrf的三阶展开式为

(14)

综上所述,本文提出的混频器利用改善偏置的PMOS和NMOS导数叠加技术,并使用交叉电容耦合,有效地减小了二阶、三阶非线性,从而在降低功耗的同时改善了线性度。

图5 PMOS与NMOS的,模拟图Fig.5 Simulated and curves of PMOS and NMOS

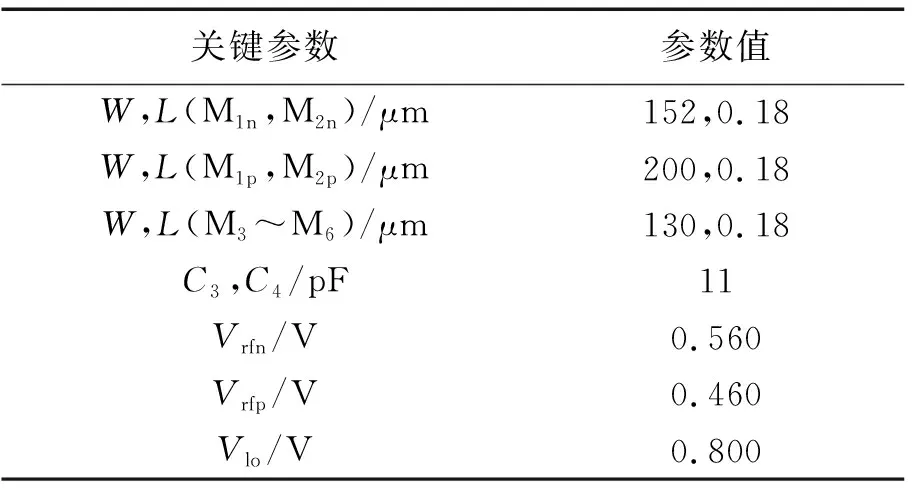

关键参数参数值W,L(M1n,M2n)/μm152,0.18W,L(M1p,M2p)/μm200,0.18W,L(M3~M6)/μm130,0.18C3,C4/pF11Vrfn/V0.560Vrfp/V0.460Vlo/V0.800

2 仿真结果

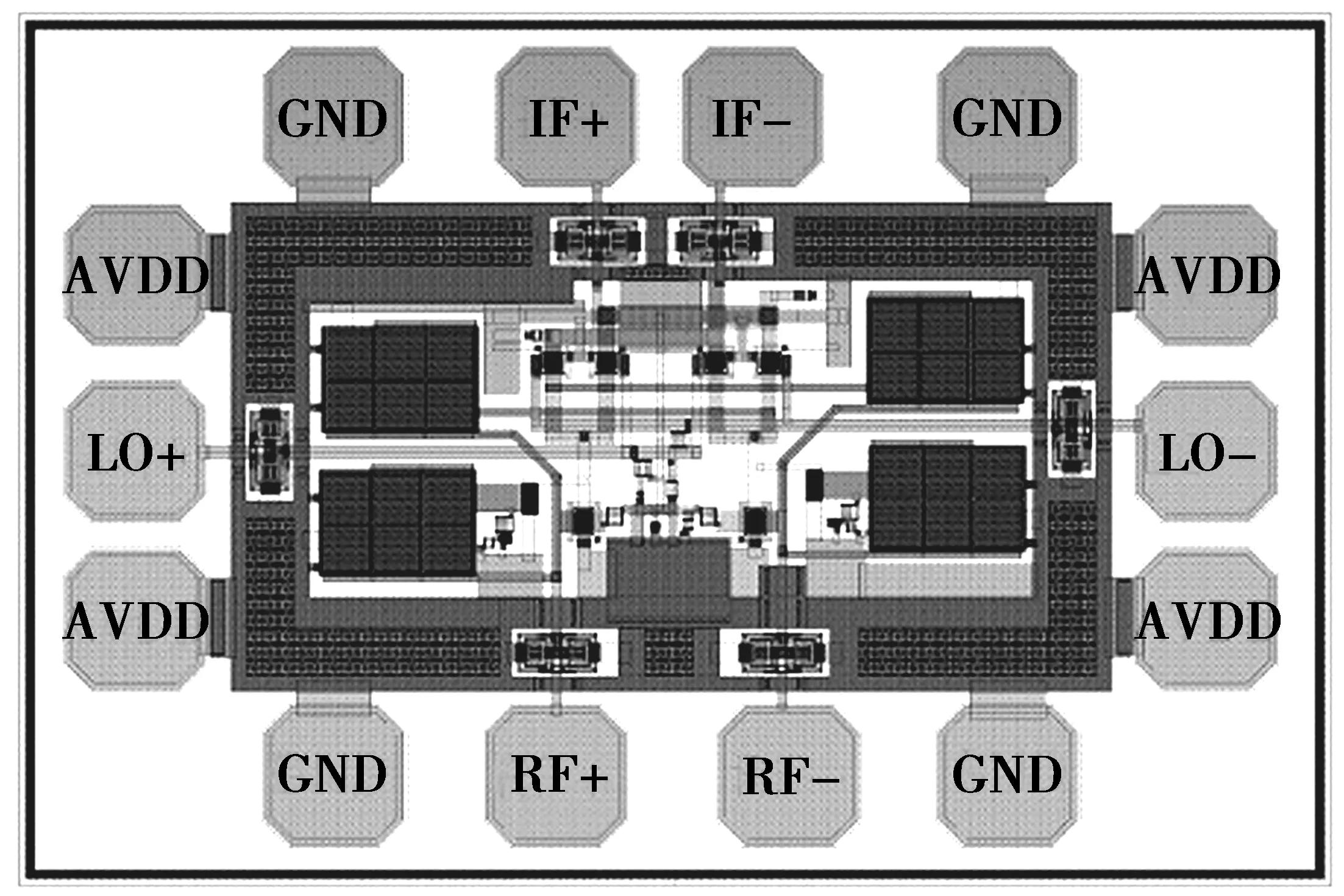

本文提出的混频器版图如图6所示,在所有的端口添加了静电保护电路,混频器核心电路尺寸为460 μm×190 μm。采用HHNEC 0.18 μm BiCMOS工艺,使用Cadence Spectre RF仿真器进行了后仿真。射频频率fRF为0.4~3 GHz,本振频率fLO为fRF-0.02 GHz,即在可变本振频率的情况下,固定中频频率为20 MHz。仿真时本振输入功率PLO=1 dBm。

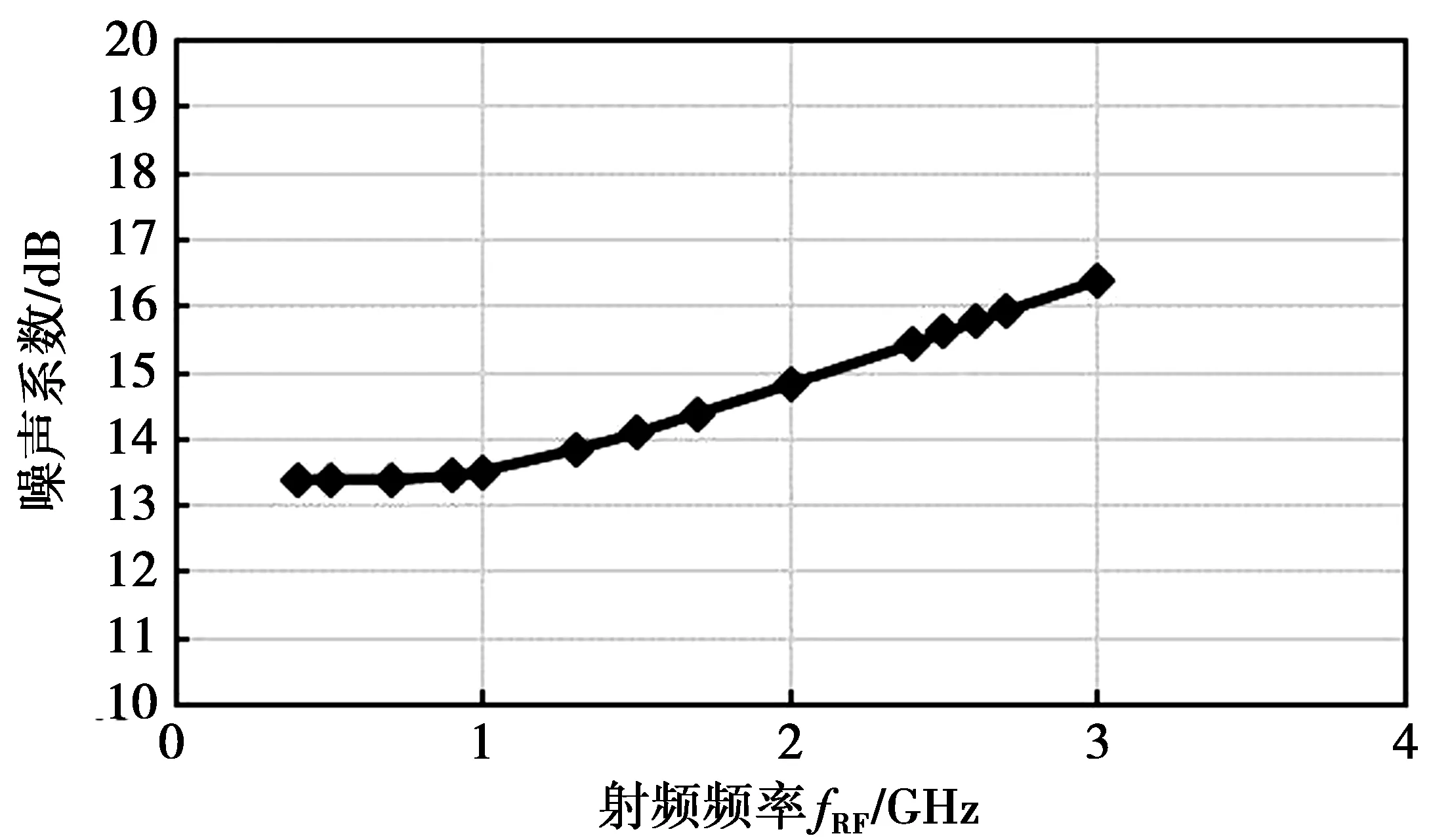

本文提出的混频器主要面向2.4 GHz频率的物联网低功耗工作场景。图7为本文中混频器转换增益后仿真结果,可以看出混频器在射频频率为0.4~3 GHz时实现了6.2~7.6 dB的转换增益,其中,在2.4 GHz频率下转换增益为7.33 dB。图8为噪声系数后仿真图,可以看出在射频频率0.4~3 GHz噪声系数为13.37~16.40 dB,在2.4 GHz频率下噪声系数为15.45 dB,该指标能够满足一般低功耗场景下的噪声系数要求。该电路的噪声系数较大,其原因有:①跨导级使用PMOS/NMOS互补结构,虽减小了开关管的噪声,但由于PMOS管的使用,引入了额外的沟道电阻热噪声;②跨导管偏置在亚阈值区,其较大的寄生电容增加了混频器的噪声系数。上文提到,混频器线性度的指标相比噪声更为关键,故在设计中着重考虑低功耗情况下线性度的改善,牺牲了部分噪声性能。

图6 本文提出的混频器版图Fig.6 Layout of the proposed mixer

图7 转换增益仿真结果Fig.7 Simulated CG of the proposed mixer versus RF frequency

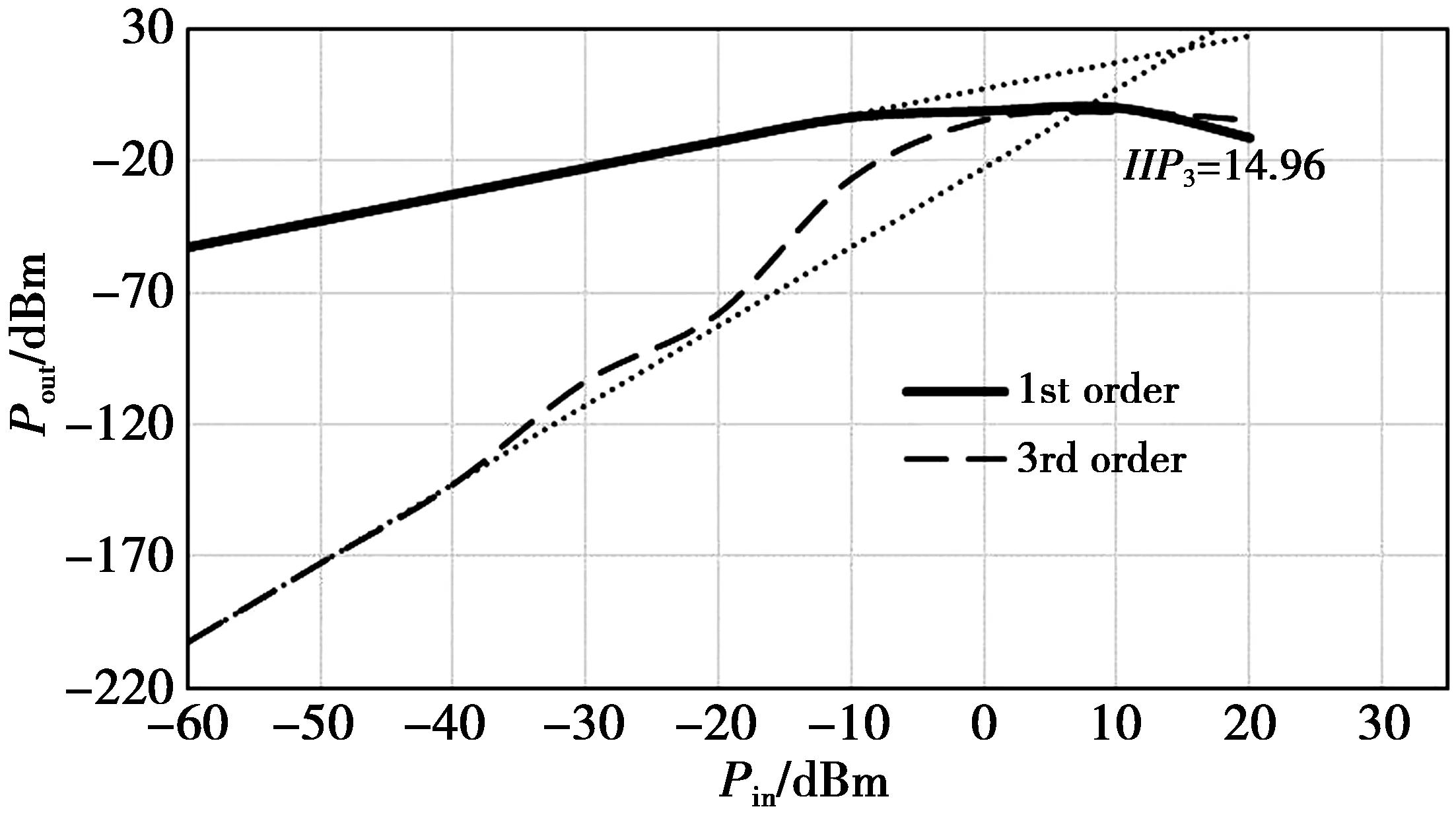

图9为在射频频率为2.4 GHz,本振频率为2.38 GHz情况下IIP3后仿真结果,可以看出IIP3为14.96 dBm,由此可知该混频器具有很好的线性度。同时,该混频器电源电压为1 V,直流功耗仅为1.8 mW。

图8 噪声系数仿真结果Fig.8 Simulated NF of the proposed mixer versus RF frequency

图9 2.4 GHz频率IIP3仿真结果Fig.9 Simulated IIP3 of the proposed mixer with fRF=2.4 GHz

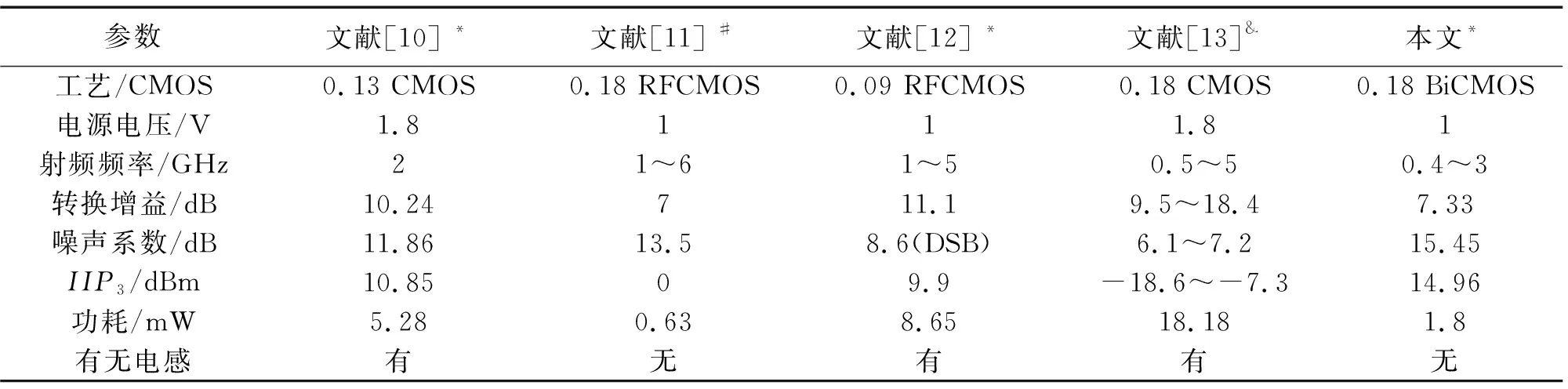

表2为本文中混频器与近几年来报道的几种性能优良的混频器的主要性能参数对比,与文献[10]相比,本文提出的混频器并未使用面积较大的电感,在面积、功耗、线性度方面性能优越;与文献[11]相比,本文的混频器同样是无电感结构,并且在增益、噪声系数相比拟的情况下,IIP3高出约14.96 dBm,即线性度指标上表现突出;与文献[12-13]相比,本文的混频器在线性度、功耗、面积上优势明显。综上,可以看出,本文中的混频器实现了低功耗、高线性度,达到了良好的总体性能。

表2 本文与其他文献的参数对比Tab.2 Performance comparison

*后仿真结果 #测试结果 &前仿真结果 DSB:双边带噪声

3 结 论

本文针对物联网低功耗应用场景,在传统吉尔伯特混频器电路的基础上,采用了低电压、亚阈值等低功耗技术;跨导级使用PMOS和NMOS互补结构,利用导数叠加技术,降低了二阶、三阶跨导的影响,并通过交叉电容耦合形成负阻抗,抵消了寄生电容的非线性影响,实现了低功耗情况下的线性度改善。电路后仿真结果与近几年文献对比表明,该混频器在2.4 GHz频率下获得了优良的功耗、线性度性能。