基于国产FPGA的高速SRIO接口设计与实现*

2019-01-23于东英康令州

于东英,陈 俊,康令州

(中国电子科技集团公司第三十研究所,四川 成都 610041)

0 引 言

2015年5月国务院印发《中国制造2025》,是中国政府实施制造强国战略第一个十年行动纲领。在该行动纲领的指导下,为了提高国家综合国力,成功实现各个产业升级转型,创新与自主发展成为其核心理念之一。

2018年上半年,美国商务部发布对中兴通信的禁止出口令。该消息一石激起千层浪,对所有国人敲响了警钟,同时明白在很多高科技行业尤其在有“工业石油”之称的芯片方面,必须拥有自主研发的产品,否则将会受制于人。如果不是在中国自主研发的芯片上进行开发和应用,取得的一切成果就如一座建立在沙子上的城堡。

在提倡创新和自主发展的大背景下,在外部环境瞬息万变的情况下,为了行业长远和健康的发展,必须在芯片领域坚持自主研发和应用。

本文主要是在国产自主研发的FPGA平台上实现高速数据通信接口SRIO的设计与验证。

1 国产FPGA平台

本文使用的FPGA平台[1]是深圳市紫光同创电子有限公司推出的全新高性能FPGA,具有完全自主产权的体系结构与自主开发套件。

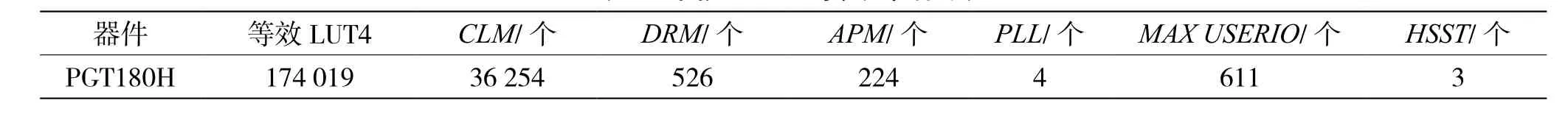

该芯片包括创新的可配置逻辑单元(CLM)、专用的18 kB存储单元(DRM)、算术处理单元(APM)、高速串行接口模块(HSST)、多功能高性能IO以及丰富的片上时钟资源等。该芯片的详细列表如表1所示。

表1 国产FPGA资源详细列表

该国产FPGA芯片内置高速串行模块(HSST),数据传输速率可达6.375 Gb/s,可以灵活运用于各种串行协议标准。本文通过配置FPGA内置的HSST接口作为SRIO接口设计的硬件接口基础。

2 SRIO接口简介

SRIO接口是一个开放式互联体系结构。该接口类型基于包交换的新一代高速互联技术,具有高可靠性、低时延、低管脚数、低传输开销以及接口频率和端口宽度可升级等优点,解决了嵌入式系统内串行数据平面连接、DSP、FPGA与串行背板之间的高速串行数据传输稳定性和时效性的问题。

SRIO协议体系包含了3层结构(传输层、逻辑层和物理层)[2],各个协议层之间的详细关系如图1所示。

3 逻辑设计与实现

图1 SRIO协议体系结构

协议体系中3个结构层详细定义了串行数据传输过程中涉及到的传输机制和传输特性,详细定义范围如表2所示。

表2 国产SRIO协议中层功能定义范围列表

在国产FPGA平台的基础上,使用FPGA内置的HSST模块与厂家提供的SRIO core,通过逻辑模拟IPcore的读写时序(与xilinx的rapidio IP core的用户侧时序相同)[3],实现了速率为2.5 Gb/s,接口模式为1X的SRIO接口设计和验证。

3.1 SRIO core简介

对于用户使用来说,SRIO core主要分为4个部分。

发起模块:主动发起事务请求以及接收对端接收模块响应本端发起模块的事物请求。

接收模块:接收对端发起模块发起的事物请求,并根据请求作出相应的响应。

时钟模块:参考SRIO core输出的时钟作为整个设计的参考时钟。

复位模块:通过对系统时钟以及一些配置标志信号进行综合处理,最终形成SRIO core的复位信号。

3.2 设计方案

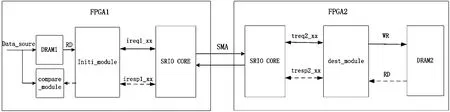

FPGA内部设计主要包括三个部分[4]:SRIO core、initial_module和 dest_module。 在 设 计 SRIO接口时,需要注意硬件设计必须提供125 MHz的差分时钟给HSST参考时钟接口。模块之间的互联关系如图2所示。

SRIO core:SRIO core实现了协议中规定的3个结构层,用户侧接口部分主要包括用户接口(user interface)、链路接口(link interface)和管理接口(Maintenance Interface)[2]。用户在使用SRIO core传输数据时主要使用的是用户接口。

用户接口主要包括四个部分:发起方请求事务(ireq_xx)、发起方响应事务(iresp_xx)、目标方发起事务(treq_xx)与目标方响应事务(tresp_xx)。

图2 FPGA内部设计

用户可以通过用户侧接口中相应的控制和标志信号实现特定的数据长度、发送方信息、目标方信息等。

Initi_module模块:该模块的功能是通过逻辑设计实现SRIO core的发起方请求事务与响应事务相关的控制与标志信号时序。

dest_module模块:该模块的功能是通过逻辑设计实现SRIO core的目标方请求事务与响应事务相关的控制与标志信号时序。

3.3 设计细节

SRIO core用户接口发起方与接收方的信号接口完全独立。验证时采用两块板卡进行通信,板卡之间通过SMA接口进行互联。为了设计验证,在FPGA内部添加了DRAM模块用于存放需要交互的数据,compare_module用于发起方接收和发送数据的比对。SRIO接口通信数据的数据流向如图3所示。

图3 SRIO接口数据流

SRIO core包括数据处理流程如下。

用户可以通过ireq_byte_count信号控制传输的数据长度,通过ireq_addr信号控制数据存储到DRAM2中的目的地址。下面以FPGA1中的initi_module发起写事务请求和读事务请求,FPGA2中的dest_module响应其读写事务请求。

Initi_module从DRAM1中读取需要发送的数据,开始进行写事件请求,通过控制ireq1_sof_n(开始标志)、ireq1_eof_n(结束标志)、ireq1_vld_n(有效标志)信号等信号,检测SRIO core的ireq1_rdy_n(备妥信号)有效性,将数据发送到SRIO core,经过SRIO core处理的数据通过SMA接口发送到FPGA2内的SRIO core。经过IP core处理后的数据通过treq2_xx信号将接收到的数据按照ireq1_addr设定的目的地址存储到DRAM2中。

Initi_module完成了写事件请求后,将执行读事件请求。dest_module接收到读请求后,从DRAM2中读取req1_addr设定的目的地址上的数据,并开始进行读响应,通过控制tresp2_sof_n(开始标志)、tresp2_eof_n(结束标志)、tresp2_vld_n(有效标志)信号等信号,检测SRIO core的tresp2_rdy_n(备妥信号)有效性,将数据发送到SRIO core。经过SRIO core处理的数据通过SMA接口发送到FPGA1内的SRIO core,经过IP core处理后的数据通过iresp2_xx信号接收有效数据,并将接收到到的数据与发送的数据进行比对。

上述过程是FPGA1内Initi_module发起事情请求,FPGA2内的dest_module响应请求;反之,数据流向类似。

3.4 验证结果

本文中接口验证过程采用国产FPGA生成的SRIO通过SMA接口连线与xlinx的开发板SP605进行互通。该开发板上搭载一片XC6SLX45T-3FGG484 FPGA。将SP605作为第三方验证国产FPGA中SRIO接口设计的正确性。

SRIO接口的传输类型中经常用到的模式有NWRITE和NREAD(不要求接收端响应)、NWRITE_R(要求接收端响应)、SWRITE(流写操作,数据长度必须是8的整数倍)等。这些传输类型通过控制信号ftype与ttype进行选择。

本文中用到的示例采用的模式为工程实例中较常用的NWRITE(ftype=5,ttype=4)和NREAD(ftype=2,ttype=4)。测试过程中开发板SP605和国产FPGA同时进行NWRITE与NREAD循环操作,即在SRIO全双工工作模式下,通过FPGA自带的逻辑分析仪得到如图4所示的时序图。

图4 发送、接收时序图

通过FPGA内部比对模块的比对结果和逻辑分析仪抓取到的测试图可以看到,国产FPGA实现的SRIO接口可以与xilinx开发板SP605进行长时间正常通信,证明国产FPGA实现了SRIO接口的稳定性和正确性。

4 结 语

在目前的实际形式下,芯片国产化势在必行,且SRIO接口具有公开发布标准,高可靠性、低时延等特性使得其使用范围极广。本文在自主国产FPGA的平台上,使用厂家自主研发的IP CORE实现了SRIO接口的设计,并通过与xilinx的SP605开发板SRIO接口进行通信,验证了国产FPGA平台上SRIO设计的稳定性与正确性。