公差设计对高集成度微波收发组件可靠性的影响

2019-01-15魏守明顾江川张文超吴小虎

魏守明,顾江川,张文超,吴小虎

(南京电子器件研究所,江苏南京 210016)

0 引言

随着相控阵技术的发展进步,有源相控阵技术被广泛地应用于现代各种高新武器雷达装备中,例如:先进战机的机载火控雷达、远程预警探测系统、新一代舰船舰载一体化系统、星载对地观测雷达和导弹导引头制导雷达等,有源相控阵雷达已经成为了现代高新武器装备先进与否的一个重要标准[1]。收发组件在各类有源相控阵雷达装备中实现信号接收和发射功能,是装备实现电控扫描和收/发的核心部件。现代战争正在向高机动化、信息化方向发展,对各种系统提出了固态化、高可靠性和小型化的要求。在这种形势需求下,高集成度收发组件得到了大力发展。应用高集成度收发组件的有源相控阵雷达与传统的雷达相比,具有体积重量大幅减小、扫描更灵活、性能更可靠、抗干扰能力更强和能快速地适应战场条件的变化等特点[2]。高集成度收发组件作为有源相控阵雷达中最为核心的组成部分,影响和制约着武器装备的主要性能,是提高武器装备性能功能的核心部件。

图1 收发组件的原理图

1 收发组件工作原理

收发组件的工作原理框图如图1所示,接收和发射分时独立工作。稳压电源提供专用集成电路(ASIC: Application Specific Integrated Circuit)、 驱放、功放和低噪放的工作电压。ASIC将信号机提供的串联控制信号 (DATA、EN和T/R等)进行处理后产生并联控制信号 (C2、C3、C4和C5等)。在发射状态下,发射信号TX由数控移相器按ASIC提供的数据进行移相后,由开关1进入发射支路,经驱放和功放进行放大,使输出功率达到要求的电平,经过环形器由天线向空间辐射。在接收状态下,天线接收空间辐射的信号由环形器输入到接收支路,经限幅器和低噪放进行放大,然后由开关1送衰减器和移相器进行幅相调整,最后输出RX信号到信号处理机[3]。

2 高集成度微波收发组件的特点

高集成度收发组件是以微波毫米波单片集成电路芯片和射频MEMS芯片等核心芯片为基础,利用微电子制造技术、低温共烧陶瓷 (LTCC)技术、芯片微组装和高集成度封装技术等工艺技术开发的新型集成组件,具有体积小、重量轻、可靠性高、一致性好和成本低等优点[4]。核心芯片、微组装和LTCC微封装等制造技术的不断提高,牵引收发组件制造技术快速更新,突出表现在收发组件体积和重量不断减小,集成度不断提升,可靠性不断提高[5]。某高集成度毫米波八通道收发组件的外形图如图2所示,从图2中可以看出,该产品实现封装一体化,大小与一枚硬币相近,在该体积内共集成了8个收发通道,每个通道均可以实现信号接收和发射功能。

图2 毫米波八通道T/R组件

3 典型的失效案例分析

以某毫米波收发组件为例,其应用环境为导弹导引头制导雷达,在装机使用过程中,发生多起失效导致整机工作异常。将失效的组件返回,经过开帽后排查,确定故障原因包括:1)四芯绝缘子内导体与PCB包边之间公差设计不良,导致四芯绝缘子内导体与PCB包边存在短路隐患,在整机使用过程中受温度应力的影响,由短路隐患变为短路;2)ASIC芯片与吸收体之间公差设计不良,导致ASIC芯片上的金丝被吸收体压趴,金丝之间存在短路隐患,在整机使用过程中受温度应力的影响,由短路隐患变为短路。

3.1 四芯绝缘子内导体与PCB包边之间公差设计不良

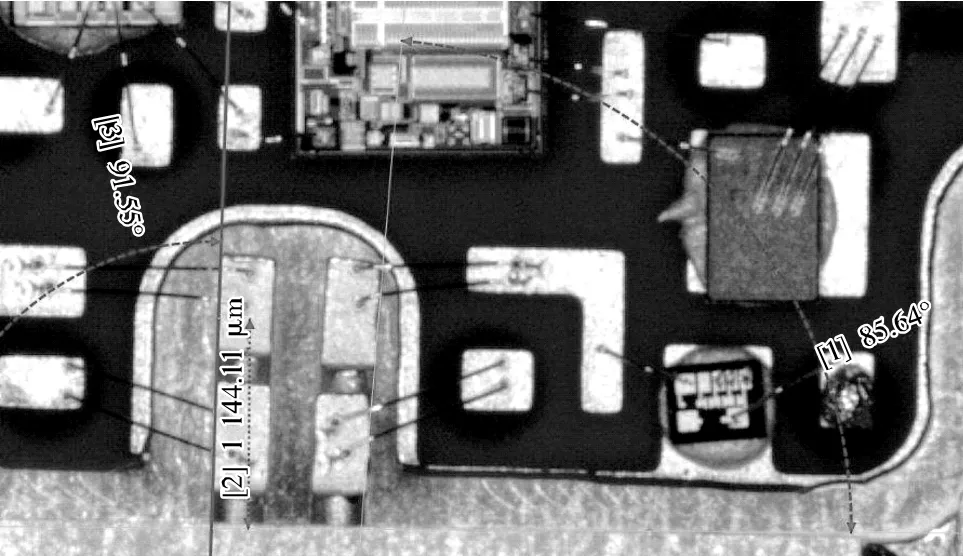

某用户反映,在常温条件下整机测试正常,但是在低温 (-55℃)条件下整机电流异常偏大。经排查,发现整机中某毫米波收发组件在低温条件下栅极加电端口 (Vg)对地短路。将故障组件开帽后,根据故障树在显微镜下进行故障定位,发现负责电压传输的四芯绝缘子内导体 (圆圈内)与PCB包边 (电学接地)近乎短路,在80倍显微镜下观察不到明显的缝隙,如图3所示。将该内导体远离PCB包边,预留可见的缝隙后,低温下该加电端口对地开路,恢复正常。因此,定位该四芯绝缘子内导体与PCB包边存在短路隐患导致低温下该组件失效。

图3 四芯绝缘子内导体与PCB包边短路

从图3中可以看出,发生短路的四芯绝缘子内导体 (右侧)距PCB包边比处于同一平面的左侧的内导体更近,同时发生短路的四芯绝缘子内导体有一定的偏心,对四芯绝缘子内导体偏心角度进行测量,结果如图4所示。发生短路的四芯绝缘子偏心角度为4.36°,未发生短路的四芯绝缘子偏心角度为1.55°,该角度符合GJB 548B方法2009.1的规定,即引线偏离平面不可超过20°。

图4 四芯绝缘子偏心角度

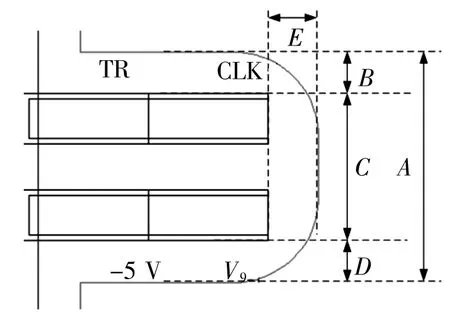

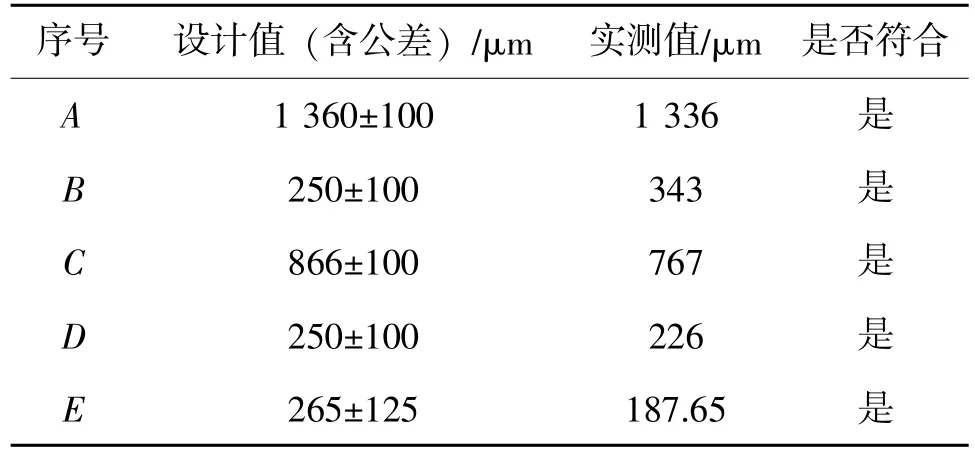

对四芯绝缘子内导体与PCB包边的各相关尺寸 (如图5所示)进行测量,测量结果和设计值对比如表1所示,从表1中可以看出,各尺寸均满足设计要求。在图5中,尺寸A为PCB“U形”凹槽的距离,尺寸B和D分别为四芯绝缘子内导体侧边与PCB包边的距离,尺寸C为四芯绝缘子两个内导体之间的距离,尺寸E为四芯绝缘子内导体顶端与PCB包边的距离。

图5 四芯绝缘子内导体与PCB包边的各相关尺寸

表1 四芯绝缘子与包边设计和实测对比

通过以上测量可知,四芯绝缘子内导体与PCB包边的各相关尺寸均在设计文件的规定范围之内,但是均有一定的偏差。这些偏差累积结合四芯绝缘子内导体发生了一定的偏心,共同导致了四芯绝缘子内导体会与PCB包边发生短路隐患。在常温条件下,尚未短路;但在低温条件下,各种材料发生形变,这些形变的综合作用导致短路隐患变为短路[6]。

3.2 ASIC芯片与吸收体之间公差设计不良

某用户反映,在常温条件下整机测试正常,但是在高温 (+70℃)条件下整机不受控。经排查,发现整机中某毫米波收发组件在高温条件下DATA信号端口为高电平,正常应为低电平。该组件开帽后,根据故障树进行故障定位,发现负责DATA信号传输的金丝与负责SEL信号传输的金丝近乎短路,在80倍显微镜下观察不到明显的缝隙,如图6所示。因为SEL信号为高电平,因此,两者发生短路时,DATA信号端口被拉高上升为高电平。人为将两根金丝分离,预留可见的缝隙后,高温下DATA信号端口为低电平,恢复正常。因此,定位DATA信号金丝和SEL信号金丝存在短路隐患导致高温下该组件失效。

图6 DATA信号传输金丝与SEL信号传输金丝短路隐患

观察图6所示的4根金丝的形貌可以看出,除了DATA和SEL信号金丝外,其余2根金丝拱弧处也发生了扭曲变形。该4根金丝均位于ASIC芯片上方,ASIC芯片区域剖面结构如图7所示,盖板下面贴吸收体,盖板距离基板设计尺寸为1 mm±0.05 mm,吸收体的厚度为0.25 mm±0.02 mm,ASIC芯片的厚度为0.4 mm±0.02 mm,ASIC芯片底部粘接材料的厚度为0.01 mm±0.005 mm。该处金丝采用楔形键合工艺,金丝键合的高度为0.3 mm±0.05 mm。经测量,该组件盖板距离基板尺寸为0.98 mm,吸收体的厚度为0.28 mm、ASIC芯片的厚度为0.41 mm,粘接材料的厚度为0.01 mm,均符合设计要求。测量变形后的金丝,金丝高度为0.28 mm。将以上尺寸累加,金丝已经触碰至吸收体。结合金丝拱弧处发生扭曲变形,而拱弧处在金丝的最高点,判断图6中的4根金丝被吸收体压趴。在常温条件下,金丝之间尚有微小的间隙,因此组件电性能正常;而在高温条件下,各种材料发生形变,这些形变的综合作用导致金丝由短路隐患变为短路。

图7 AISC芯片区域剖面结构示意图

4 解决措施

将图5中的尺寸A由原来的1 360 μm±100 μm增加为1 460 μm±100 μm, 可以保证极限公差和四芯绝缘子内导体偏心10°同时发生时,四芯绝缘子内导体与PCB包边仍然不会发生短路。

由于ASIC芯片是低频硅芯片,不会向外界辐射电磁波,因此其上方不贴吸收体不会影响组件的性能。后续产品不在ASIC芯片上方贴吸收体,以消除触碰金丝的隐患。小盖板上粘贴吸收体示意图如图8所示。

图8 小盖板上贴吸收体位置示意图

以上措施落实后,再未发生同类质量问题,证明改进措施有效。

5 结束语

本文对高集成度微波收发组件由于公差设计存在不足而导致的典型失效案例进行了分析,论述了公差设计对于产品可靠性的重要影响。针对这些失效案例,可以获得以下几点启示:

a)在高集成度收发组件实现过程中,对于尺寸精确度的要求不断地提高,在尺寸设计时要考虑充分,不仅要考虑到原材料的公差,还要考虑到装配的公差,保证在各种公差累积的情形下均不会出现失效,条件允许的情况下,可以留一定的余量;

b)针对公差设计存在隐患的地方,在装配工艺文件或图纸中进行标注,确保组件装配后可以达到设计效果;

c)组件试验要充分,不仅要关注各项电性能指标的实现情况,也要关注结构安装,保证产品在高低温或者综合应力条件下仍能正常工作。