一种新型的基于嵌入式MRAM的低功耗芯片架构技术研究

2019-01-10周明政

李 炜,徐 庶,周明政

(中电海康集团有限公司,浙江 杭州 311121)

0 引言

随着半导体工艺技术的不断进步和演进,主流半导体 CMOS制程已经从 28nm、16nm发展到10nm、7nm。随着芯片工艺制程不断提升,芯片的性能越来越高,面积越来越小,但随之而来的是功耗问题在芯片设计中变得越来越突出。

PPA(Power,Performance,Area)是制约芯片架构设计的主要方面。在进入到深亚微米甚至FINFET工艺节点后,芯片功耗成为了最主要的考虑因素,芯片的低功耗设计成为芯片架构设计的重中之重。

本文提出了一种新型的芯片架构,将嵌入式磁存储芯片(Spin-Transfer-Torque Magnetic Random Access Memory,STT-MRAM)应用于芯片架构设计中,与传统芯片架构相比较,能够降低芯片漏电流,减少芯片静态功耗,延长手持设备的在线工作时长,降低整体使用成本。

1 当前主流芯片低功耗设计方案简介

图1为当前主流IoT芯片架构方案示意图。

图1 当前主流芯片架构图

以一个常用的物联网领域的通信芯片为例,该SoC芯片分为以下几个主要的部分:CPU模块(ARM)、片上存储模块(SRAM)、无线传输模块(蓝牙、近场通信、射频等)、DSP子模块、多媒体模块、外设子模块及模拟模块等。其中,在多媒体模块、CPU模块以及ISP/DSP内部,都有着大量的SRAM存在。

芯片整体功耗由以下公式所示:

其中Vdd是芯片工作电压,Ileckage是芯片静止工作模式下的漏电流,C是介电常数(跟工艺有关),f是芯片工作频率。

由以上公式可以看出,芯片功耗分为动态功耗和静态功耗两类。

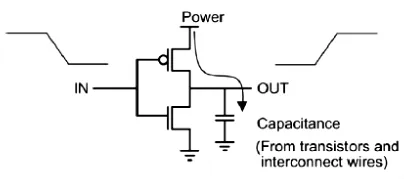

动态功耗跟电压成平方关系,跟运行频率成正比关系,因此,为了降低系统的动态功耗,芯片设计者尽量采用更先进的工艺、更低的电压,根据不同的应用场景选择不同的时钟工作频率,在不工作的时候关闭时钟等。CMOS管动态功耗示意如图2所示。

图2 CMOS管动态功耗示意

降低动态功耗的主要手段有如下几种方式:(1)Clock Gating(时钟门控)

(2)DVFS(动态电压和频率调节)(3)Multi-VDD(多电压域设计)

通常芯片设计者都会在降低动态功耗设计中采用上面的技术。但是采用过低的电压和过低的频率,会影响芯片整体的性能。因此,在成熟的芯片中,动态功耗降低的空间有限。

静态功耗跟芯片的工艺节点有关,也与半导体CMOS管门限电压有关。通常随着工艺节点的演进,动态功耗不断地降低,但静态功耗却不断地升高。在16nm甚至以下的工艺节点,静态功耗成为制约整体芯片功耗的主要矛盾。

图3 CMOS管静态功耗示意

图3 所示为CMOS管静态功耗示意。静态功耗来源于在晶体管通电状态下源极和漏级之间产生的微弱电流,即漏电流(Ileckage),根据栅极电压施加的不同,漏电流的大小也会不一样,通常情况下栅极电压越高,漏电流越小,但是CMOS导通性能下降。半导体制造商为了减少漏电流,通常在工艺库的设计中采用了3种不同栅极门限电压的库单元,即 LVT、RVT、HVT。

3种单元的漏电流和性能的对比如表1所示。

表1 不同的栅门限电压的标准库单元比较

减少静态功耗的设计方法通常有以下2种:

(1)Power Gating(电源门控)

(2)Multi-Vth Design(多栅极门限库单元设计)

Power Gating的做法是根据不同的应用场景,对不需要工作的模块进行关电处理,其能最大程度地降低漏电流,但带来的问题是需要重新上电后导致的延迟,以及掉电后需要对原模块内关键数据进行保存,否则会造成数据丢失。

多栅极门限库单元设计的主要做法是,在芯片综合实现的过程中,对不同模块、不同路径采用不同栅极门限电压的单元库进行综合产生。即对于性能要求高、时序紧张的模块和路径,采用LVT单元进行综合;对于性能要求不高、时序裕量较大的路径和模块,尽可能采用HVT单元去综合。采用这种方法,能够减少在后端实现和布局布线阶段的静态功耗损失。

对于业内成熟的芯片设计公司来说,这些主流技术已经完善应用在整个芯片设计的过程中,通过传统的方法来降低芯片功耗变得越来越困难。

芯片中很大一部分是存储单元。对于内部的SRAM存储单元来说,为了保持存储在其中的数据,一般都不进行关电设计;为了降低漏电流,半导体制造商因此也开发了具有数据保持功能的SRAM库单元,采用双电源供电,在不工作的情况下可以关掉主电源,只留下次电源进行数据锁存部分的CMOS管的供电,但这种低功耗设计方法对降低整体Memory部分功耗比较有限。

如何降低Memory部分的静态功耗,成为当前芯片静态低功耗设计的痛点之一。

2 磁存储芯片(STT-MRAM)的特点

在众多新型非易失性存储介质中,磁存储芯片(STT-MRAM)能够与CMOS半导体工艺良好兼容,利用较少的金属层即可以做到存储单元的高密度集成。同时,由于其接近于静态随机存储器(Static Random Access Memory,SRAM)的读写速度、极低的静态和动态功耗、掉电不易失的特性、接近于无限的擦写次数、高温下长时间的数据保持能力以及抗强磁场辐射等特性,是作为企业级SSD控制器中数据缓存和FTL表项存储的天生优良介质[1]。

当前,众多半导体设计大厂都将MRAM芯片作为下一代非易失性存储介质的研发重点。除了台积电、三星和东芝一直在持续推进STT-MRAM的研发之外,美国的EVERSPIN公司已经发布了256MB的量产测试芯片。在嵌入式MRAM领域,格罗方格半导体公司已经在22nm FD-SOI工艺平台上率先推出了eMRAM的选项,且良率可达到90%以上,可以供各芯片设计公司选用[2]。

将嵌入式STT-MRAM应用在芯片架构设计中,充分利用其掉电不易失数据的特性,能够对存储部分进行完全的关电设计,从而显著降低整个芯片的漏电流和静态功耗。

3 基于嵌入式STT-MRAM的新型芯片架构方案

如图4所示,为应用嵌入式STT-MRAM之后的新型芯片架构示意图。

图4 基于嵌入式STT-MRAM的新型芯片架构图

本方案的技术特征在于:

(1)用兼容 SRAM(SRAM-like)的嵌入式 STTMRAM IP取代传统的SRAM单元。SRAM-like的总线接口信号包括片选CS、写使能WE、读使能RE、输出使能信号OE、复位RST、时钟 CLK、地址线A[31:0]、数据输入线 DIN[31:0]和数据输出线DOUT[31:0]。除了一些串行配置接口之外,基本与SRAM IP的接口保持一致,非常便于SOC的系统集成。

(2)嵌入式eMRAM的主要作用在于:取代片上的SRAM单元,用来保存系统交互数据和作为数据缓存。同时对于拥有TCM(Tightly Coupled Memory)技术的ARM核来说,用一块贴近ARM的MRAM,可以用来存取指令,提升CPU取指令和执行的速度,进一步提升系统整体的性能。

(3)静态漏电流的显著降低。图5和图6描述了传统的带数据保持功能的 Memory(Retention Memory)和eMRAM的供电示意。电,在进入低功耗模式时可以关闭。次电源,对SRAM内部的数据锁存单元进行供电,一直保持开启,目的是在进入低功耗模式下保证SRAM原先存储的数据部分不丢失。因此,对于Retention SRAM中静态功耗的损耗主要是由内部数据保持单元的电源无法完全关断造成的。

图5 SRAM供电网络示意

对于具有数据保持功能的SRAM,本身带有两个电源,主电源(Primary VDD)和次电源(Secondary VDD)。主电源给SRAM外围逻辑和读写电路供

图6 MRAM供电网络示意

对于MRAM来说,由于内部存储单元具备掉电不易失特性,因此当芯片进入低功耗模式时,MRAM的电源VDD可以完全关断,因而MRAM存储部分的漏电流能够完全消失。与SRAM相比较,芯片在低功耗模式下的静态功耗会有明显降低。

采用基于ARM Cortex-M3内核的参考芯片设计进行了实验,该设计采用4块大小为32kB的单口双电源Retention SRAM。基于Global Foundaries 22nm FD-SOI的工艺库评估显示,当芯片工作在0.8V标准电压,室温25℃时,SRAM部分的静态功耗为0.175mW;当芯片工作在50MHz的工作频率时,采用50%的翻转率进行估算,芯片的整体功耗为3.83mW。如果采用本文提出的新型芯片架构,用STT-MRAM来替换SRAM,功耗能够降低约5%左右。如果对于内部SRAM比例更大(约30%-40%)的手机处理器来说,所节省的静态功耗会更明显,可以达到8%-10%左右。

4 结语

本文提出的一种基于嵌入式STT-MRAM的新型芯片架构,能够在先进工艺节点下在一定程度上降低芯片的漏电流及静态功耗,从而使手持式物联网设备获得较原来更长的在线工作时长,降低TCO成本,提升产品竞争力。其在功耗要求高的手持设备、可穿戴设备、物联网领域具备广泛的应用前景。