一种用于DC-DC的高PSRR参考电压电路

2019-01-03方海燕

李 新 ,苗 荟 ,,洪 婷 ,方海燕

(1.沈阳工业大学信息科学与工程学院,沈阳110870;2.北京伽略电子股份有限公司,北京100081)

1 引言

随着科学技术的发展,电源在通信、国防军工、消费类电子产品、人工智能等高科技领域内的应用十分广泛,已经深入到生产和生活的各个方面[1]。电源管理芯片在电子设备系统中承担着对电能的变换、分配、检测及其他电能管理的职责,其性能的优劣对整机性能有着直接的影响,因此,核心电源管理芯片的设计,在当今对电源的研究课题中,也占据着主流的地位[2]。

针对DC-DC对参考电压的温漂和电源抑制比性能的高要求,提出一种用于DC-DC开关电源管理芯片的高PSRR(Power Supply Rejection Ratio,电源抑制比)参考电压电路,并对其电源抑制比性能进行优化。在-40~125℃温度范围内可实现低至0.877mV的基准电压变化幅度,比文献[5]、[9]、[10]低很多;此外也在提高PSRR的同时兼顾了低温漂特性。

2 系统设计

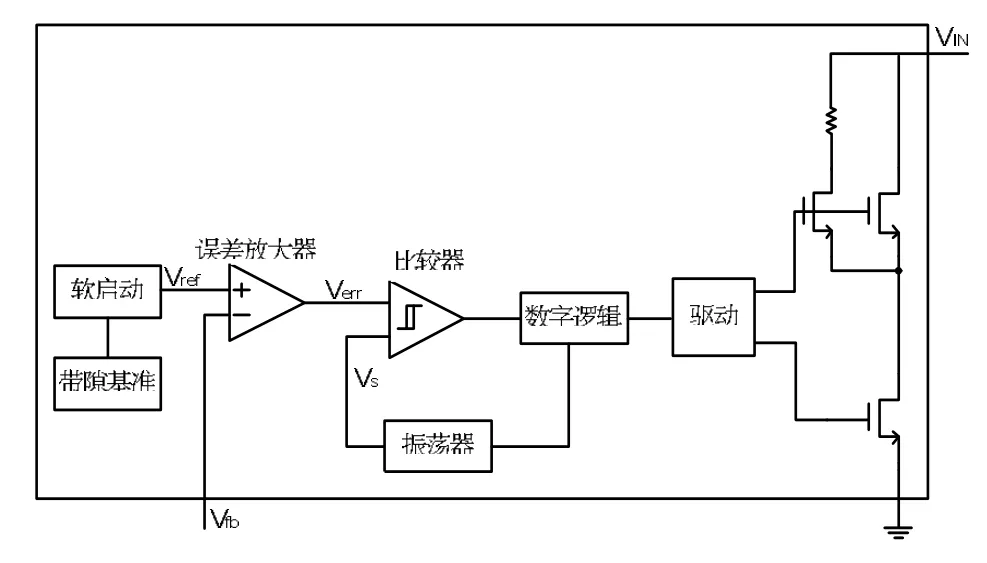

DC-DC开关电源结构框图如图1所示。其原理为:输入电压的变化通过反馈电阻网络后为Vfb,它与参考电压Vref之间的差值经过补偿网络反向放大后输出为Verr;误差放大器输出Verr与固定时钟频率的锯齿波Vs做比较,当输出电压变大时,误差电压Verr反相变小,因此控制功率开关管的导通时间较短,使得输出电压下降,反之亦然[3]。DC-DC需要参考电压系统提供一个精确的Vref信号,而开关电源从VIN吸取的电流是脉冲式的,VIN波动较大,故此内部电路的PSRR性能十分关键。针对此种情况,设计一种参考电压电路,采用双极晶体管型PTAT电流产生带隙基准电压,核心结构无需运算放大器,也因此不会受到运放失调电压的影响[4]。同时,由BG_GOOD作为指示信号,可以在上电启动结束之后,使供电电源由VIN转换为2.8V的内部稳压电源,从而不受VIN影响,提高PSRR性能。

图1 DC-DC开关电源结构框图

3 参考电压电路设计

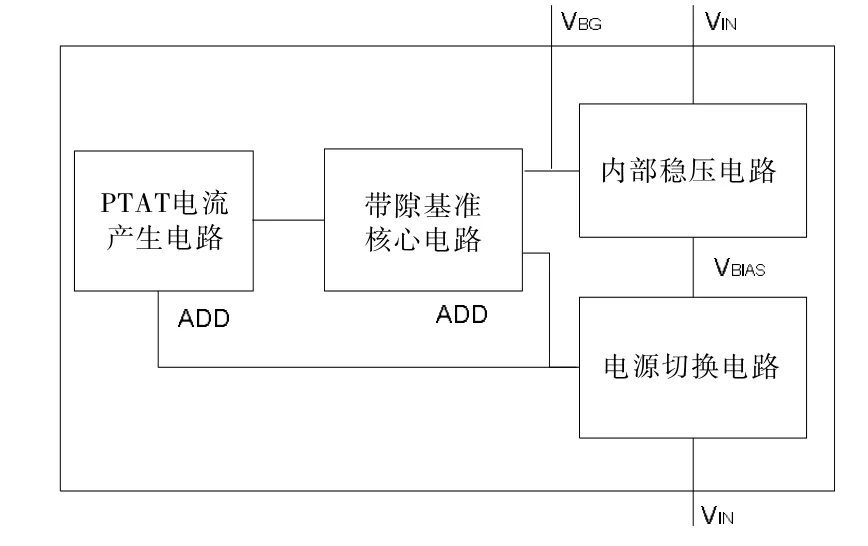

参考电压电路整体框图如图2所示,主要包括:PTAT电流产生电路、带隙基准核心电路、内部稳压电路、电源切换电路。当带隙电压稳定之后,BG_GOOD指示信号为高,它是带隙电源从VIN切换到VBIAS的必要条件之一。

图2 参考电压电路整体框图

3.1 PTAT电流产生电路

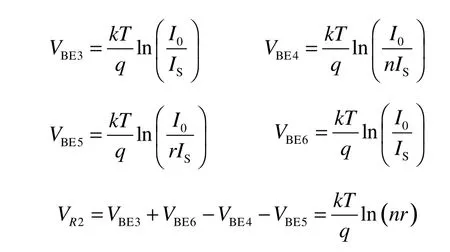

PTAT电流产生电路如图3所示。三极管Q3~Q6以及电阻R2构成交叉结构的PTAT产生电路,从中产生出PTAT电流。PM2、PM4尺寸相同,构成电流镜,且电流相同均为Io。

根据双极晶体管集电极电流IC与基极-发射极电压VBE的关系式IC=ISexp(VBE/VT)以及热电压的定义VT=kT/q,有:

可推导出:

其中n、r为管子的个数,皆为4。所产生出的电流和绝对温度成正比。与传统的PTAT电流产生电路比较,该电路无需运算放大器,从而避免了由于运放的不对称性造成输入失调而使输出电压产生误差;也避免了失调电压随温度发生变化令基准电压的温度系数随之增高[5]。PM5和R0会对PTAT注入一个永久存在的启动电流,助其摆脱简并态,同时为Q3和Q4提供基极电流,避免了电流偏差。PTAT电流产生电路为带隙基准核心电路提供了一个PTAT电流,通过PM2和M0构成的电流镜,接入带隙基准核心电路。

3.2 带隙基准核心电路

图3 带隙基准电路图

该带隙电路注重电源抑制比性能。一种提高电源抑制比的方法是引进反馈回路,令Q0、Q1的电流由上面PTAT电流产生电路的PMOS管M0提供,M0的电流从PTAT电流源镜像而来。M0的存在可以提高PSRR的能力。带隙电路中存在由M0~M4和Q0、Q1构成的反馈环路,如果由于某些原因,使Q0、Q1集电极电流增加,而M0提供的电流基本不变,则NMOS管M4栅极电压降低,Q0、Q1基极电压也降低,集电极电流随着减小,反之亦然。M3栅极-源极跨接的电容是米勒补偿电容,可以增加相位裕度。

第二种提高电源抑制比的方法是当芯片上电启动后,带隙模块供电电源由VIN切换到内部稳压电源。在DC-DC的VIN为3V到6V变化时,使其不受 VIN变化的影响。左侧 M1、M2、Q0、Q1组成的带隙基准核心电路产生稳定的基准电压后,M3导通,即M3上的电流为上述产生的PTAT电流,通过电流镜将此 PTAT 电流镜像为 Q10的 IC;PM15、PM14、Q8、Q7构成另一个PTAT电流产生电路产生Q10的IB,设计使IC大于IB,Q10导通经过迟滞电路和两个反相器BG_GOOD变为高电平,其中反向器对信号进行整形,此时将供电电源转换成内部稳压电路进行供电,从而提高PSRR。反之,M3关断,BG_GOOD为低电平。

3.3 内部稳压电路

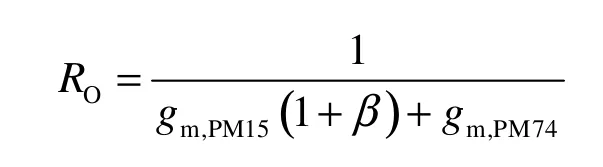

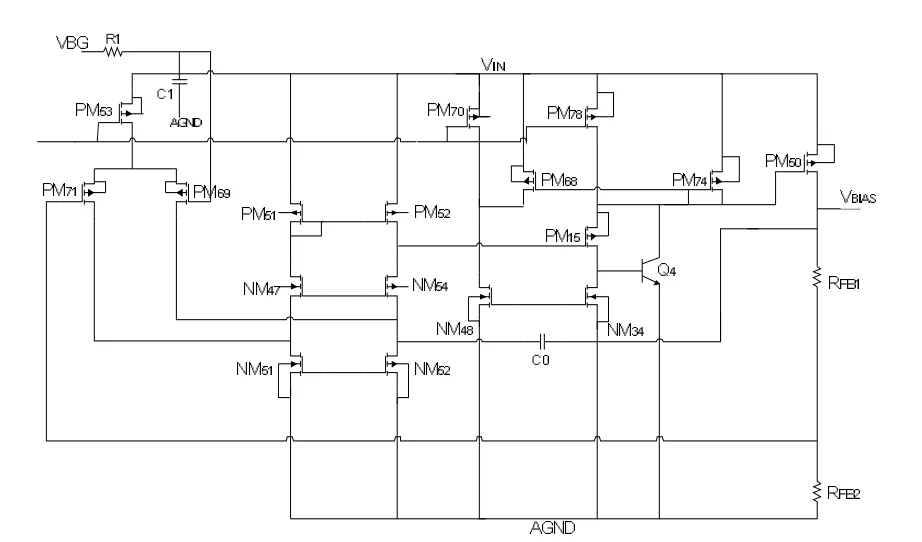

内部稳压电路如图4所示。它是一个LDO电路,包含误差放大器、阻抗衰减缓冲器、功率级。参考电压由上述带隙基准核心电路产生;误差放大器第一级为折叠共源共栅放大器,折叠共源共栅结构能够提高增益和PSRR[7];第二级采用带Shunt负反馈结构的动态电流偏置缓冲器[8],PM15是功率管驱动buffer,Q4为PM15的并联反馈器件,buffer的等效输出阻抗为:

可将buffer的输出阻抗减小β倍(β为Q4的电流放大倍数),又由P2和PPOW的相对关系:

可以形成极点-极点追踪效果[2],其中,米勒电容将主极点与次极点分开,提高相位裕度。采用此种频率补偿方法来增加LDO环路的稳定性,能够在VIN为3V到6V变化时产生2.8V稳定电压。

图4 内部稳压电路图

3.4 电源切换电路

电源切换电路如图5所示,当带隙基准电路稳定后,BG_GOOD为高电平,此时NM0导通使I0输出高电平,与VB_OK信号共同作用使与非门I1输出低电平,则反相器 I2、I3输出为高,从而使 PM2、PM9、PM7不导通;NM2导通使PM7漏端电压拉为低电平,从而PM6导通,使输出为VBIAS的电压,反之输出VIN,其输出接图3电路的ADD引脚,实现了当带隙电压稳定后,将带隙电源ADD从VIN切换到VBIAS的功能。

图5 电源切换电路图

4 电路仿真与测试结果

使用Spectre软件对设计的参考电压电路进行仿真:

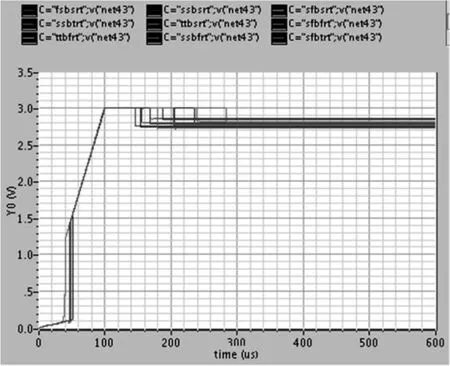

(1)在正常工作条件下,带隙电路的电源由内部稳压器(VBIAS)提供,而在芯片上电过程中,其电源是由VIN直接提供的,等到VBIAS稳定之后,再把电源从VIN切换到VBIAS。因此,需要验证不同条件下带隙和VBIAS稳压器的启动过程。由于VBG稳定之后,作为内部稳压器的参考电压,所以内部稳压器的启动时间比带隙电路启动时间晚30μs左右。仿真结果如图6、图7所示,带隙和内部稳压器均能正常启动。

图7 内部稳压电路启动波形图

(2)对温度进行直流扫描。在典型条件下,带隙电压值大约为1.2V,在-40℃~125℃范围内的最大值和最小值之差为0.877mV。以此为条件模拟的结果如图8。

图8 温度特性典型曲线图

(3)对电源抑制比进行仿真。带隙电路自身的电源抑制比非常高,低频段大于80dB,100kHz时大于50dB。另外,正常工作时带隙电路由VBIAS供电,内部稳压器的电源抑制能力会进一步隔绝VIN对带隙电压的影响。在此条件下的模拟结果如图9。

图9 电源抑制比曲线图

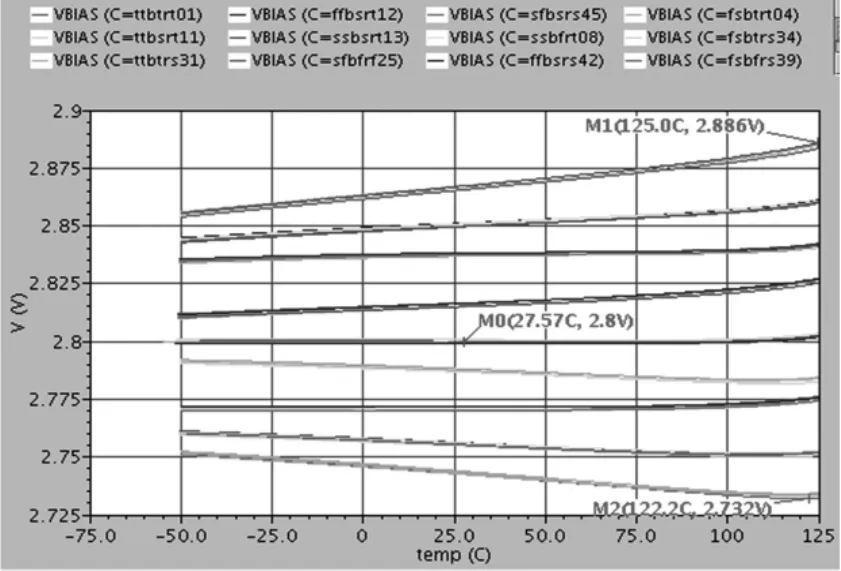

(4)设置VIN值为3V、6V,在不同负载条件下对温度进行直流扫描分析。VBIAS的常温典型值为2.8V,最大值为2.886V,最小值为2.732V。在此条件下的模拟结果如图10。

图10 VBIAS稳压电路仿真图

(5)对VBIAS稳压电路环路的稳定性进行仿真。在不同温度、不同负载和不同工艺角下,对稳压电路进行stb仿真,通过曲线可以看到buffer的输出极点与内部稳压器的输出极点移动一致,形成极点-极点追踪,在DC-DC的VIN变化时,能够为基准电压稳定供电2.8V,使其不受VIN变化的影响。在此条件下的模拟结果如图11。

图11 VBIAS稳压电路环路仿真图

5 结束语

本设计实现了一种用于DC-DC开关电源的参考电压电路,利用了负反馈网络和BG_GOOD指示信号指示VIN与VBIAS的变换,从而提高了基准电压的电源抑制特性。虽然增加了电路的复杂度和芯片面积,但能够完全隔离VIN变化对基准电压的影响,得到高精度的参考电压,来消除缩放分压和误差放大器电路的失调误差。该电路可以应用于高性能的DC-DC开关电源管理芯片中。经过Spectre软件的仿真,各项指标均满足要求。