低功耗自适应偏置无片外电容低压差稳压器

2018-12-26刘云超陈敏刘云涛肖璟博张成彬陈杰

刘云超 陈敏 刘云涛 肖璟博 张成彬 陈杰

摘 要:设计了一款低功耗自适应偏置无片外电容低压差线性稳压器.为了解决由于设计和工艺中存在不匹配造成每级误差放大器不同类型输入管的反型系数在自适应偏置下变化不同步问题,提出了由循环折叠共源共栅放大器和跨导提高放大器构成的误差放大器结构,同时采用推挽输出结构提高了对功率管的驱动能力.该无片外电容低压差稳压器采用嵌套密勒补偿和自适应偏置,解决了轻负载时的稳定性问题,同时提高了轻负载下的电流效率.芯片采用SMIC 0.18 μm CMOS工艺设计,版图面积为0.019 9 mm2.蒙特卡罗后仿真的结果表明,其负载电流范围为10 μA~100 mA,最大负载寄生电容为100 pF,最小负载下静态电流为1 μA,负载调整率和电源调整率分别为3.5 μV/mA和0.372 mV/V.设计的低压差稳压器具有低功耗、无片外电容、面积小的优点,是片上系统中电源管理知识产权核的良好选择.

关键词:线性稳压器;低功耗;无片外电容;自适应偏置

中图分类号:TN402 文献标志码:A

Abstract:A lowpower adaptively biased outputcapacitorfree lowdropout linear regulator was designed. In order to tackle the problem that the inversion coefficients of different types of input transistors in each error amplifier stage may vary asynchronously under adaptive bias caused by mismatches in the design and process, an error amplifier comprised of the recycling folded cascode amplifier and transconductanceboosting amplifier was proposed. The driving ability for the power transistor was improved by the adopted pullpush output structure. Nested Miller compensation and adaptive bias were used to solve the stability problem of outputcapacitorfree lowdropout regulator and improve the current efficiency at light loads. The regulator chip was implemented in SMIC 0.18 μm CMOS process with a layout area of 0.019 9 mm2. The Monte Carlo postsimulation results show that the load current range is 10 μA~100 mA with the maximum load parasitic capacitance of 100 pF, and the quiescent current is 1 μA at the minimum load condition. The load regulation and line regulation are 3.5 μV/mA and 0.372 mV/V, respectively. The designed lowdropout regulator has the merits of low power consumption, no offchip capacitor and small area, which indicates that it is a good choice as intellectual property core of the power management for the system on chip.

Key words:linear regulator; low power consumption; outputcapacitorfree; adaptive bias

低压差线性稳压器(lowdropout linear regulator, LDO)是一种重要的电源管理芯片,具有噪声低、紋波小、电源抑制比高、精度高、结构简单、封装小、瞬态响应速度快等优点,被广泛应用于片上系统设计中,特别是高性能的模拟、数模混合电路中.传统结构的LDO需要一个带等效串联电阻的片外电容起到频率补偿作用,稳定LDO的输出电压,抑制过充电压[1-4],但是它增加了芯片引脚和片外元件,而且增加了负载电源线间的串扰,不利于电压调整[5].因此,无片外电容LDO逐渐成为研究热点.

无片外电容LDO实际上是由多级放大器构成的负反馈放大电路,在LDO环路中存在多个极点,不利于LDO稳定工作,国内外学者对此提出了不同的补偿方案.文献[5]提出一种阻尼系数控制的补偿方法,文献[6]提出了品质因数Q值减小技术,文献[7]提出通过功率管阵列实现平滑的极点追踪技术,文献[8]提出有源反馈结合前馈的技术,这些方法都是通过减小复极点对的Q值来实现环路稳定,但是存在一些固有缺点,如补偿电路结构复杂[5,7-8]、静态电流过大[6-7]或轻负载下不稳定[5-7]等缺点.文献[9-15]采用了自适应偏置方法,其中误差放大器的部分偏置电流镜像复制功率管的工作电流,弥补上述缺陷,但是还存在如下问题:1)误差放大器对功率管栅极电容充放电速度受到尾电流源的限制[9-15];2)设计和工艺中存在失配造成每级误差放大器不同类型输入管的反型系数随LDO负载变化不同步[14];3)需要片外电容[9,13,15].

本文设计了一种采用嵌套密勒补偿自适应偏置无片外电容LDO.为了解决误差放大器输入管的反型系数随LDO负载电流变化不同步问题,提出了由输入管都是PMOS管的循环折叠共源共栅放大器和跨导提高放大器组成的误差放大器结构,同时在跨导提高放大器中采用推挽输出结构提高了对功率管栅极电容充放电的速度.此外,该结构具有很高的开环增益,因此有效提高了LDO的负载调整率.为了减小LDO的静态功耗和芯片面积,使用了二极管连接的PMOS管反馈网络.

1 提出的LDO结构及原理分析

1.1 LDO的电路结构

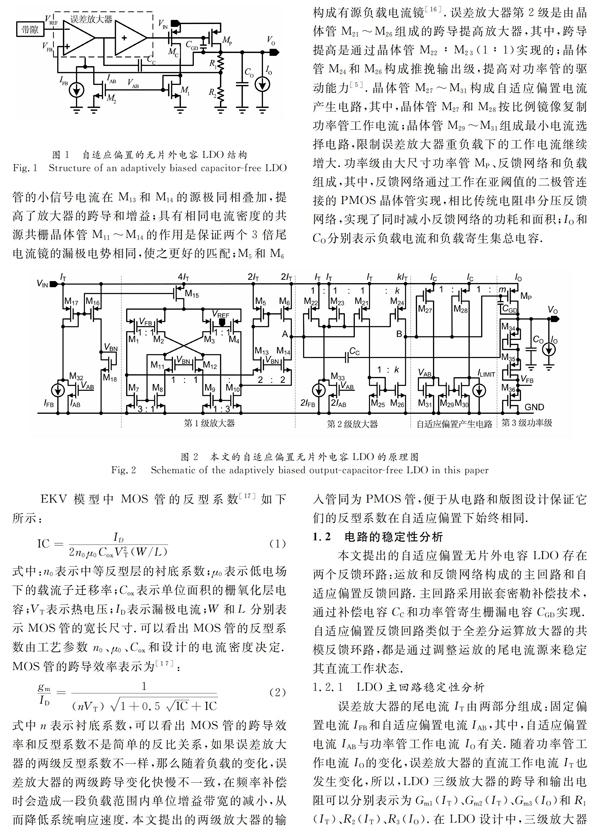

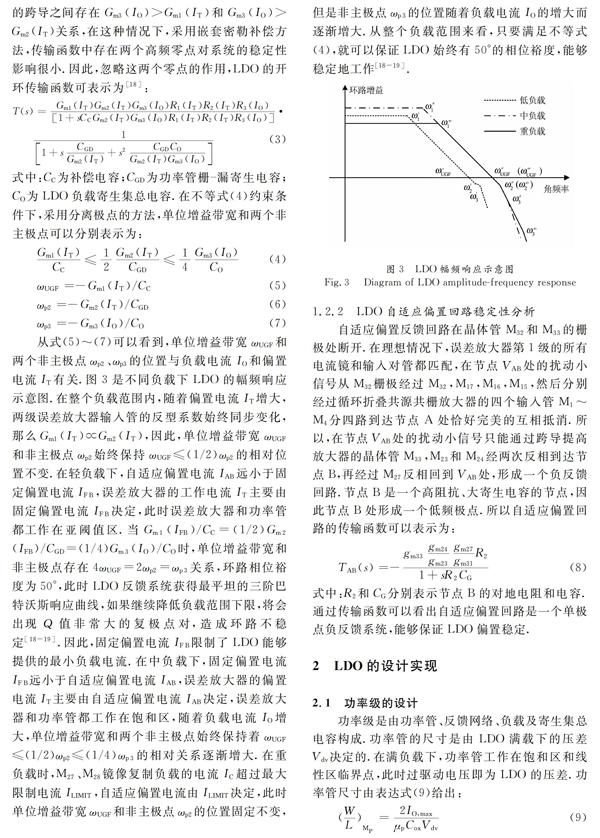

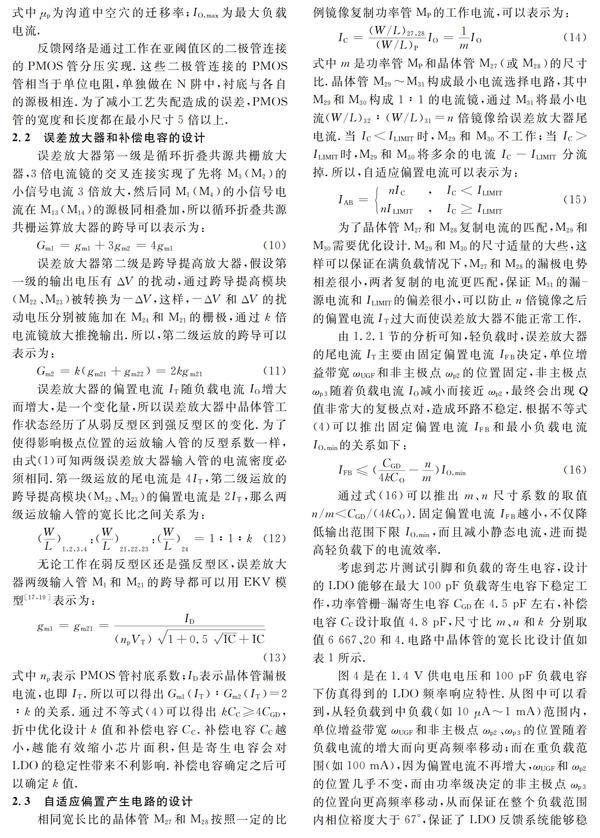

图1是一个基于自适应偏置的无片外电容LDO结构.它由以下几部分构成:误差放大器、带隙基准源、功率管、反馈网络、补偿网络、自适应偏置电路.功率管尺寸决定了LDO所能提供的最大负载电流,一般设计的尺寸都非常大;由三级放大器组成的LDO环路中存在三个低频极点,可以利用功率管的栅极和漏极之间存在的pF级寄生电容CGD和补偿电容CC共同实现嵌套密勒补偿方法,将第二、三级放大器输出节点的两个非主极点推至单位增益带宽外,保证LDO有足够的相位裕度;自适应偏置电路通过电流镜按固定的比例镜像复制LDO的负载电流,为误差放大器提供自适应偏置电流,提高LDO轻负载下的电流效率和重负载下的瞬态响应特性;误差放大器将反馈电压VFB同由带隙基准源提供的高精度、低温漂参考电压VREF进行比较放大,调整功率管的工作状态,稳定LDO的输出电压.本文提出了由循环折叠共源共栅放大器和跨导提高放大器组成的误差放大器,可以使得误差放大器输入管的反型系数始终一致,推挽驱动功率管,增大了LDO的环路增益进而有效地提高LDO的负载调整率和电源调整率.

3 后仿真结果分析

本文的自适应偏置无片外电容LDO采用SMIC 0.18 μm CMOS混合信号工艺模型设计和仿真,版图面积为0.019 9 mm2(194.08 μm×102.78 μm),如图5所示.其供电电压范围是1.4~2 V,输出电压为1.2 V,输出负载电流范围是10 μA~100 mA.

为了充分考虑工艺制程变化和器件失配对电路带来的影响,特别是轻负载下电路中MOS管工作在亚阈值区,对电路的瞬态特性进行了蒙特卡罗后仿真.图10是针对电源瞬态响应特性进行了300次蒙特卡罗后仿真的结果,在100 mA负载和100 pF负载寄生电容条件下,供电电压从1.4~1.8 V以1 μs的时间阶跃变化,LDO输出上冲样本均值(Mean)和标准差(Std Dev)分别为23.82 mV和1.44 mV,输出下冲样本均值和标准差分别为24.94 mV和1.80 mV.图11和12是在1.8 V供电电压下重负载和轻负载时针对负载瞬态响应特性进行了300次蒙特卡罗后仿真的结果.负载电流从1~100 mA以1 μs的时间阶跃变化,LDO输出上冲的样本均值和标准差分别是81.39 mV和3.33 mV,下冲的样本均值和标准差分别是83.32 mV和5.14 mV;从10 μA~1 mA以1 μs的时间阶跃变化,LDO输出上冲的样本均值和标准差分别是133.2 mV和1.61 mV,下冲的样本均值和标准差分别是162.37 mV和0.64 mV.瞬态响应特性蒙特卡罗后仿真的结果表明LDO具有很好的鲁棒性,能够稳定地工作,为负载提供稳定的工作电压.

表2是其它文献中LDO电路与本文设计电路的性能比较.相比文献[56]中固定偏置结构无片外电容LDO,本文设计自适应偏置LDO无论是轻负载下的静态电流还是最小负载电流都减小了1~2个数量级.文献[9,13,15]中的自适应偏置LDO以增添片外电容为代价实现空载下的稳定工作.相比文献[10,14]中自适应偏置LDO,综合从芯片面积、轻负载下静态电流、最小负载电流三项指标来看,本文设计的三项指标都较小,仅次于文献[12],但是本文采用的工艺节点相比文献[12]落后3代.本文中LDO的电源调整率较小,仅次于文献[6],而负载调整率也最小,这都与LDO环路的高增益有关.从对比结果来看,本文设计的无片外电容LDO在芯片面积、轻负载下静态功耗和负载电流范围得到了很好的折中优化,而且能够为负载提供精准稳定的工作电压.

4 结 论

本文设计了一个低功耗自适应偏置无片外电容LDO.利用嵌套密勒补偿和自适应偏置解决了LDO在轻负载下环路中出现复极点对的问题,确保其在10 μA的轻负载下也能够稳定工作,同时降低了静态电流,进而提高其轻负载下的电流效率.提出的由循环折叠共源共栅放大器和跨导提高放大器构成的误差放大器结构,保证在自适应偏置下每级误差放大器PMOS输入管的反型系数始终一样,推挽输出驱动功率管,增大LDO的环路增益进而提高负载调整率.同其它结构相比,本文设计的LDO结構简单,版图面积显著降低,在轻负载下的静态功耗相对较小.蒙特卡罗后仿真的结果表明LDO具有很好的稳定性,可以作为电源管理知识产权核应用于片上系统设计中.

参考文献

[1] 王 忆,何乐年.CMOS低压差线性稳压器[M]. 北京:科学出版社, 2012:19-20,71-73.

WANG Y, HE L N. CMOS lowdropout linear regulator [M]. Beijing: Science Press, 2012:19-20,71-73. (In Chinese)

[2] RINCONMORA G A, ALLEN P E. A lowvoltage, low quiescent current, low dropout regulator [J]. IEEE Journal of SolidState Circuits, 1998,33(1):36-44.

[3] OH W, BAKKALOGLU B. A CMOS lowdropout regulator with currentmode feedback buffer amplifier [J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2007,54(10):922-926.

[4] HO M, LEUNG K N, MAK K L. A lowpower fasttransient 90nm lowdropout regulator with multiple smallgain stages [J]. IEEE Journal of SolidState Circuits, 2010,45(11):2466-2475.

[5] LEUNG K N, MOK P K T. A capacitorfree CMOS lowdropout regulator with dampingfactorcontrol frequency compensation [J]. IEEE Journal of SolidState Circuits, 2003,38(10):1691-1702.

[6] LAU S K, MOK P K T, LEUNG K N. A lowdropout regulator for SoC with Qreduction [J]. IEEE Journal of SolidState Circuits, 2007,42(3):658-664.

[7] LIN Y H, ZHENG K L, CHEN K H. Smooth pole tracking technique by power MOSFET array in lowdropout regulators [J]. IEEE Transactions on Power Electronics, 2008,23(5):2421-2427.

[8] HO E N Y, MOK P K T. A capacitorless CMOS active feedback lowdropout regulator with slewrate enhancement for portable onchip application [J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2010,57(2):80-84.

[9] LAM Y H, KI W H. A 0.9V 0.35μm adaptively biased CMOS LDO regulator with fast transient response [C]// 2008 IEEE International SolidState Circuits Conference (ISSCC), Digest of Technical Papers. San Francisco, USA: IEEE,2008:442-626.

[10]ZHAN C, KI W H. Outputcapacitorfree adaptively biased lowdropout regulator for systemonchips [J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2010,57(5):1017-1028.

[11]ZHAN C, KI W H. An outputcapacitorfree adaptively biased lowdropout regulator with subthreshold undershootreduction for SoC [J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2012,59(5):1119-1131.

[12]CHONG S, CHAN P K. A 0.9μA quiescent current outputcapacitorless LDO regulator with adaptive power transistors in 65 nm CMOS [J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2013,60(4):1072-1081.

[13]MAITY A, PATRA A. Design and analysis of an adaptively biased lowdropout regulator using enhanced current mirror buffer [J]. IEEE Transactions on Power Electronics, 2016,31(3):2324-2336.

[14]MAITY A, PATRA A. Tradeoffs aware design procedure for an adaptively biased capacitorless low dropout regulator using nested miller compensation [J]. IEEE Transactions on Power Electronics, 2016,31(1):369-380.

[15]MAITY A, PATRA A. A hybridmode operational transconductance amplifier for an adaptively biased low dropout regulator [J]. IEEE Transactions on Power Electronics, 2017,32(2):1245-1254.

[16]ASSAAD R S, SILVAMARTINEZ J. The recycling folded cascode: a general enhancement of the folded cascode amplifier [J]. IEEE Journal of SolidState Circuits, 2009,44(9):2535-2542.

[17]BINKLEY D M. Tradeoffs and optimization in analog CMOS design [M]. England: John Wiley & Sons, 2008:33-294.

[18]LEUNG K N, MOK P K T. Analysis of multistage amplifierfrequency compensation [J]. IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, 2001,48(9):1041-1056.

[19]SANSEN W M C. Analog design essentials [M]. Netherlands: Springer, 2006:1-49,263-290.