高精度电荷域ADC共模电荷误差前台校准电路

2018-12-07陈珍海魏敬和于宗光苏小波

陈珍海,魏敬和,于宗光,3,苏小波,3,薛 颜,张 鸿

(1. 黄山学院 信息工程学院,安徽 黄山 245041; 2. 中国电子科技集团第五十八研究所,江苏 无锡 214035; 3. 西安电子科技大学 微电子学院,陕西 西安 710071; 4. 西安交通大学 微电子学院, 陕西 西安 710049)

高速高精度流水线模数转换器(Analog-to-Digital Converter, ADC)一直是各类中频采样系统的主要选择,因而被大规模运用于多载波宽带无线通信和雷达接收等电子应用系统中[1-3].通过采用各类新颖的设计技术,已报道的流水线ADC性能得到快速提升.通过采用先进纳米工艺和各类数字校准技术,基于开关电容技术的14位流水线ADC采样速率可以达到1GS/s以上[4-6],但是该类ADC内部使用的高增益带宽积运算放大器仍然消耗了大量功耗.

基于增强型电荷传输(Boosted Charge Transfer, BCT)电路的电荷域ADC是一种无运放的超低功耗的高速流水线ADC实现技术[7-8].然而,其面临的一个突出问题是各级BCT输出电荷会受工艺、电压和温度(Process, Voltage and Temperature, PVT)波动以及输入共模电荷的影响而产生共模电荷误差.针对PVT波动问题,文献[9-11]中提出了一种伪差动辅助型和一种镜像控制型PVT不敏感BCT结构,完成了10位电荷域流水线ADC的设计与实现;针对输入共模问题,文献[12]提出了一种输入共模电荷前馈补偿电路,将电荷域流水线ADC的精度进一步提升到12位;然而精度14位以上的电荷域流水线ADC还鲜有文献报道.

为进一步提高电荷域流水线ADC的精度,笔者提出了一种数模混合共模电荷误差校准方法,在现有共模电荷控制技术基础上可进一步对各流水线子级中电容非线性而产生的共模电荷误差量进行补偿,并成功应用于一款低功耗14位 210 MS/s 电荷域流水线ADC中.该ADC电路采用 1.8 V 1P6M 0.18 μm 互补金属氧化物半导体(Complementary Metal-Oxide-Semiconductor,CMOS)工艺进行设计并流片验证.

1 电荷域流水线子级电路共模电荷误差分析

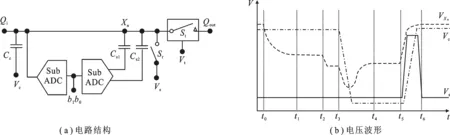

图1(a)所示为典型1.5 bit电荷域ADC子级电路结构,包括一个电荷存储节点Xn,电荷传输电容Cc、子DAC电容Cs1和Cs2,本级量化子ADC电路,产生余量电荷Qout的子DAC电路,一个BCT电路开关St和一个在Qout传输完成之后对Xn进行复位的复位开关Sr.其中,子DAC和子ADC电路的具体实现可见文献[8].图1(b)所示为该电路工作的电压波形示意图.t0时刻,Qi被传输到本级电荷存储节点Xn,由于电荷注入Xn的电压VXn将会由t0时刻的VXn(0)不断降低;t1时刻,前级电路向本级电路的电荷传输工作结束,此时本级子ADC电路开始电荷比较量化工作,得到本级量化结果b1b0;t2时刻,b1b0通过子DAC控制电容Cs1和Cs2对Qi进行电荷加减,得到本级电路的余量电荷Qout;t3时刻,本级BCT电路St将Qout传输到下一级子级电路;t4时刻,本级BCT电路St关断,VXn将会被稳定到VXn(4),电荷传输工作结束;t5时刻,复位开关Sr打开,对Xn进行复位;t6时刻完成一个完整的时钟周期.

图1 电荷域1.5 bit子级电路结构及工作原理波形

上述子级电路中,假设Cs1=Cs2=Cs,可以得到输入输出电荷量关系为

Qout=Qin+(b1+b0)CsΔVR+(Cc+2Cs)(VXn(0)-VXn(4))+CcΔVc=Qin+(b1+b0)CsΔVR+Qc,

(1)

其中,VR为子DAC输出参考电压的变化量,Vc为Cc下端控制电压Vc的高低参考电压变化量,Qc= (Cc+ 2Cs)(VXn(0)-VXn(4))+CcΔVc.当 1.5 bit 电荷域子级电路采用差分形式实现时,可以得到该子级电路的输出共模电荷为

其中,VR是子DAC满幅参考电平变化量;Qin,CM是输入共模电荷量.式(2)中,第1项为输入共模电荷,针对该部分产生的共模误差可以通过文献[12]所提出的共模前馈补偿技术进行补偿; 第2项为电荷传输过程中引入的固定电荷增量Qc,该部分共模分量误差由Cc和Cs的电容非线性以及VXn(4)波动共同产生,针对VXn(4)波动可以通过采用文献[9-11]所提出的PVT波动不敏感BCT电路进行控制; 第3项误差为子DAC增量电荷CsVR/2,该部分共模分量产生误差的原因主要是Cs电容的非线性和寄生电容影响.要实现高精度电荷域ADC,Cc和Cs的电容非线性所引起的共模误差影响必须进行校准控制.

假设由于寄生电容的影响导致电容Cc或Cs产生了大小为ΔC的电容误差,若VXn(0)、VXn(4)和VR均不变,则Qout,CM电荷量将会产生ΔQ的误差电荷.若在该误差电容(假设大小为Ce)对应的电压上补偿一个大小为 -ΔQ/Ce的电压 -ΔV,即人为补偿一个大小为 -ΔQ的电荷到产生误差的对应电容上,那么该电容非线性产生的误差即可消除.由式(2)可知,和Qout,CM电荷量相关的电压量为VXn(0)、VXn(4)和VR,其中VXn(0)和VR为保持固定影响芯片全局的基准电压,所以适合进行ΔV电压补偿的控制电压为VXn(4).文中所提出的共模电荷误差校准电路所采用的方法就是在文献 [9-11]所提出的控制技术产生的VXn(4)基础上,进一步通过数模混合校准产生ΔV的电压补偿量对VXn(4)进行微调,使之抵消电容非线性的影响.

2 高精度共模电荷误差校准电路结构及实现

2.1 校准电路结构

文中所提出的数模混合型共模电荷误差校准电路的结构图如图2(a)所示,在文献 [9-12]所提出的共模电荷控制技术基础上,进一步采取了针对电容非线性所引起共模电荷误差的前台校准补偿措施.为方便说明,图2(a)给出的校准电路被运用于第N级流水线子级电路中,整体校准电路由共模检测、共模前馈、共模比较、数字脉冲过滤、共模校准控制、8位寄存器和共模调整等电路功能模块构成.校准电路采用前台校准的方式完成对电荷域ADC共模电荷误差的校准工作,校准顺序为由前级向后级依次逐级校准.校准电路针对电容非线性所引起共模电荷误差的校准补偿措施,最终通过精确调整BCT的工作状态来实现.

图2 共模电荷误差校准电路的结构图和补偿原理示意图

当ADC进入共模前台校准模式时,共模校准控制电路首先控制8位补偿码Cal(N)输出默认值80H,使VFB(N)输出初始调整电压VFB(N)(0); 此时假设第N-1 级电路输入的共模电荷误差已经被校准过,本级电荷域流水线子级电路中由于电容非线性变化引起的共模电荷误差会体现在该级电路的输出共模电荷上,并被共模检测电路所检测,检测得到的共模误差CM(N)将会被共模比较电路进行误差方向判别得到误差方向信号Dir,Dir进入数字脉冲过滤电路进行统计处理得到误差量Err(0),共模校准控制电路根据Err(0)产生新的8位补偿码Cal(N).若Err(0)为1,表示本级共模电荷偏高,共模校准控制电路会将8位补偿码 Cal(N) 修改为D0H,使VFB(N)(1)>VFB(N)(0),以增大VXn(4)电压,进而减小本级共模电荷; 反之,若Err(0)为0,表示本级共模电荷偏低,共模校准控制电路会将8位补偿码 Cal(N) 修改为40H,进而增大本级共模电荷.校准电路将采用“二分法”逐次逼近的方式,先后进行8次运算,从而确定最终的8位补偿码 Cal(N) 并保持不变,同时产生最终共模调整电压VFB(N)(7),此时本级共模电荷误差校准过程结束.在共模电荷前台校准过程中,共模前馈电路将会被关闭,当校准结束后共模前馈电路才会开始工作.

图2(b)为共模调整电压VFB(N)对本级共模电荷量的补偿原理电路图.该电路在文献[11]所提出的镜像控制型BCT电路基础上,将误差放大器反向输入端由基准电压VR替换成共模电荷调整电压VFB(N),另外还使用了文献[12]提出的共模前馈电路.流水线子级电路中,输入共模电荷误差由VFF(N)控制NMOS管M1FF进行实时补偿,由电容非线性变化引起的共模电荷误差由VFB(N)控制VXn(4)电压进行补偿.共模前台校准过程中,当本级共模电荷量偏高时,调整电压VFB(N)将会被增大,而VXn(4)和VFB(N)为正比例关系式[11],因此VXn(4)也会增大,由式(2)可知,本级共模电荷将会被减小,从而实现共模电荷校准的功能.

文中采用的共模电荷检测电路由共模电荷不敏感采样网络和一个差分电压放大器连接构成,共模比较器电路采用现有成熟的电压比较器即可实现,共模调整电路可以采用数字控制型LDO电路来实现.为提高共模校准过程中共模电荷误差方向判别的准确率,采用数字脉冲过滤电路对共模比较电路输出的Dir量进行多次采样并进行统计分析才输出一次Err,以避免电荷热噪声的影响.

2.2 共模检测电路

图3(a)为文中所采用的共模检测电路的实现方式.该电路采用全差分结构实现,共模电荷不敏感采样网络由4个电荷采样器和共模电压不敏感的开关电容采样网络构成; 增益为Ad的全差分放大器由现有成熟的差分电压放大器即可实现.电路输入端采用电荷采样器的目的是防止差分电荷存储节点上的电荷QoutN,P和QoutN,N通过MOS开关与C1和C2上的电荷产生耦合,从而引起检测误差.共模检测电路采用电荷检测器对电荷信号QoutN,P和QoutN,N以及基准信号Rp和Rn进行检测得到电压信号之后,开关电容差分电压信号采样网络对4个电压信号进行进一步的采样,得到差分电压信号Vi+和Vi-,经过进一步放大得到输出共模误差信号.电荷检测器的实现如图3(a)中虚线框中所示,为一个由时钟控制的源跟随器电路.当时钟Φ2为高时,电荷检测开关电路处于导通正常检测状态,电荷信号QoutN,N的变化将会通过源跟随器响应,得到输出电压信号Voutn; 当时钟Φ2为低时,电荷检测器处于关断不工作状态,输出电压信号被拉到地.考虑到源跟随器会产生的压降,M3管采用了低阈值NMOS管实现.

图3 共模检测及调整电路结构

2.3 共模电荷调整电路

图3(b)所示为文中共模调整电路的具体实现,其结构为数字控制型LDO电路.当ADC开始进入正常工作模式时,控制信号置1,M1导通,由于运算放大器的负反馈作用,基准电压VREF在调整PMOS管M50的控制下经电阻分压得到一个初始电压输出VR(0),同时 8 bit 电流型DAC还会产生一个到地的调整电流Ic,调整电流Ic流经最末端电阻到地,这样就会在该电阻上叠加一个 ΔV=IcR2的电压量,输出到基准信号输出电路的电压VR=VR(0)+ΔV.根据电阻分压关系,输出基准电压信号VFB会相应地产生变化.因此,只要控制8位补偿码便可以实现改变输出基准电压的目的.

2.4 数字脉冲过滤电路

数字脉冲过滤电路是文中ADC共模校准电路系统中较为关键的一个模块,它在控制信号和时钟的控制下,对Dir信号进行选择采样,然后进行脉冲统计处理,并输出共模误差方向信号Err.由于在共模比较电路中比较器判别的电平比较接近于参考电平时,比较器的输出可能会产生波动.数字脉冲过滤电路通过其内部的16位计数器,累计统计15次Dir的输出结果中高电平所占的比例,来实现精确判断共模比较电路的输出电平.共模校准时,共模校准控制电路在适当的时间读取Err的值,来判断所检测的共模点的共模电荷的高低,由此来调整相应的控制电压VFB,从而达到共模电荷校准的目的.

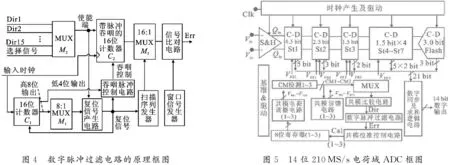

图4给出了数字脉冲过滤电路的原理框图,包含了2个16位计数器,其中C2是具有脉冲吞咽功能的计数器.只要M1的输出为高电平,复位电路即输出复位信号.M2前端的Dir1~Dir15分别表示共模比较电路15次的比较结果.电路工作顺序如下: 当M2选择出的某个信号为高电平时,说明某个共模电荷检测电路输出为高,使能端输出一个脉冲控制复位信号产生电路将复位信号由0变为1,启动C1开始计数;吞咽脉冲控制电路也开始工作,输出一个与主时钟16分频、占空比为0.5的时钟;C2开始计数,其数值是C1的 1/16;C1计满后(M1输出变为高电平),复位信号产生电路输出复位信号,C1和吞咽脉冲控制电路被复位; 扫描序列发生器开始工作,输出4位扫描脉冲,依次输出0~15共16个状态,使得C2中的每一位都被扫描输出; 窗口信号发生器产生一个参考数值信号,用于和C2被M3选择输出的信号进行比较,并输出标志位Err.

图4 数字脉冲过滤电路的原理框图图5 14位210MS/s电荷域ADC框图

3 校准电路在14位210 MS /s ADC中的应用及测试结果

文中所提出的高精度共模电荷误差校准电路被运用于一款14位 210 MS/s 电荷域流水线ADC中进行验证.图5所示为采用该校准电路的14位 210 MS/s 电荷域流水线ADC的结构框图,其在文献[12]中给出的12位 250 MS/s 电荷域ADC内核的基础上,将第1级2.5位子级电路升级为4.5位子级电路,其余各级电路保持不变.时钟产生和基准电压产生电路继续沿用文献[12]所采用的单元电路.

整个ADC中前4级流水线子级电路之间使用了3个共模前馈电路,VFF1、VFF2和VFF3分别补偿第2级、第3级和第4级子级电路的输入共模电荷误差.为校准电容非线性带来的共模电荷误差,ADC使用了3个共模电荷调整电路和对应的3个8位寄存器,VFB1、VFB2和VFB3分别精确控制第1级、第2级和第3级子级电路的共模电荷.整个共模电荷误差的校准工作受共模校准控制电路控制,校准过程中前3级电路的共模校准通过MUX电路公用一个共模比较电路.

共模电荷误差的校准工作开始时,ADC首先进入前台校准模式,共模校准控制电路会将第1级流水线子级的差分输入端短接,并连接到输入共模电压,此时输入共模电荷误差对ADC的影响可以忽略.其次,3个共模检测电路被依次开启,对前3级电路由电容非线性所引起共模电荷误差进行检测和统计处理,然后由共模校准控制电路进行运算,依次对3个8位调整寄存器进行赋值,依次产生VFB1、VFB2和VFB3并保持不变; 最后,共模校准控制电路开启3个共模前馈电路,并将第1级流水线子级的差分输入端从共模电平切换到采样保持电路的输出.ADC结束共模电荷前台校准模式,进入正常工作模式.

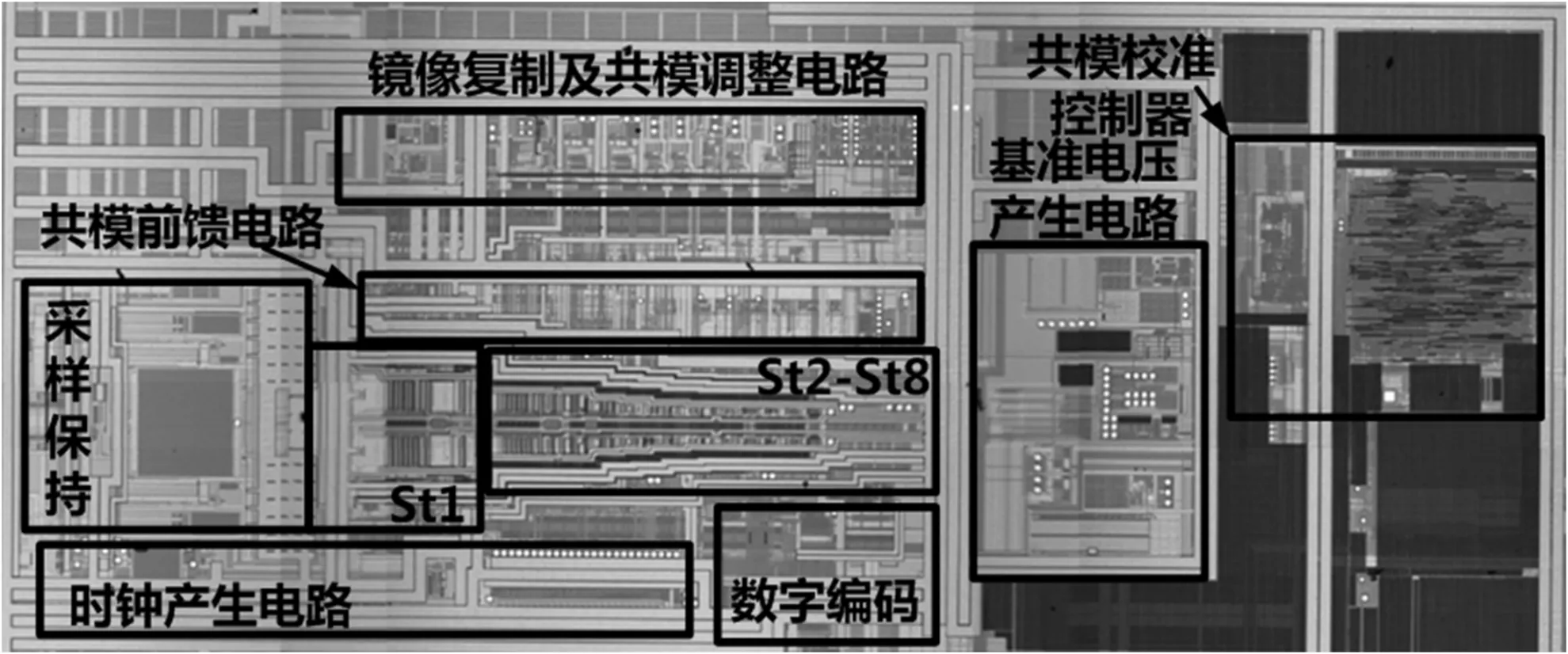

图6 14位210 MS/s ADC芯片照片

4 测试结果及分析

采用文中校准技术的14位210 MS/s电荷域流水线ADC采用 1.8 V 0.18 μm 1P6M CMOS工艺流片,样片芯片的放大照片如图6所示.14位ADC芯片布局与文献[12]基本一致,主要区别在于增加了文中所提出的高精度共模电荷误差校准电路,包括共模校准控制器和共模调整电路,另外还增大了采样保持电路和第1级流水线子级电路的信号处理电容.图中芯片上部为镜像控制及共模调整电路,中间部分从左向右依次为采样保持电路、第1级4.5位流水线子级电路(St1)和其他各级流水线子级电路(St2~St8),下部为时钟产生电路和数字编码逻辑电路.整个ADC电路去除PAD和ESD保护电路以外的有源芯片面积为 1.5 mm× 3.6 mm,其中采样保持和各级流水线子级电路面积为 1.5 mm× 2.1 mm.

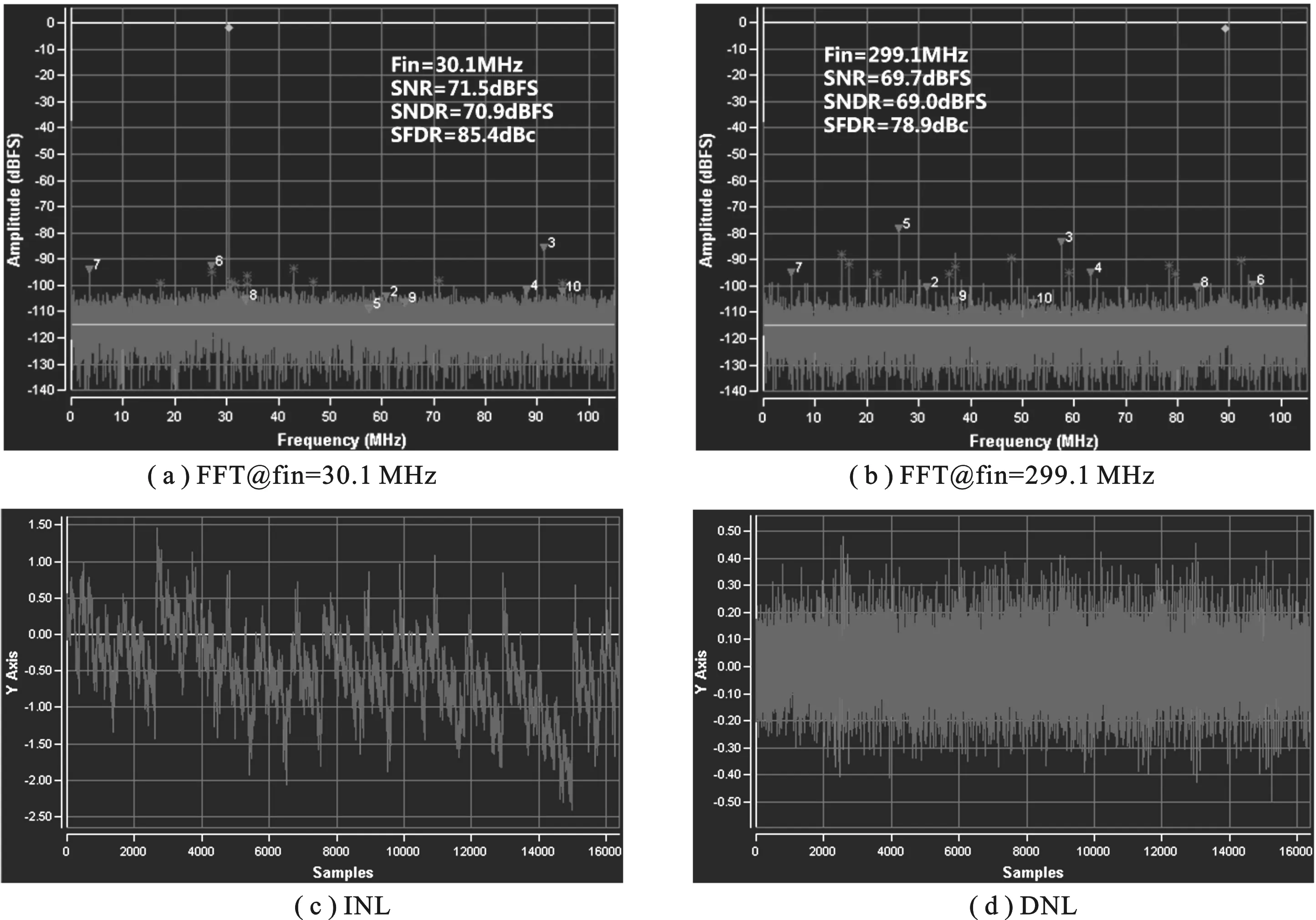

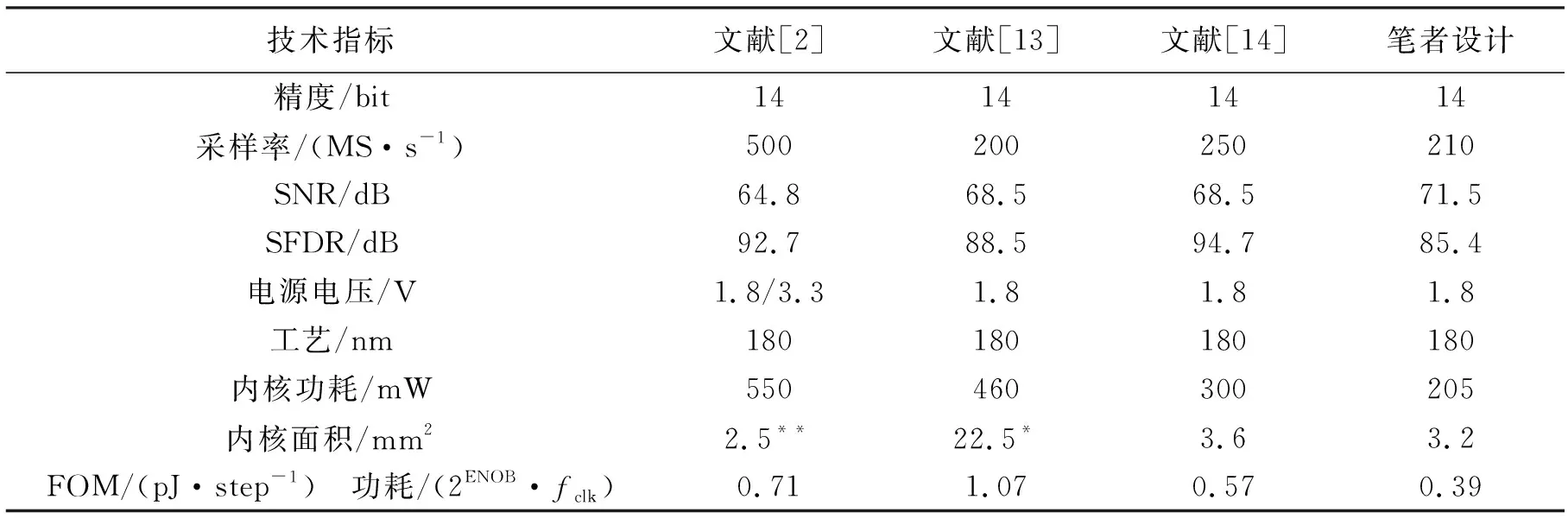

图7为ADC测试得到的典型曲线.图7(a)所示为FFT频谱图,14位ADC在采样率为 210 MS/s 时,对于 30.1 MHz 单音正弦输入信号转换得到的无杂散动态范围(Spurious Free Dynamic Range,SFDR)为85.4 dBc,信噪比(Signal-to-Noise Ratio,SNR)为 71.5 dBFS,信噪失真比(Signal to Noise and Distortion Ratio,SNDR)为 70.9 dBFS; 对于 299.1 MHz 单音正弦输入信号转换得到的SFDR为 78.9 dBc,SNR为69.7 dBFS,SNDR为 69.0 dBFS.图7(b)为采用码密度统计法测试得到的ADC线性度曲线,从图中可以看出,最大微分线性度(Differential NonLinearity,DNL)为 +0.48/ -0.5 LSB,最大积分线性度(Integral NonLinearity,INL)为 +1.5/ -2.5 LSB.由图中的INL曲线可以看出,由于ADC第1级子级电路采用了4.5位子级电路,比较大的误差出现在16个比较器对应的量化区间交界处.表1所示为近年来文献报道的14位高速流水线ADC与笔者设计的14位电荷域ADC性能的对比情况.可以看出,文中设计的电荷域流水线ADC在采用了适中芯片面积条件下,达到了最佳的品质因数(Figure Of Merit,FOM)性能,SNR较相同工艺条件下的其他文献提高了 3 dB 以上.

图7 ADC实测曲线

表1 ADC性能对比

5 结 束 语

笔者提出了一种数模混合型高精度共模电荷误差校准电路,可以对电荷域ADC中各流水线子级内电容非线性引起的共模电荷误差进行精确补偿.所提出的高精度共模电荷误差校准电路被运用于一款14位 210 MS/s 电荷域ADC中.测试结果显示,该14位ADC电路在 210 MS/s 条件下对于 30.1 MHz 单音正弦输入信号得到的SFDR为 85.4 dBc,SNR为 71.5 dBFS,而ADC内核功耗仅为 205 mW.所提出的数模混合共模电荷误差校准电路可满足高精度电荷域流水线ADC的应用需求.