基于自动对齐算法的Python300图像传感器接口逻辑电路设计

2018-11-14南京邮电大学

南京邮电大学 王 翔

图像传感器按照接口数据传输方式可分为并行接口图像传感器和串行接口图像传感器,LVDS接口的图像传感器是串行接口图像传感器的一种,可以提供很高的帧率和抗干扰传输能力。图像传感器的逻辑接口,负责接收传输过来的原始图像数据,并进行解码、时序同步等操作,输出相应分辨率的图像数据,供后续处理或者显示。字对齐操作是指在高速的LVDS串行数据中找到正确的起始采样点,它是将LVDS高速串行数据恢复成低速并行数据的重要步骤,也是后续数据处理的前提条件。针对LVDS接口的Python300图像传感器逻辑接口设计,提出一种自动对齐算法,能够自动寻找LVDS数据中的同步码,完成字节对齐,恢复出正确的数据。仿真并且在ZYNQ平台上实现自动对齐算法和接口逻辑,实验表明,自动对齐算法能够更快速准确地完成LVDS数据的字对齐,CRC校检无误,并且通过后续同步通道解码、重映射等模块,能够产生正确视频格式数据,图像显示正常。

引言:机器视觉的不断成熟与发展,使得其应用面越来越广泛。图像采集部分是一个完整可靠机器视觉系统的入口部分,也是关键部分(熊晓薇.基于FPGA的视频图像处理的研究与实现[D].河北大学,2010)。图像采集部分包含图像传感器,以及连接图像传感器的接口逻辑部分。图像传感器负责图像的成像,以及原始图像输出(李守政,汤斌,欧红师,等.一种基于FPGA的CCD图像传感器驱动系统设计[J].国外电子测量技术,2014(1):80-84;祝长锋,肖铁军.基于FPGA的视频图像采集系统的设计[J].计算机工程与设计,2008,29(17):4404-4407)。很多情况下,原始图像数据,如RAW格式图像,并不能够直接显示,也不能进行边缘检测等后续图像处理操作,而需要通过逻辑接口部分进行信号转换、解码等操作,使之变成常见格式的图像数据(刘宏,符意德.基于Zynq芯片的图像处理系统平台设计[J].计算机与现代化,2015(8):43-47)。

逻辑接口通常有专用电路、单片机/微控制器(MCU)、FPGA等多种实现方式。专用电路速度快但造价高、开发难度大,且适应性窄,当需要更改功能或添加功能时,则需要重新设计电路,制作芯片,不够灵活。单片机/微控制器处理能力有限,速度与带宽会是处理高帧率、高分辨率图像的瓶颈。FPGA设计逻辑接口较为灵活,利用其内部逻辑资源并行处理的优势,可以实现高带宽、高分辨率的图像采集与处理,同时也具有非常大的灵活性,如果需要更改或升级功能,只需要更改代码,重新综合实现即可。

常见的图像传感器按照图像数据的输出方式,可分为并行总线接口传感器和串行总线接口传感器。并行总线接口图像传感器以并行的方式输出图像数据,相同带宽下时钟速率要求低。串行总线接口传感器中,像素数据按照位的形式,依次在总线中传输,接收端需要相应处理,将数据恢复成并行形式。

串行数据线可以避免并行数据线在高速信号平行传输的线间串扰问题,因此串行数据图像传感器可以工作在很高的时钟频率。串行接口按照传输线可分为单端接口与差分接口,差分接口中每一路信号用一对差分线表示,可以提供更强的抗干扰能力,例如LVDS接口就是典型的差分串行接口。

得益于LVDS接口的高速传输特性,因此LVDS图像传感器可以提供很高的数据传输带宽,也就提供了很快的传输帧率。但相比于并行数据传输,LVDS接口数据需要进行字对齐,即找到串并转换时正确稳定的采样起始点,才能把高速的串行数据按照特定的位宽恢复出来,供后续模块处理。对于带源同步时钟的LVDS接口,可以直接通过源同步时钟和配套的解串行模块完成字对齐操作。而没有提供源同步时钟的LVDS接口器件,可以利用同步码完成字对齐操作。对于这一种方式,通常有两种方法,第一种是手动对齐,也就是人为的设定相位延迟长度,在LVDS源数据产生之后,通过内部的相位控制模块,进行相位延迟,等到预设的延时长度到达之后,就将当前位置作为数 据LVDS数据采样的开始,也就是第一个字的起始位置;第二种方法是使用自动对齐算法,通过该算法,可以自动地在LVDS数据中进行搜索,直至搜索到同步码,完成字对齐操作。

对于LVDS接口的图像传感器,需要设计相匹配的对齐模块完成正确的字对齐操作,才能保证后续同步通道解码模块从原始图像数据中恢复成帧开始、行开始、图像数据等信息。这些数据通过CRC校检无误后进行重映射,对像素顺序重新排列,在按特定分辨率的标准视频消隐进行同步,输出图像帧,传送到后续模块(陆佳华,潘祖龙,彭竞宇.嵌入式系统软硬件协同设计实战指南[M].机械工业出版社2014;李列.FPGA低功耗设计相关技术研究[D].中南大学,2010)。

1 整体逻辑接口设计

图1 逻辑接口整体设计

如图1所示,整体Python300图像传感器逻辑接口由6个部分组成:自动对齐模块、同步通道解码模块、CRC校检模块、重映射模块、fifo模块、640*480P标准时序产生模块。

自动对齐模块完成LVDS入口数据串并转换操作,自动对齐算法也在该模块中实现。自动对齐的目的是完成字对齐操作,找到稳定采样点,从该点进行采样可以将高速串行信号准确地转化为并行信号。对于CMOS图像传感器Python300,其接口为4路LVDS数据信号加1路LVDS同步信号,这5路信号经过自动对齐模块成为5路并行信号,送入同步通道解码模块。

摄像头输出的数据为原始RAW格式数据,其中数据通道与同步通道的数据存在对应关系,同步通道中存在不同的同步码,每一种同步码对应数据通道不同的状态信息,如帧开销、行开销、帧开始、行开始、帧结束、行结束、有效像素数据等信息。同步通道解码就是根据这些同步码,解析出对应的状态信息,传递给后级模块。

CRC(循环冗余校检)校检模块用以校检摄像头数据的正确性,对于每一路数据通道,该模块都进行CRC校检,并输出校检结果。重映射模块将四路数据通道的顺序按照传感器技术手册中的要求,重新做调整,使像素数据输出排列正确,不发生偏斜。

整个的逻辑接口目的是输出640*480P的视频格式数据,640*480P时序产生模块产生标准时序,包括行同步、场同步、有效数据信号。该模块与重映射模块通过FIFO连接,并将经过重映射之后调整过顺序的像素数据同步到标准640*480P的时序下面。

2 自动对齐模块设计

2.1 总体设计

图2 自动对齐模块整体设计

同步码自动对齐算法的目的在于自动地在高速串行数据流中找到相应的同步码,并且保证在有效数据中突然出现的,与对齐码相同,但不是对齐码的数据,不会使自动对齐算法做出错误判断。

整体的自动对齐模块设计如图2所示,输入数据为LVDS信号,输出数据为解串行并经过对齐后的并行数据以及相应的对齐状态。内部实现主要由三个模块组成:串并转换/相位控制模块、同步握手模块、自动对齐算法状态机模块。

串并转换/相位控制模块接收LVDS信号,并将差分信号转换为单端信号,随之经过IODELAY2和ISERDES2进行相位控制和转并行输出。而其中相位控制和ISERDES2的位偏移控制来源于自动对齐算法状态机。

同步握手模块沟通串并转换/相位控制模块和自动对齐算法状态机模块,当自动对齐状态机需要当前数据的时候,即与同步握手模块建立握手连接,由同步握手模块向串并转换/相位控制模块申请实时解串行的数据,并传送给自动对齐算法状态机。自动对齐状态机在运行自动对齐算法的时候,会根据当前的数据,得出相位偏移和位偏移控制信息,并传递给同步握手模块,而同步握手模块则将此信息提供给串并转换/相位控制模块。

自动对齐状态机则负责在高速串行的数据流中寻找同步码,并且需要剔除干扰情况,并保存搜索到正确同步码时的相位信息和ISERDES2位偏移信息,并提供给串并转换/相位控制模块。

2.2 同步握手部分设计

同步握手模块向串并转换/相位控制模块申请数据,而自动对齐状态机通过握手操作从同步握手模块中得到数据。握手操作是通过req/ack这一对信号线进行操作并完成握手过程的,当握手完成之后,自动对齐状态机接收到的数据为有效数据。

自动对齐状态机通过自动对齐算法在高速的串行数据流中寻找同步码,在寻找过程当中,会根据情况调整对于串并转换/相位控制模块的控制信息,即相位偏移和位偏移控制信号。自动对齐状态机将这些信号提供给同步握手模块,而同步握手模块将信号同步给串并转换/相位控制模块。同步握手模块是沟通自动对齐状态机和串并转换/相位控制模块的桥梁,后两者工作在不同的时钟频率上,利用同步通道握手模块可以同步两个时钟域的数据与控制信号,并且减少这两个模块直接相连时的耦合性,有利于综合器综合出更加合理的电路与布局。

2.3 串并转换/相位控制部分设计

串并转换/相位控制模块是整个自动对齐模块的入口模块,它接收输入的LVDS的数据,并将LVDS数据经过差分转单端、相位延迟、高速串并转换转化为并行数据输出。

IBUFDS部分将LVDS差分信号转化为单端信号,接着提供给IODelay2模块。

IODelay2模块可以将高速串行数据相对于采样点做相位控制,具体的操作为相位延迟,它可以对输入数据做0至31拍的相位延迟,每一拍的长度为5ns。具体的延迟拍数由自动对齐状态机中自动对齐算法调整得出,并通过同步握手模块同步提供,其目的主要是保证高速串行数据的采样点能够稳定在每比特数据的中间位置,避免采样点在相邻比特的边缘位置,导致亚稳态的产生。

经过IDelay2模块进行相位延迟后的数据输入至Iserdes2模块。该部分可以对于高速的串行信号做串并转换操作,具体的转换位宽为1:10,即每一路LVDS信号通过Iserdes2都转化为位宽为10位的并行信号。

Iserdes2的Bit滑动控制信息由自动对齐状态机提供,并通过同步握手模块同步给该部分。

2.4 自动对齐算法状态机设计

在没有源同步时钟的LVDS信号当中,通常会存在有大量的同步码,以供接收器进行搜索同步,完成自对齐操作。

图3 自动对齐状态机的工作流程

自动对齐状态机的工作流程如图7所示,沿检测即数据有效性检测,在串行数据流中,很可能有长串的低电平,而同步码不为0,所以这些低电平中并不存在有同步码,对于自动对齐状态机来说为无效数据,进行沿检测即保证自动对齐算法状态机通过同步握手模块得到的数据不为0。

当数据不为0的时候,自动对齐状态机完成沿检测状态,进入下一个状态。LVDS数据为高速串行数据流,在每一路通道中,字数据按照比特流的形式依次传输,在进行串并转换的过程当中,使用与数据速率相对应的时钟,对于串行数据流进行双边沿采样,得到并行数据。不过这些数据可能出现相位误差,如下所示,时钟的上升与下降沿可能位于串行比特流的相邻比特位置,从而导致不能满足建立时间和保持时间的要求,引起亚稳态的发生:

因此需要通过相位移位来确保采样位置不会出现在相邻比特的交界位置。IODelay2模块可以进行0到31拍的相位延迟,利用此特性设计如下方法找到稳定采样点,避免采样在相邻比特位边缘位置,发生亚稳态的情况:

a.设定当前点为起始采样点;

b.从当前点开始,进行相位延迟,范围从0至31拍;

c.如果一直延迟到31拍,串并转换后的数据没有发生变化,那么更新当前采样点为原采样点进行相位延迟31拍的位置;

d.如果串并转换的数据发生改变了,意味着相位延迟使得采样点从当前比特偏移到了下一个比特,假如刚刚发生数据改变对应的偏移为n,如果n大于32,那么更新当前采样点为原采样点进行相位延迟n/2拍的位置;

e.如果n小于12,那么更新当前采样点为原采样点延迟n+(31-n)/2拍的位置;

f.如果n介于12到16之间,那么当前采样点的位置不发生变化。

对于工业CMOS传感器Python300,其LVDS同步码为0x3a6,则在行开销和帧开销期间,有大量的同步码,在确定不会发生亚稳态情况的当前采样点之后,就可以在数据中搜索同步码,但此时还不能保证从当前采样点采样,串并转换之后的数据就是同步码0x3a6,还可能是其循环移位的其他数据。所以在采样点稳定后,在帧开销和行开销间,能够从高速LVDS串行数据中解出的并行数据中找到0x3a6或者其循环移位数据。

a.待找到0x3a6,则直接进入干扰排除过程;

b.如果找到的是0x3a6的循环移位数据,自动对齐状态机会产生比特位滑动控制信号,通过同步握手模块传递给串并转换/相位控制模块中的Iserdes2部分进行比特位滑动,调整采样点,直至串并转换得到的数据为0x3a6,随后进入干扰排除阶段。

之所以要进行干扰排除,是因为在有效数据阶段,LVDS通道内可能产生和同步码一致的数据,即0x3a6,为了防止这些数据让自动对齐状态机发生误判,则需要排除这些偶然情况,以免干扰对齐结果。

稳定性检测部分中,其第一步是数据不变性检测:因为对于工业CMOS传感器Python300而言,每一帧前的帧开销和每一行前的行开销中会存在有一长串连续的同步码。所以在之前步骤搜索到了同步码型0x3a6之后,其后续的数据依然会是同步码型0x3a6,也就保证了有效像素数据中,偶然出现的,与同步码型相同的孤立数据不会影响对齐结果。如果之后的数据依然是同步码型0x3a6,那么通过了数据不变性检测;

第二步是1比特滑动检测:该步骤是进一步确定同步码型的稳定性,即通过Iserdes2使采样点发生移位,串并转换得到的数据也会发生比特偏移,在同步通道中,同步码连续出现,当正确采样点左移一位,则串并转换结果为同步码循环左移一位数据;

第三步是2比特滑动检测:与第二步类似,该步骤是最终确定当前与同步码型相同的数据就是同步码,即通过Iserdes2是采样点左移2个比特,那么串并转换得到的数据应该是同步码循环左移2比特的数据。

如果这三个步骤完成,那么稳定性检测部分结束,可以认定,同步码型搜索完成,当前的采样点就是所需要的对齐起点,自动对齐过程也随之完成。

3 实验结果分析

为了验证自动对齐算法的有效性以及整体逻辑接口的功能,在FPGA+ARM架构的ZYNQ平台上设计自动对齐算法以及逻辑接口。经过仿真、综合、添加约束、实现之后,使用在线逻辑分析仪(ILA)上板调试,工业CMOS图像传感器Python300传输数据为4路LVDS的RAW格式图像,经过自动对齐算法模块经过设计的步骤,自动在数据当中搜索同步码型,并且进行相位控制和比特位滑动控制,最终找到稳定采样点。

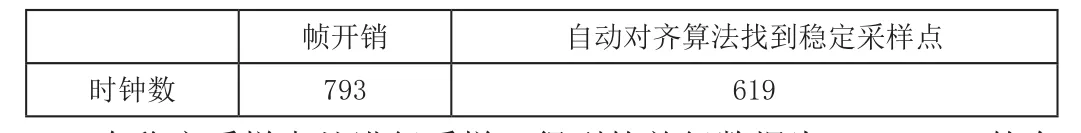

设计的逻辑接口工作在6.3MHz时钟频率下,如表1所示,通过实验得到帧开销长度为793个时钟周期数,而寻找到同步采样点需要619个时钟周期,可以在第一帧图像开始前完成对齐。

表1 自动对齐算法的时钟耗费

在稳定采样点处进行采样,得到的并行数据为Python300的有效帧数据,与官方提供的帧结构一致,不会发生相位偏移、错位等情况,后续经过同步通道解码模块可以按照帧结构对于数据进行解码,恢复出有效像素数据和行场同步信息,再经过重映射模块将4路信号整合成一路,并用标准的640*480P的时序产生模块进行同步,就可以产生视频流数据,输出至显示器上可以看到稳定清晰的图像,表明自动对齐算法运行有效、整体逻辑接口也工作正常。

图4 原始图像数据经逻辑接口处理得到的清晰图像

4 结论

本文提出了一种基于自动对齐算法的Python300图像传感器逻辑接口设计,并在ZYNQ平台上设计了自动对齐算法模块和整体的逻辑接口。通过实验,本设计可以很好地找到稳定采样点,并将LVDS图像数据进行正确的串并转换,供后续模块进行同步解码和时序同步,并输出稳定清晰的图像。本设计对于LVDS接口的摄像头具有一定通用性,可以自动寻找同步码型并设置稳定采样点。另外将设计在ZYNQ平台中的FPGA上进行了验证,进一步提高了算法的应用范围,具有很好的应用前景。