双乒乓模式实现视频融合

2018-11-14太原航空仪表有限公司贾万春

太原航空仪表有限公司 贾万春

现代飞机座舱显示系统要求高分辨率大屏幕显示,这对图形处理器的速度要求越来越高.本文重点介绍FPGA如何实现双双乒乓模式,采用双图形处理器的构架,各输出1024×768的视频信号,通过FPGA进行拼接融合后输给液晶显示屏,有效避免了图形处理器速度的瓶颈,实现了高分辨率大屏幕显示。

1.FPGA的设计

本设计的关键是建立在Altera的FPGA(EP2S60F1020I4N)基础上,开发片上处理系统。该设计是在Quartus II9.0完成。

图像最终输出分辨率为1560×1080@60Hz像素时钟为119.5 MHz,外部RAM速度为100 MHz,如果采用高速RAM 将会带来更高成本,而外部输入1024×768@60Hz像素时钟为65 MHz,所以采用双乒乓模式实现图像合成,即FPGA外部RAM和内部RAM,片外RAM的主要作用是储存外部输入的1帧图像,通过外部RAM写地址控制器和外部RAM读地址及读写操作控制器控制,同时将图像扭转90度。此时写外部RAM频率为65MHz,读外部RAM的速度为60 MHz,乒乓切换控制靠液晶屏驱动时序场信号分频来完成。

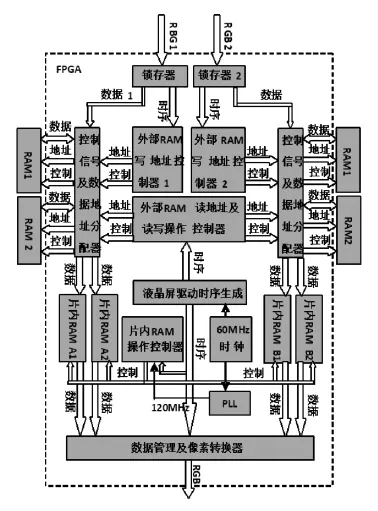

图1 系统结构框图

将同一时间从两片外部RAM中读出的两行数据同时放入两片内部RAM中,通过片内部RAM操作控制器控制片内部RAM,读内部RAM的速度为120MHz,读地址分为高位地址和低位地址两部分,顺序读取两片片内RAM,可以有效显示一行,显示时左半屏为第一路视频图像,右半屏为第二路视频图像,完成图像合成(见图1)。

1.1 同步的设计

系统输入的时钟信号为两部分组成,一部分为外部图像输入的65 MHz像素时钟,一部分是系统自带的60MHz时钟。60MHz时钟倍频后是为驱动液晶屏119.5MHz像素时钟所用,而在操作外部RAM时它是作为取数据地址产生的源头。两部分时钟频率不同但刷新频率一样,同为60Hz,所以采用输人视频信号的场同步一次分频作为同步控制信号,也作为以下读取外部RAM的读/写控制信号。

1.2 外部RAM写地址控制器的设计

将外部输入图像的时序的时钟信号在使能信号有效情况下进行分频计算出行地址,将使能信号在场信号有效情况下分频计算出列地址,地址寻址空间为1024×768,将输入图像场信号一次分频作为读写操作的控制信号。

1.3 外部RAM读地址及读写操作控制器的设计

将系统输入60MHz时钟在液晶屏驱动时序生成器输入的使能信号有效的情况下分频计算出读外部RAM的行地址,将液晶屏驱动时序生成器输入的使能信号在其输入的场信号有效的情况小分频计算出读外部RAM的列地址,寻址空间为780×1080,将其旋转90度后变为1080×780,完全覆盖写入数据空间,将输入图像场信号一分频作为读操作控制信号。

1.4 控制信号及数据地址分配器的设计

根据读/写操作控制信号指令,在写操作有效时将外部RAM写地址控制器输入的写外部RAM地址、写操作控制信号发送给外部RAM,同时将FPGA数据总线设置为输出模式把外部图像数据发送给外部RAM。

在读操作有效时将外部RAM读地址及读写操作控制器输入的读外部RAM地址、读操作控制信号发送给外部RAM,同时将FPGA数据总线设置为输入模式把外部RAM数据读入FPGA的内部RAM中。

1.5 片内RAM操作控制器的设计

将液晶屏驱动时序生成器输入的120MHz像素时钟信号在其使能有效的情况下分频计算出读地址,读地址分为高位地址和低位地址两部分,大于780为高位地址,小于780为低位地址,所以顺序读取两片片内RAM形成一行完整数据。将60MHz时钟频率在使能有效的情况下分频计算出写地址,使能信号一分频作为读/写内部RAM控制信号。

1.6 液晶屏驱动时序生成器的设计

将外部输入60MHz时钟信号经过PLL输出120 MHz作为基准时钟计数进行行同步信号生成,以120 MHz基准时钟的11分频(此频率和行同步频率相同)作为基准计数进行场同步信号生成。根据Vesa标准产生液晶屏驱动信号。

2.结论

此设计已完成调试,并应用于实践,性能稳定,成本低、功耗小,实现了高分辨率大屏显示,达到预期效果。

参考:闻建明,FPGA芯片在视频图像实时处理中的应用:计算机应用,2009。