红外焦平面像素级数字化技术最新进展

2018-08-28李敬国刘泽巍

于 艳,李敬国,刘泽巍

(华北光电技术研究所,北京 100015)

1 引 言

红外焦平面的数字化实质上是红外探测器信号读出电路的数字化,而信号读出电路是属于微电子集成电路的范畴,因此,超大规模集成电路设计和制造技术是实现红外焦平面数字化的支撑技术。随着集成电路设计、制造技术的飞速进步,能够获得线宽更小、集成度更高的数字化/智能化读出电路芯片。更进一步地可将许多传统红外探测器组件后端电路所完成的功能集成在焦平面读出电路中实现,例如:信号的模数转换(ADC)、非均匀性修正(NUC)、甚至实现图像处理、片上系统(SoC)等,这些技术的发展不但提高了探测器的性能和信息处理能力,还能够简化探测器接口、减小探测器的体积和重量、提高探测器的抗干扰能力。

模拟数字转换器(ADC)是数字化焦平面的基础,本文将简要叙述红外焦平面片上ADC的几种架构方式及其优缺点,重点分析几种典型的像素级ADC结构的工作方式及其对红外焦平面探测器的性能影响,最后将介绍国外像素级数字化技术最新进展情况。

2 红外焦平面片上ADC简介

红外探测器读出电路片上ADC的设计是数字化焦平面的最核心技术,不同于集成电路中的ADC模块,其结构参数设计受限于探测器有限的像素面积,应用于制冷型探测器中还要受到功耗方面的约束。

传统读出电路将探测器感光后输出的微弱电信号积累、放大、处理并顺序输出。通常是由输入级、列放大级、输出级和时序控制电路组成,其中除了一些简单的控制电路为数字电路以外,对探测器信号的处理均是在模拟域完成的,如图1所示。

图1 传统读出电路架构组成Fig.1 Composition of traditional readout circuit

读出电路的数字化就是要将AD转换等功能放在读出电路上实现,使其最终输出的信号为数字格式,从而提高其抗干扰能力。通常片上ADC的架构方式有三种:芯片级的AD转换结构、列级的AD转换结构和像素级的AD转换结构[1],如图2所示。 芯片级ADC就是将ADC置于传统读出电路输出最末端,因此,信号处理的大部分其实仍是以模拟的方式进行,只是在输出级之后完成AD转换,其对信号噪声性能的提高作用不明显,且由于ADC的转换速率等于探测器信号读出速率,速度较高而容易引起较大的时钟噪声、容性耦合噪声和较高的功耗。因此芯片级ADC架构方式较少被采用。

列级的ADC方式是目前发展较为成熟,也较多被国外公司采用的片上ADC架构方式。列级ADC是一列(或多列)探测器单元共用一个ADC,因而省去了原来的列驱动放大器以及输出驱动电路,使信号通路上的模拟电路减少了,且输出至片外的因而对噪声性能的提高有一定的作用。但集成了列级ADC的处理电路所处理的探测器信号量并没有本质的改变,所以对探测器性能的提升有限。列级ADC结构和参数设计受像元中心距一定的限制,转换频率通常等于探测器行频,相对属于中速ADC转换,当像元中心距较小、帧频较高和阵列规模较大时,设计难度也随之加大。

像素级ADC结构是在每一个像素内实现AD转换,探测器的微弱信号经过简单的耦合流入读出电路直接被转换成数字格式,因而后续的传输、处理都是针对数字信号。像素级ADC的转换频率通常等于帧频,所以ADC的转换速率可以非常低,功耗小;焦平面阵列和外围接口之间的通信均为数字信号,因此可大大提高整个芯片的噪声性能;由于结构的特殊性,可以采用一些技术来增加电荷处理能力,提高探测器信号处理量,对提高探测性能非常有利。另外,采用像素级ADC结构实现焦平面数字化时,数字信号便于做进一步处理来进行焦平面读出电路的控制,比如,曝光控制、盲元替代,在芯片上也可以实现图像处理功能以降低片外硬件的需求。像素级ADC结构受到非常苛刻的面积限制,版图实现难度极高,因此在初期因集成电路制造工艺水平的限制而未得到广泛的发展,而近年来随着集成电路制造工艺尺寸的不断缩小,越来越多的国外公司已通过研制具有像素级ADC的数字化读出电路使红外焦平面的性能不断接近理论极限值,探测水平极大提高。

3 典型像素级ADC结构

众所周知,集成单片ADC电路模块可以有多种实现方式:全并行式(flash)、流水线式(pipeline)、逐次逼近式(SAR)等。而用于红外焦平面探测器读出电路中的像素级ADC对像元面积、填充因子以及功耗都受到非常苛刻的限制,因此并不是所有的ADC电路结构都适用。目前被国外公司较多采用的结构主要有三种:斜率型ADC(single slope)、过采样ADC(Σ△ADC)、脉冲频率调制型ADC(PFM)或称电荷包计数型以及两步转换型ADC(Residual-Counting)等。

3.1 斜率型像素级ADC

单斜率型ADC属于间接转换的一种,具有转换精度高,抗干扰能力弱的特点。它通过电压-时间变换把模拟电压量变成时间量,该时间间隔内对时钟脉冲进行计数,再对计数脉冲进行编码、锁存得到相应的数字量。它由积分器、比较器、计数器、时钟脉冲发生器和一些控制逻辑组成,时间间隔的长短与模拟输入电压成比例。其原理和时序示意图见图3。单斜率型ADC对斜坡电压要求很高,线性不良会带来转换误差,一般采用外部输入。对于N位转换器,完成一次转换最慢需要2N个时钟周期。

斜率型ADC包含的电路模块较多,因此面积庞大。为了将这种结构的ADC集成到像素单元内,常用的方法是将计数器模块放在像素之外,采用多元共享的方式,而像素单元内仅产生控制“时间间隔”的脉冲用于将当前的计数值锁存下来。甚至也有将全部输入级和ADC电路都共享的方式,进一步解决像素面积和功耗方面的限制[2]。

3.2 过采样ADC

红外探测器用像素级Σ△ADC ,它通常由调制器和数字低通滤波器构成,输入模拟信号经过调制将量化噪声推到了高频部分即信号带宽以外,然后通过数字抽取滤波器滤除量化噪声,从而能够实现较高分辨率的AD转换结果,如图4所示。其工作原理是探测器生成的光电流经电容积分,积分周期结束时获得一个采样电压,电压经过由过采样时钟CK1控制的比较器量化,量化值经过一位DAC转换为电荷反馈到积分电容。每个时钟周期,比较器产生一个位码,经位线读出。尽管所产生的位码的不可预测,但是通过比特(bit)流的统计特性就可以反映模拟信号的幅度,即通过数字滤波器来完成bit流统计。

图4 一阶∑△ADC原理框图Fig.4 Schematic diagram of one order ∑△ADC

提高∑△ADC信噪比的方法有:过采样、噪声整形和多位量化。一阶一比特∑△ADC调制器的信噪比与过采样率(OSR)的关系下:

SNRmax=30log(OSR)+2.61

(1)

可见,对于一阶Σ△调制器,过采样率的加倍能使动态范围增加9dB,相当于分辨率增加约1.5bit。例如要实现转换精度15bit的ADC,一阶Σ△调制器需要的OSR约为950。在实际电路中,通常OSR不会超过512。在这种情况下,可以考虑用高阶调制器或多位量化,高阶调制器可以减小输出频谱中的谐波,但电路规模会随之增大。

与调制器配合需要设计数字抽取滤波器,它将高速的一位数据流转换成低速的数据流。数字滤波器完成的平均作用相当于频域里的低通滤波一般需要实时、高速完成复杂的信号处理算法,所以面积较为庞大[3]。

美国Amain公司在2000年研制的640×480,27μm中心距数字化中波探测器样品,其中的像素级ADC实现方式就是二阶∑△ADC结构,ADC精度12.6bit,电荷处理能力70Me-。Amain公司将比较器部分放在像素外采用一列共用一个的方式以降低功耗[4]。

从图3、4的电路工作原理框图可以看出,单斜率ADC和过采样ADC在进行AD转换前都需要将积分信号采样保持下来,那么在电荷处理量方面就受到一定的局限性,特别是随着CMOS工艺线宽越来越小,且为了降低功耗会逐渐从5V工作电压降低至3.3V、1.8V甚至更低,由此电荷处理量就会进一步减小,对于提升红外探测器的动态范围和信噪比是不利的。

3.3 脉冲频率调制型ADC

目前,还有一种比较常见的电荷包计数型ADC应用于像素级数字化电路中[5],这种结构的ADC处理信号的方式非常特别,如图5所示。

图5 脉冲频率调制型ADC原理框图和工作时序示意图Fig.5 Schematic diagram and timing sequence of PFM ADC

它是将探测器的光电流信号转换为与之成正比的脉冲个数信号,对脉冲个数进行计数,通过计数器输出的数字码来反映探测器光电流的大小。像素单元电路主要由积分电容Cint、比较器、反馈电路和计数器、锁存器等组成。当光照射到探测器时,产生的光电流给积分电容放电,导致了Vint电位的下降,Vint和Vref通过比较器进行比较,当Vint电位低于Vref时,在比较器的输出端产生一个脉冲送至计数器计数,同时经反馈电路将积分电容复位,使Vint的电位回到Vdd,开始下一个放电周期。计数脉冲的周期为:

其中,id为探测器的光电流。从工作波形图可以看出,积分结束则转换完成,在Tint积分周期内,产生了光电流到数码的转换。脉冲频率调制型ADC电路原理简单而且鲁棒性较强,具有较宽的信号输入动态范围。最重要的是,通过多次复位机制可以以很小的积分电容实现超大电荷处理能力,这对提高探测器尤其是暗电流较大的长波探测器的探测灵敏度非常适合。同时,对电荷的多次累加复位可以很好的降低高频噪声,提高AD转换信噪比。脉冲频率调制型ADC的最大电荷处理量用公式(3)计算:

其中,q是单位电荷电量;n是ADC分辨率。假如Qmax的设计目标是2Ge-,取Vdd为1.8 V、Vref为1 V、AD转换的位数是15 bit,则Cint的取值在12 fF左右即可实现。

法国sofradir和美国MIT Licoln Library都有将脉冲频率型ADC即电荷包计数型ADC应用于红外焦平面像素级数字化技术的相关报道[6-9]。法国sofradir(CEA-LETI)在2010年报道的具有像素级电荷包计数型 ADC的长波320×240,25 μm中心距数字化焦平面,能够实现40 ms的积分时间,读出电路最大电荷处理能力接近3Ge-,转换分辨率15 bit,动态范围(DR)为90 dB,NETD为2 mK,单个ADC的功耗仅0.9 μW。

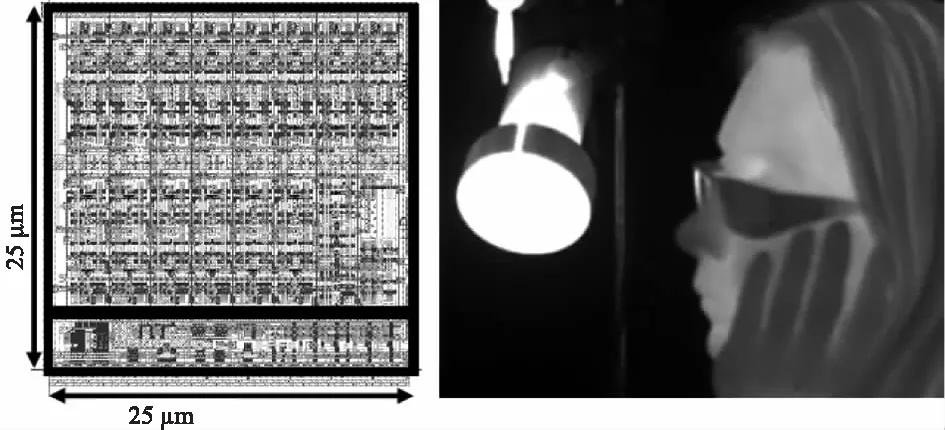

图6 法国研制的像素级ADC版图(左) 和数字化探测器成像图(右)Fig.6 The pixel ADC layout and digital detector IR scene of Sofradir

3.4 两步转换型ADC

PFM型ADC应用于红外焦平面像素级数字化技术中,虽然在动态范围、电荷处理能力等方面具有明显的优势,但随着三代焦平面技术的快速发展,探测器阵列规模从320×256向640×512、1 K×1 K为主流,像元中心距目标直指10 μm以下,这种ADC结构同样将面临面积和功耗的问题。

两步转换型ADC(又称Residual-counting)是在PFM型的基础上开发的新型ADC结构,可以较好地解决面积和功耗的问题,同时仍然能够保证较高的转换精度以及大的电荷处理能力。

图7 两步转换型ADC的原理框图和工作波形图Fig.7 Schematic diagram and timing sequence of residual-counting ADC

图7是两步转换型ADC的原理框图和工作波形图,其中大部分电路与PFM型ADC类似,工作方式也相同,特别之处在于当积分周期结束的瞬间,电荷包计数器产生一个m位的数字量,同时积分电容Cint上会有一个残余(residual)电压Vref,将残余电压采样保持下来后转移至列级ADC,转换生成n位数字量,与像素ADC转换完成获得的m位数字量组合构成分辨率为m+n位的AD转换结果[10-11]。

Residual-counting方法可有效减轻高精度对像元面积的压力,降低功耗,还仍可以保证较大的电荷处理能力,这样既减小了KTC噪声又获得了较低的量化噪声,提高转换信噪比。文献[12]中描述的通过这种方式可以将量化噪声电子数从26000 -减小到200 e-,这在光电流非常小的应用中非常适合。

4 国外像素级数字化技术最新进展

目前对红外焦平面像素级数字化技术研究最多的有法国sofradir、美国MIT以及土耳其、韩国、意大利的一些科研机构。他们都基于以上典型结构研制出了相应的产品或样品,代表了此项技术的最新水平。

4.1 法国sofradir公司

法国sofradir公司联合CEA-LETI基于PFM ADC在2010年研制出具有2 mK峰值探测灵敏度的320×240数字化焦平面样品,具有15 bit并行数字输出信号,测试最高信噪比为90 dB,单个ADC的功耗约0.9 μW。之后在2012年又基于Residual-counting结构研制了320×256,具有16 bit数字输出的焦平面样品,因为像素单元内仅设计了11 bit计数器,低5 bit采用列级flash ADC来完成,所以像素单元的功耗降低0.5 μW,峰值信噪比为88 dB,且仍然保证了3 Ge-的最大电荷处理能力[13]。图8为这款读出电路芯片的原理框图和像素单元版图布局,这两款电路都是采用0.18 μm/1.8 V工艺实现的。

图8 法国研制的两步式数字化读出电路原理 框图和像素级ADC版图Fig.8 Schematic diagram and pixel layout of residual-counting ADC of France

4.2 土耳其自然科学工程院

土耳其的自然科学工程院2015年报道了其研制的像素级数字化焦平面样品及其测试结果[14]。所设计的像素级ADC是基于residual-counting结构,只是在残余电压的量化处理方式上与法国略有不同。用0.18 μm工艺制成的样品阵列规格只有32×32,中心距30 μm,积分电容值为40 fF,AD转换分辨率是14 bit粗分加11 bit精分共25 bit,可实现2.04 Ge-的电荷处理能力,单个ADC功耗仅有0.35 μW。图9是该电路的像素级ADC版图布局图。

图9 土耳其研制的两步式像素级ADC版图Fig.9 Pixel ADC layout of residual-counting of Turkey

在此基础上,他们还研制了90×8数字化时间延迟积分(TDI)红外焦平面样品,遵循TDI读出电路的工作原理,利用的则是像素级输出的数字信号非常便于存储、运算的优势,从而用0.18 μm工艺实现了8元信号累加/平均后的16 bit输出信号[15]。

4.3 MIT Licoln Library

美国林肯实验室在2010年就研制出256×256规格,30 μm中心距的像素级数字化焦平面系列产品,采用的也是PFM型ADC,他们采用90 nm工艺实现30 μm中心距内的最高19 bit AD转换,最低芯片功耗做到了30 mW。此外,他们还在读出电路片上设计了背景减除、盲元替换、非均匀性修正等功能,可以说是智能化焦平面的代表。图10是其读出电路及像素级ADC结构原理示意图。

随着集成电路制造水平的不断提高,MIT采用更小尺寸工艺研制出了更大规格、更小中心距且集成更多片上信号处理功能的智能化红外焦平面产品。从相关报道中已可以看到640×480,20 μm中心距的像素级数字化(智能化)焦平面产品,其片上ADC分辨率从14 bit到21 bit,信号读出速率可以达到串口32 Gbps。更新的产品上设计的计数器是双向计数或高低位计数分别可控的,因此,片上信号处理的功能更加丰富,包括:图像稳定、实时时间滤波和图像锁定放大等等。并且,他们规划的未来的发展目标是采用小于32 nm工艺实现1280×720或4 K×4 K,中心距小于12 μm的像素级数字化焦平面产品[16]。

图10 美国研制的计数型ADC原理框图Fig.10 Schematic diagram of PFM ADC of America MIT

这种smart IRFPA集红外探测器阵列、读出电路、图像信号处理为一体,在探测器单元中进行某些像元级数字化处理,能减小传感器带宽和要处理的数据吞吐量,是对于输入/输出瓶颈问题的解决办法。有了这种技术就能减小IRFPA外部处理电路的尺寸、复杂性和费用,且数据处理更加可靠。

美国加利福尼亚州Santa Barbare研究中心(SBRC)在研制模仿视网膜的“灵巧”(smart)红外焦平面(IRFPA),SBRC是以碲镉汞三层异质结结构为基础的双色探测器来构成smart IRFPA,它在焦平面阵列上完成自动目标识别、非均匀性修正等计算性很强的预处理。美国Amber工程有限公司模仿人的视网膜研制的神经形态IBPPA(NIF),是为美国未来先进的制导导引头提供所需要的smart IRFPA。美国Martin Marietta公司研制的是双色多量子阱探测器构成128×128元smart IRFPA。据报道,美国的“AIM-9X”(响尾蛇)就采用了非均匀性校正与探测器集成的smart IRFPA。

2014年6月,美国导弹防御局宣布授予BAE系统公司940万美元的项目,设计和制造512×512双色高速数字化焦平面阵列。美国导弹防御局希望BAE系统公司设计具有高分辨率、高帧速和先进数字处理能力的焦平面阵列,根据合同,BAE系统公司定于2017年1月完成开发工作。

5 结 论

从以上国外红外焦平面像素级数字化技术最新进展情况看出,国外的红外焦平面数字化技术发展迅速,尤其是美国MIT licoln library的片上图像处理功能已经非常强大,达到智能化焦平面的水平。同时美国的许多大学也在做相关技术的研究。而国内的红外焦平面数字化技术,不论从性能指标还是技术的创新能力方面,发展还是相对落后,需要更多的投入来缩小差距。