TMS320C6678在雷达成像中的应用

2018-08-08董磊,冯媛

董 磊,冯 媛

(西安卫星测控中心陕西渭南714000)

合成孔径雷达作为一种重要的二维高分辨雷达,在测绘、抢险救灾和军事侦察方面均发挥了重大作用。但是其成像处理算法较为复杂,实时处理对硬件的运算能力要求又很高,一直限制着合成孔径雷达实时成像方面的应用。

文中以TMS320C6678为核心,设计了高速运动平台雷达信号实时处理板,并结合改进的距离-多普勒[1-3](Range-Doppler,R-D)雷达成像算法特点,高效分配多核资源,充分发挥了多核DSP(Digital Signal Processor)强大的计算能力和并行处理能力,实现了雷达回波信号的实时处理。

1 硬件结构

为了满足大数据量的并行处理和复杂算法的实时处理,保证数据处理的连续性,硬件平台充分利用了FPGA(Field Programmable Gate Array)密集型并行计算实时性高,DSP处理精度高、资源控制和处理复杂算法灵活的优势,采用乒乓处理方式,硬件采用EP4SGX230+2路TMS320C6678的结构,其硬件框图如图1所示。

EP4SGX230接收模数变换后的雷达中频回波数据,经DDC变换后将对数字基带信号进行部分算法处理、逻辑和接口控制、多路处理,解决并行性和实时性的问题,减轻DSP并行处理的负担。TMS320C6678负责主要成像算法的处理。

FPAG与DSP间、两片DSP之间均采用Rapid IO接口互联,FPGA还负责DSP的电源启动配置。FPGA和 DSP均挂载 2GB的 DDR3、256KB的EEPROM和2GB flash存储器。

图1 雷达信号处理板框图

为了保证系统稳定性,DSP和FPGA电源相互独立,ADC采用线性电源供电。

2 成像算法设计

要实现合成孔径雷达成像精确的空变二维匹配滤波是比较复杂的。可以在成像质量要求、成像模型上进行一些近似简化,实现快速、高效成像。

雷达在飞行过程中,对回波的采样和量化,是按照先距离方向,后方位方向的顺序进行的,信号具有二维结构。而且本文的雷达平台飞行速度快,在4 km/s~2 km/s变化,方位向过采样率在0.9~1.4之间,由于方位分辨率远大于距离分辨率,可以通过方位向预滤波降采样[2]降低方位向多普勒带宽满足方位向1.2倍过采样率要求,同时保证方位不模糊的同时降低方位向数据率,在满足成像要求的情况下使距离和方位分辨率匹配,同时减少降采样后的混叠干扰,保住回波的相位信息,这样比较有利于信号的实时处理。

对于正侧视成像来说,距离-多普勒算法将首先解除距离、方位两维之间的耦合,进行距离走动和距离弯曲校正,解耦后二维处理等价于两个一维处理[3],这样在硬件处理时,比较容易引入流水处理和并行处理,也不会在硬件中进行大规模的转置操作,比较有利于实时成像处理。

并且考虑到实际平台运动状态受外界因素影响存在不稳定性,可能存在非匀速、小范围侧摆。运动状态变化引起的多普勒中心和多普勒调频率变化[3],可以通过对原始数据进行估计或者惯导数据对距离向数据进行线性相位补偿,对方位向数据进行运动补偿,进一步解除距离向和方位向的耦合。在通过距离、方位两个一维的匹配滤波,得到所需场景图像。

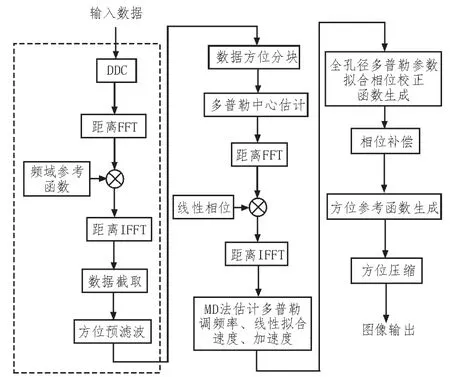

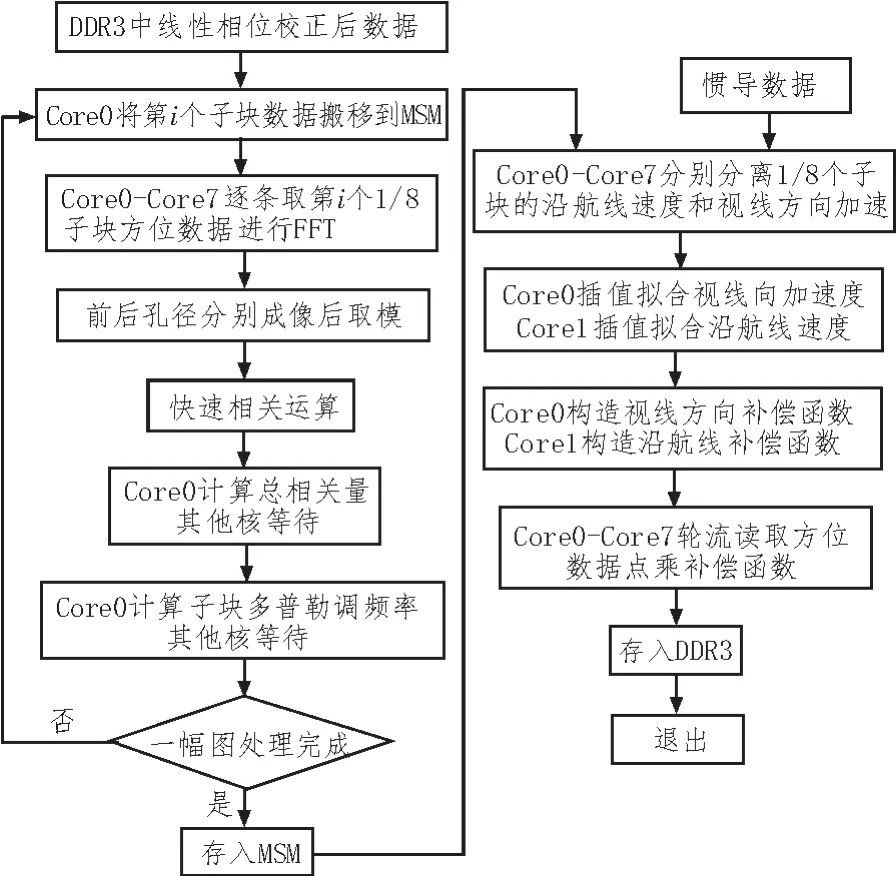

本文采用的硬件成像算法如图2所示。考虑到硬件处理数据流,FPGA并行完成数字下变频、距离压缩、方位预滤波降采样,如图2中虚线所示。DSP完成多普勒中心估计、线性相位补偿、运动补偿和方位压缩,同时FPGA还负责对外数据通信。

图2 成像算法流程图

3 主要硬件算法实现

实时处理算法可以分解为数字下变频(DDC)模块、距离脉冲压缩模块、方位预滤波模块、线性相位补偿模块、运动补偿模块、方位脉冲压缩模块和通信模块。本文主要介绍DSP处理模块。

3.1 Rapid IO通信程序设计

信号处理板中,FPGA可以通过IP核与DSP实现Rapid IO 2.1[5]协议通信。两路DSP间采用2倍速(2.5 Gbps)连接,FPGA与两路DSP间之间均采用1倍速(1.25 Gbps)连接。

由于DSP的内存映射关系及相应数据段已经在DSP的CMD配置文件中定义,故可以采用Direct I/O通信方式,将FPGA设置为主控设备端,DSP设置为从属设备端,FPGA可以将DSP当做随机存储器,使用NREAD和NWRITE两种方法直接对DSP相应的地址空间进行读写[6-7]。同时设置FPGA和两路DSP的Device ID,以便互相识别。表1为FPGA读写DSP外挂的2GB DDR3中100MB数据的性能。

表1 FPGA读写DSP DDR3中数据的性能

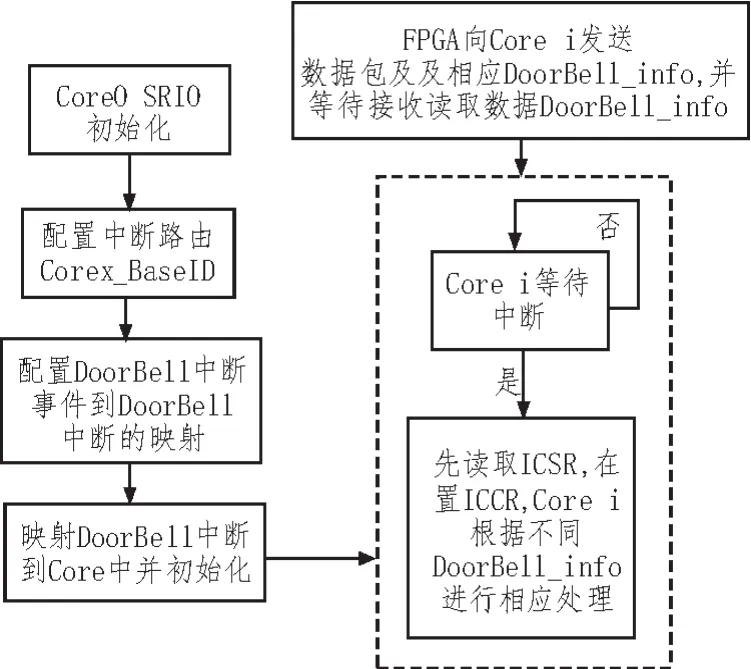

实时处理中,DSP初始化SRIO后,FPGA就可以通过NWRITE发送数据,一般FPGA还需要发送一个DoorBell信息通知DSP,FPGA要发送数据。对于FPGA通过NREAD读取DSP存储器数据,FPGA发送这个命令后,DSP会自动的将请求的数据发送出去,但也需要DoorBell信息通知FPGA数据发送出去。所以FPGA每次对DSP数据的读写可以通过DoorBell中断方式进行,通过设置中断事件16-19,进行相应的处理,通过设置不同的DoorBell信息,通知对方一块数据或一帧图像数据开始发送或者发送完成,保证系统数据交换的可靠性。

DoorBell中断配置及中断服务程序流程如图3所示。

图3 中断配置及中断服务程序流程图

3.2 核间通信及cache一致性维护

雷达成像数据量通常都较大,并行处理时,每个核无法同时将DDR3或MSM(共享存储空间)中的数据利用EMDA3搬移到各自L2中,必须通过一定措施实现实现核间通信保证EDMA3任务分配。

C66X内核对访问相同存储空间提供了硬件信号量、共享存储空间和核间中断三种方法进行核间通信[8-9]。文中采用相对比较容易理解的共享存储空间方法实现核间通信。其基本思想如图4所示。设置全局标志位Flag,确保每个核对共享存储空间访问时,共享资源都是独占的,保证数据的有效性,避免访问冲突。

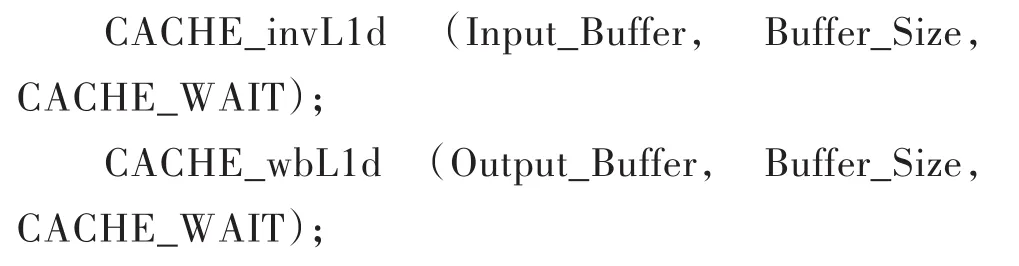

对于小数据量的计算使用EDMA3直接从DDR3将数据搬移到各核L2计算,不需要维护L2与L1D的cache一致性。对于块数据的计算使用EDMA3从DDR3将数据搬移到MSM计算,通过共享存储空间方式分配多核任务,在每次数据搬入后,使L1D cache值无效,每次数据搬出前,将L1D cache中最新数据写入MSM中,可以采用TI提供的两个函数[10]完成:

3.3 线性相位补偿程序设计

图4 共享存储空间方法实现核间通信

线性相位校正是依据非聚焦SAR临界合成孔径长度,将一幅图像数据按方位向分成若干块,估计出每块的多普勒中心,构造相应的线性相位校正函数,在按方位向在频域校正原始数据,而后变换到时域完成线性相位补偿。

为了保证实时性,每个核均预分配空间L2_swap作为数据交换区,在MSM中分配块空间MSM_Swap。每次运算由Core0将一块数据搬移到MSM_Swap,每个核依次取两条距离向数据至L2_swap进行FFT、共轭点乘并累加求平均取相角后存入MSM,每个核将FFT后的数据轮流写入DDR3,待所有分块数据处理完成。Core0将相角转化为多普勒中心,每个核根据结果构造线性相位校正函数存储至L2,依次进行线性相位校正,并将数据转置存储到DDR3中,供运动补偿使用。线性相位补偿流程如图5所示。

3.4 运动补偿程序设计

图5 线性相位补偿流程图

由于平台运动的不稳定性,会使雷达回波距离向和方位向的耦合,必须进行运动补偿。运动补偿关键是估计平台在成像时间内的运动参数。本文利用惯导数据得到每一点的沿航向速度及其引起的多普勒调频率,并通过回波估计多普勒调频率,得到视线方向加速度,构造相应沿航向和视线方向补偿函数,在时域进行运动补偿。其流程如图6所示。

图6 运动补偿流程图

硬件实现时,按方位向取合成孔径相干积累时间十分之一的子块[1,3],Core0每次将DDR3中线性相位补偿后的数据取一个子块到MSM_Swap,按距离向平均分成8块,8个核分别处理一块。每个核沿子块方位分成前后两个孔径分别成像,进行相关运算。Core0将相关结果累加得到总相关量,求取偏移量,与初始值相加后估计出多普勒调频率。所有子块调频率计算完成,结合惯导数据拟合得到沿航向速度和视线方向加速度,Core0和Core1分别构造沿航向和视线方向补偿函数后,8个核按距离向进行运动补偿。这里采用Double型运算减小对误差的累加效应。

3.5 方位压缩程序设计

运动补偿后,可以认为相位误差已经基本消除[3],图像可以良好聚焦。本文采用频域方位压缩,利用估计的多普勒中心和多普勒调频率构造方位频域脉压匹配函数,方位脉冲压缩后变换到时域,得到图像数据,存入DDR3。为了节约计算资源,将128位-4096位的FFT旋转因子采用固化方式写入flash,每次初始化后读入MSM,供后续计算使用。

3.6 系统连续出图设计

雷达平台飞行速度从4 km/s~2 km/s变化时,多普勒带宽的过采样率逐渐增大,对于观测2.6 km的场景的飞行时间增长,方位采样点数也在增大。FPGA方位预滤波时,采用不同降采样率的滤波器保证方位分辨率满足指标。系统连续出图需保证相邻两幅图像重叠半个孔径的数据,即两路DSP乒乓处理的数据方位上重叠半个孔径,由FPGA将重叠数据缓存,轮流发给两路DSP,并且FPGA读取DSP处理完成数据送给上位机进行图像拼接。连续出图方案如图7所示。

图7 系统连续出图方案

4 结果及分析

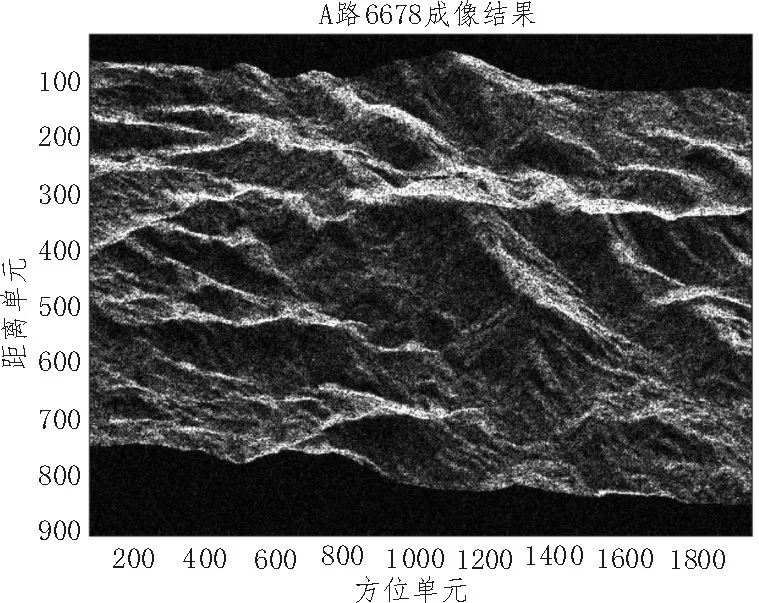

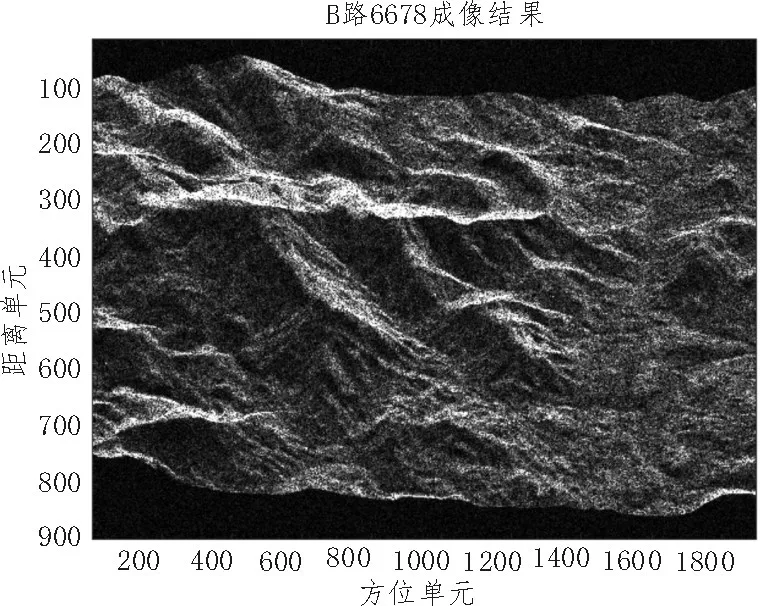

将2.6 km×4 km大小场景雷达回波(雷达重复频率20 000 Hz,距离向采样点数1200)仿真数据及惯导参数导入到FPGA外置DDR3存储,由FPGA按实时采样流水依次读取数据与DSP联合完成成像算法处理。图8、图9为两路DSP乒乓处理后的雷达成像结果。

由于FPGA的并行流水处理特点,其算法处理的时间消耗极少,主要时间消耗在DSP上,表2为DSP处理算法消耗的时间。

以平台最快飞行速度4 km/s计算,平台飞行2.6 km的一幅图像场景需要650 ms,由于实时连续出图需要,每路DSP处理时间间隔约1 s,而算法总处理时间约为500 ms,满足实时处理要求。硬件与Matlab处理的结果对比,幅度无误差点数大于91.5%,相位无误差点数大于97.2%,相位偏差均在在0.5°以内,处理精度较高。验证了硬件平台和算法的正确性。

图8 A路DSP处理的雷达图像结果

图9 B路DSP处理的雷达图像结果

表2 DSP算法模块时间消耗情况

5 结束语

文中利用R-D算法的基本思想,结合线性相位校正、运动补偿以及多核DSP的算法特点,优化处理流程、多核任务分配和并行处理效率,在TMS320C6678平台上实现了高速运动平台高精度实时成像处理实现了实时成像。而且本文所述系统可以应用在制导、救灾地形勘探、军事侦察等场景,也可应用于干涉合成孔径雷达实时处理,具有较高的应用前景。