一种改进型CIC抽取滤波器的实现方法

2018-08-08谢海霞孙志雄

谢海霞,孙志雄

(海南热带海洋学院电子通信工程学院,海南三亚572022)

数字上、下变频器所涉及的抽取和内插存在着混叠、镜频等问题,抽取、内插后如何分离出需要的信号,关键在于抽取前和内插后的抗混叠高效数字滤波器设计。由于CIC滤波器结构只有乘法运算,便于提高实时性和简化硬件,故常用它作为抗混叠高效数字滤波器。经典CIC抽取器一般用来处理窄带信号,而处理宽带信号时,幅频响应很不理想,满足带外衰减指标时,通带衰减过大,难以满足抗混叠性能要求。因此,如何更好地增大滤波器的零点抑制同时又不影响其通带性能一直是CIC滤波器研究的热点[1-5]。

1 CIC抽取器的设计

CIC抽取器结构简单,主要由积分部分、抽取部分和梳状部分组成[6]。其结构如图1所示。

图1 单级CIC抽取滤波器框图

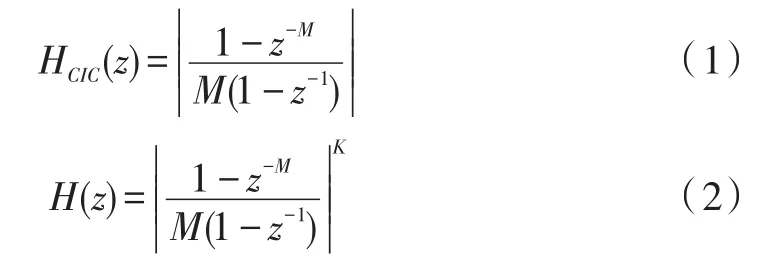

式(1)为单级CIC抽取器传输函数。由于单级CIC的过渡带的衰减性能不是很好,所以实际应用中,通常是由多个单级CIC滤波器级联方法来加大过渡带和阻带的衰减。多级传输函数为式(2):

其中,M为大于1的整数,称为抽取因子,决定了CIC的通带大小;K为级联数,对旁瓣抑制比起到加大作用。CIC滤波器多级级联的方法虽然能使阻带衰减加大,但却是牺牲了通带特性。在滤波器的设计中这两点都很重要,不能只考虑其中一点,而忽略另外一点。文献[7]提出的基于分级抽取的滤波器的改进方法就是针对多级滤波器级联的情况,将整数倍抽取分成两部分实现,即M=M1M2。则式子(2)可以变形为:

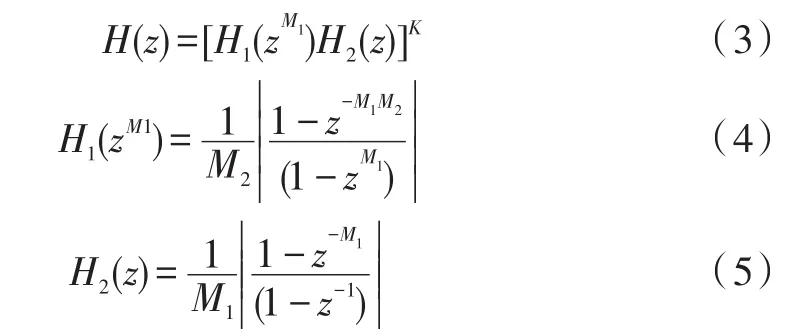

对滤波器的零极点分析如图2所示。

观察零极点图2可见,H(z)的零点与和H2(z)的零点在位置上相同,保证了CIC整体频率特性的相似性。因此,用H1(zM1)来控制滤波器的通带响应,用H2(z)来调整阻带衰减。因此,可以重新定义滤波器的传递函数:

以下利用上述特征对H(z)进行结构改造衰减。

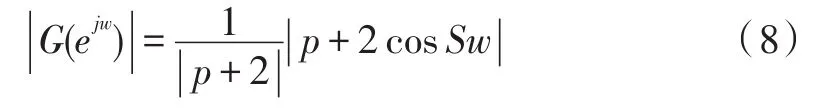

1.1 基于二阶多项式函数补偿的抽取器

通常使用CIC抽取器时,为了调整通带内的平坦度,会在后面加一级补偿滤波器。文献[8]对[H1(zM1)]部分进行频响特性的改进,采用易实现的内插二阶多项式(ISOP)对[H1(zM1)]改进其频率特性。其中二阶多项式(ISOP)的系统函数为G(z),定义为:

式中:S为ISOP的内插因子且为正整数;p为实数,它调整内插曲线的幅度。S和p为G(z)的可调参数。ISOP抽取器的幅频特性为:

图2 零极点分析(M=16,M1=2,M2=8)

N值必须保证ISOP子系统每N个极小值的位置都要与CIC滤波器的零值点相吻合。值得注意的是N的选取p密不可分,因为(N,p)共同决定通带波动δ,把ISOP的各个参数值作特殊设置,令M=M2且N=M1,在频段0≤ω≤2πfp尽量减小通带内的波动δ,并在满足:|H(ejω)G(ejω)-1|<δ。这样能够确定最小的通带波动δ的p值就被选定。改进后的抽取器加大了通带内的平坦度,且对阻带衰减没有影响,且能够很好地处理窄带信号,但处理信号带宽大且抽取倍数M很小的情况时,滤波器的通带衰减仍然不够理想,该现象将在下面性能比较中进行分析。

1.2 基于锐化技术补偿的抽取器

锐化技术既能改善CIC滤波器的通带特性,又能改善其阻带特性。文献[9]提出的锐化技术对CIC抽取器进行改进所得的滤波器通常称SCIC(Sharpened CIC)滤波器,其传递函数为:

式子(11)中,HCIC(z)为原型单级CIC抽取器的系统函数。通过与传统的CIC抽取器性能比较,SCIC改善了CIC的通阻带特性,但其在硬件实现中,积分器往往工作在很高的输入采样率下,运算量大。文献[6]用锐化H1(zM1)来代替锐化整个滤波器H(z)。从而式子(6)改进为:

与传统CIC抽取器相比,锐化后抽取器的通带性能有了改善,其旁瓣抑制比有较大提高,这现象也将在性能比较分析中给出具体说明。虽然锐化滤波器的特性优良,但这是以增加滤波器的复杂度换取的,显然这种以增加复杂度换取性能的改进在一些对实时性要求不是很高的场合是很适用的。

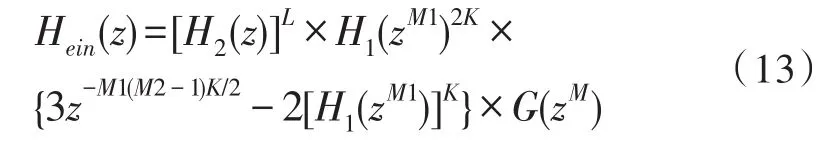

1.3 改进的CIC抽取器

本文基于上面提到的两种改进方法,综合利用锐化滤波器和二阶多项式补偿滤波器对CIC抽取滤波器的通带和阻带衰减同时进行改进。利用文献[7]中提到的将整个抽取分两级实现的结构,即M=M1M2,用H2(z)来调整阻带衰减,锐化H1(zM1)即控制滤波器的通带响应,在后面加二项多项式补偿滤波器G(zM),以调整通带内的平坦度,则改进型的整个滤波器的Z变换为:

2 幅频特性比较分析

根据CIC抽取滤波器幅频特性,通带截止频率wp处的衰减幅度为通带内幅度衰减最大值;阻带截止频率wd处的幅度衰减是阻带内衰减的幅度最小值。衡量滤波器的抗混叠性能优劣主要以这两个点的衰减情况为参考[10]。设信号带宽fp,固定采样率为fs,wp、wd、δp、δd分别为:

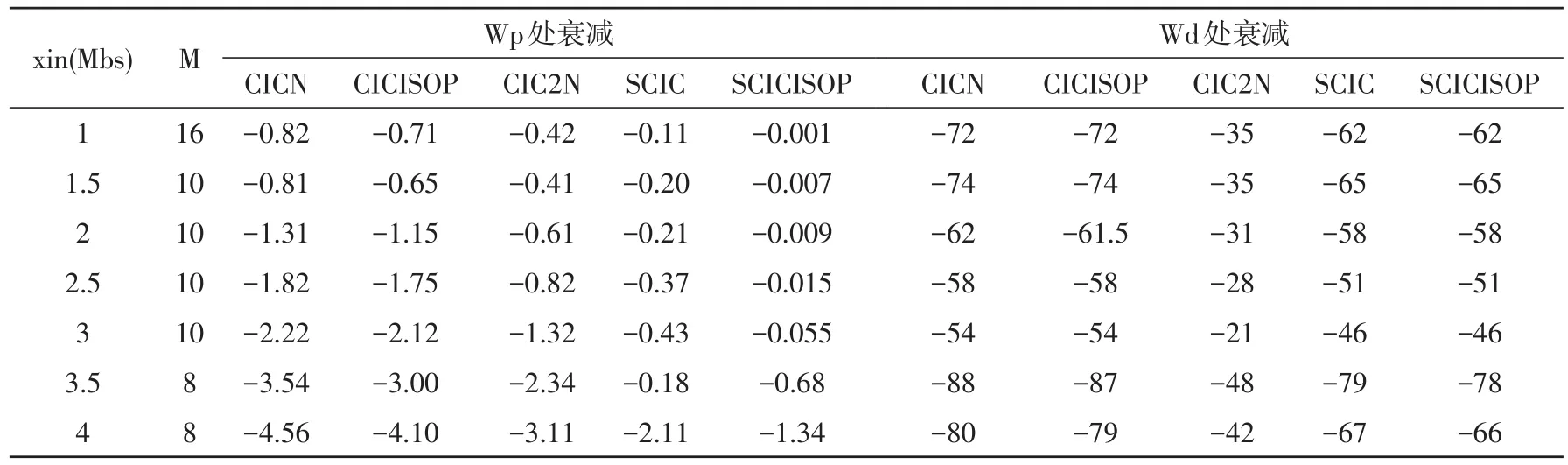

以处理信号带宽大,抽取倍数小的这类信号举例。采样率fs=140 MHz,输入信号的数据率由xin表示,且 xin=[1 Mb/s,1.5 Mb/s,2 Mb/s,2.5 Mb/s,3 Mb/s,4 Mb/s]。传统多级CIC抽取滤波器的级数由满足阻带衰减牺牲通带衰减来确定。不同的滤波器结构,参数计算也不相同。结构中的K和L参数的设计。1)当 xin数据率小于或者等于 3 Mb/s时,K=2,L=4;2)当xin数据率大于3 Mb/s时,K=4,L=8。令传统CIC的级数为N,根据因式分解算法[9]来配置参数如下:

N=[4 4 4 4 6 6];K=[2 2 2 2 4 4];L=[4 4 4 4 8 8];M1=[2 2 2 2 2 2];M2=[8 5 5 5 4 4]。

此时,对传统CIC(CICN)抽取器、传统CIC带有补的(CICISOP)、分级CIC的(CIC2N)、分级锐化处理的(SCIC)、和改进型CIC抽取器(SCICISOP)的频响作比较如图3所示。

图3 5种滤波器的频响对比图

从比较的情况可知,利用多项式补偿函数对原型CIC进行改进后抽取器(CICISOP),对通带处的衰减幅度稍有改善,但在处理宽带信号时还不够;分级抽取CIC滤波器(CIC2N)通带频响平坦,但是阻带衰减不满足要求,采用锐化处理后(SCIC)阻带衰减显著,通带也较平坦,而本文提出的改进型CIC抽取器通带内更加平坦,并且阻带衰减明显并满足要求。5种滤波器在处理输入信号xin时wp、wd处的衰减情况比较,如表1所示。

表1 5种滤波器在通阻带处的衰减情况

3 改进型CIC抽取器的FPGA实现

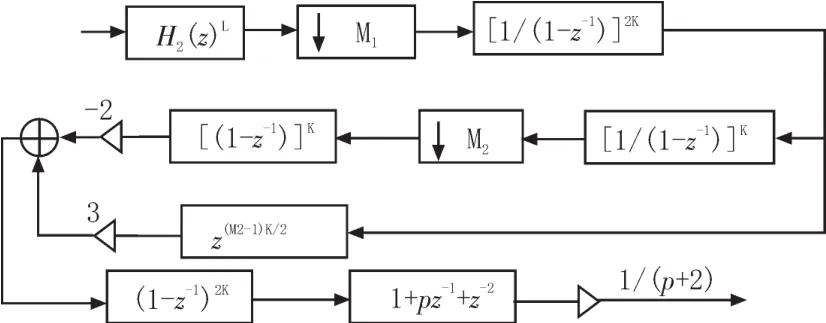

简单地将积分器和梳状器级联是传统CIC的FPGA实现形式。本文提出的改进型CIC滤波器则是先搭建H2(z)L和H1(zM1)K之后再级联G(zM),图4给出了改进后的CIC抽取器的框图,这种结构很直观的看出滤波器的结构。

图4 改进型CIC抽取器

为了使整个抽取器的计算量降到最低,对图4中的电路优化,本文利用文献[12]的方法对H2(z)L进行多相分解,主要缓解下采样率前处理高速率信号的计算压力,前级抽取因子M1的作用下使后面处理的信号采样率下降M1倍,这对降低功耗相当重要;而锐化的滤波器的各个组成部分分解成两部分:M2倍下采样前和M2倍下采样后;二阶多项补偿滤波器放在最后,这样整个抽取器的各个组成部分都在最低的采样率下工作了,应用这种思想改进抽取器的结构细化分解为:

图5 改进型CIC抽取器实现结构

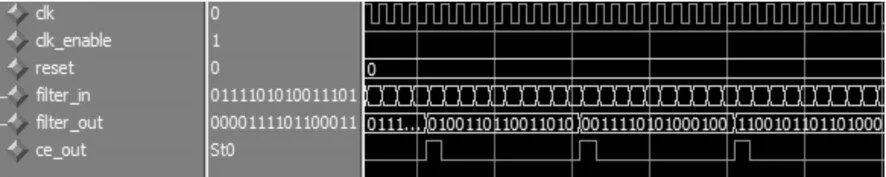

改进型CIC滤波器FPGA实现采用Verilog语言描述,采用Altera公司CycloneII系列开发板,在QuartusII 12.0环境下进行。其FPGA实现的顶层结构如图6所示(其中clk为输入时钟,clk_enable为使能信号,reset为复位信号,filter_in为输入数据,filter_out为输出数据,ce_out为输出数据变化指示信号)。

图6 顶层结构图

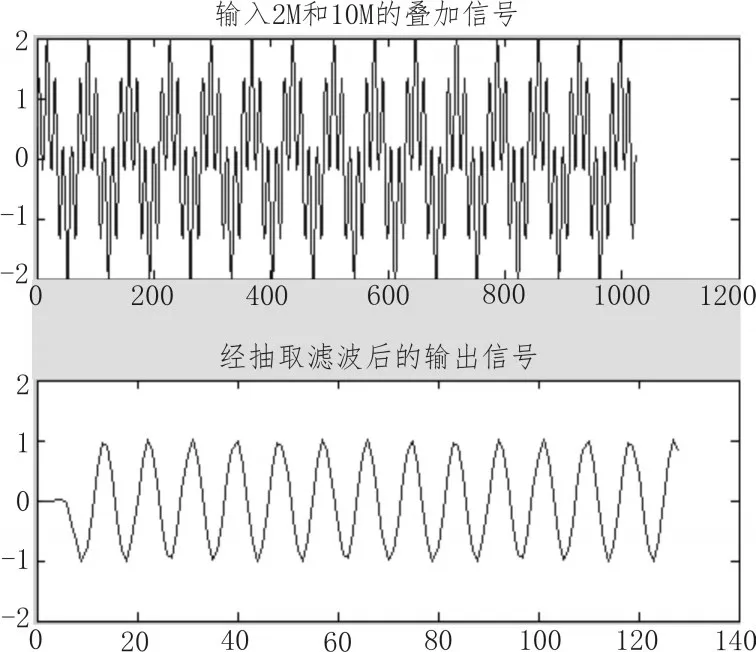

此时,选取抽样频率为140 MHz,抽取倍数M=10,M1=2,M2=5,K=2,L=4,p=-28,利用 MATLAB仿真验证,从图7中可以看到,输入信号为2 MHz和10 MHz正弦信号的叠加,在输入的两个信号中,位于阻带内的频率为10 MHz被滤掉,保留了位于通带内的频率为2 MHz信号;而QUATUSII自带的仿真工具仿真的结果如图8所示,从ce_out的10个时钟变化一次,可以看出对输入信号进行16倍的抽取。仿真结果正确,最后下载到芯片中,根据FPGA综合报告,在滤波性能不变下,采用优化电路结构时,使用的逻辑资源减少了15%,说明对结构的改进与优化大大节省了硬件资源。

4 结束语

本文提出的改进型抽取滤波器很好地补偿了CIC滤波器通带的偏差,并增加了通带的宽度,其更适用于对通带要求较宽的软件无线电系统。在高速率状态下进行积分,在低速率状态下进行梳状滤波,

图7 MATLAB仿真

图8 时序仿真

多相优化结构,降低了中间存储,资源占用最少,大大降低功耗[12-16]。