基于FPGA的星载NAND FLASH控制器的设计

2018-08-08乔亚飞李华旺

乔亚飞 ,李华旺 ,常 亮 ,李 杰

(1.中国科学院上海微系统与信息技术研究所上海200050;2.上海微小卫星工程中心上海201203;3.中国科学院大学北京100049)

随着空间科学技术的进步,在轨卫星运行期间产生海量的数据[1],对数据存储设备的容量要求也越来越高。由于NAND FLASH的容量大、读写速度快、易擦除、低功耗等特点[2],越来越多的用作航空航天领域的存储器件。虽然市面上有很多专用的FLASH控制器的芯片,但是这类芯片往往功能较多,导致功耗高,兼容性较差[3]。考虑到星上CPU的资源比较宝贵,底层的控制器采用FPGA实现,FPGA作为可编程逻辑门阵列,具有高度的集成性,同时又有可编程器件的灵活性。本文采用VHDL语言,设计了通用型的NAND FLASH控制器,并在Microsemi公司Smartfution2 090 FPGA单板上得到验证。

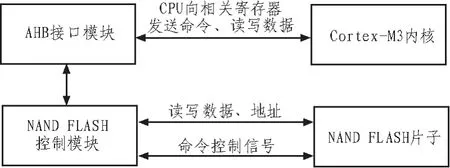

1 整体架构设计

本次设计FPGA选用Microsemi公司的Smartfu⁃tion2 090,该芯片包含FPGA和ARM的Cortex-M3内核[4]。Smartfution2系列FPGA基于FLASH架构,而一般的FPGA基于SRAM架构[5]。与SRAM架构FPGA相比,Smartfution2系列FPGA具备高可靠性和单事件翻转免疫能力[6],更能适应太空复杂环境,广泛应用于航空航天领域。

总体架构如图1所示,单板上的Cortex-M3内核通过AHB总线向底层的FPGA的AHB接口模块发送相关FLASH控制命令和将要写入FLASH的数据;FLASH控制器模块从AHB接口模块的相关寄存器读取FLASH控制命令,数据等,解析相关命令,执行对NAND FLASH的操作。

图1 总体架构图

2 NAND FLASH控制模块

本次NAND FLASH的片子选用Micron公司的MT29F32G08AFABA这一型号。这一FLASH容量较大,每片可以达到32G,组织也更加复杂。1片FLASH有2个(Logical Unit)LUN,每一个LUN包含2个plane,每个plane包含2 048个block,每个block包含128page,每个page为(4K+224bytes)。

NAND FLASH的数据、地址和指令采用复用I/O接口[7]。NAND FLASH 器件通过 CE(片选)、CLE(命令锁存)、WE(写使能)、RE(读使能)、ALE(地址锁存)使能信号的电平,来判断写入I/O总线的数据是地址还是数据、指令[8]。如果是通过I/O写入命令,需要将CLE信号拉高,写完之后将CLE拉低;同理,如果写入的是多拍的地址,需要将ALE信号一直拉高,写完之后拉低。

NAND FLASH控制模块是本次设计的核心。该模块主要功能有:

1)支持FLASH复位,读数据,写数据,块擦除,读状态,读ID操作。

2)支持超时检测功能。

3)支持多片FLASH阵列。

4)NAND FLASH控制时序参数可设置。

NAND FLASH控制模块主要由状态机实现,状态机的初始状态为ST_IDLE,当检测到脉冲信号USER_CMD_EXE时,启动状态机,状态机跳转等待FLASH忙状态;随后根据命令信号USER_CMD跳转到相应的子状态机去执行,执行完一种功能时,跳回ST_IDLE初始状态。本设计主要有6种子状态机:复位操作子状态机,对NAND FLASH进行复位;读ID状态机,读出NAND FLASH的生产厂商、特性等[9];块擦除状态机,写操作之前必须对NAND FLASH进行擦除[10];读操作状态机,读数据;编程操作状态机,向NAND FLASH写入数据;读状态操作状态机,判断块擦除或者编程操作是否完成[11]。

2.1 NAND FLASH读操作设计

读操作是NAND FLASH的一个基本操作,以页为基本单位读出数据[12]。对于本次FLASH的读操作设计,根据需要,将一页分为4 K大小的data区,和224字节的Spare区,data区主要存放有效数据,例如卫星的载荷数据、电源数据等;spare区存放片子的信息,例如坏块、ID等。

根据NAND FLASH的数据手册时序图设计读操作的状态机,读操作分为9个状态。检测到US⁃ER_CMD_EXE脉冲信号,状态机跳转至ST_WA IT_BUSY,随后,解析命令信号跳转至读操作;向NAND FLASH发送00h指令,则使NAND FLASH进入READ模式,随后写入3个周期的PAGE地址和2个周期的列地址;写入30h指令则将启动数据读操作,等待NAND FLASH反馈的R/B信号由‘0’变化为‘1’时[13],状态机进入ST_READ_WAIT_TO_READ状态,在R/B信号为低时,利用rbn_time_cnt计数器进行超时检测;等待tRR(大约为3个时钟周期)时间即可开始数据读序列,依次读完data区数据和spare区数据,最终跳回ST_IDLE状态。读操作的状态机如图2所示。

图2 读操作状态机转移图

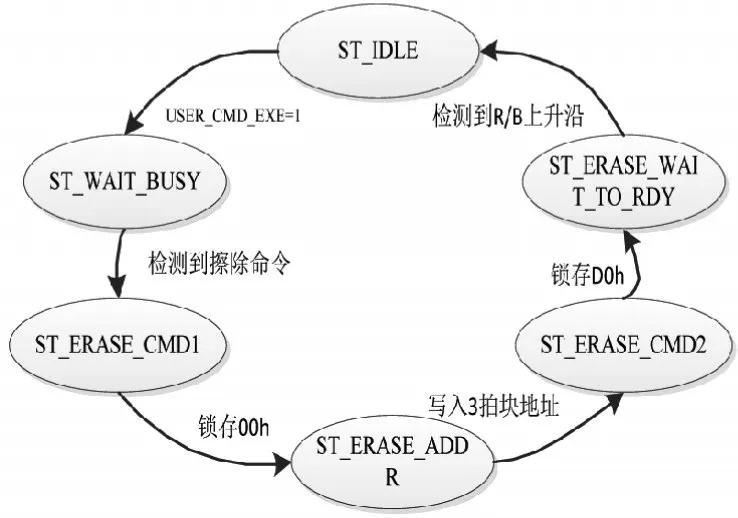

2.2 块擦除设计

对于NAND FLASH,在写入数据之前必须进行块擦除,块擦除是基于块的[14]。与读操作和编程操作相比,块擦除操作相对简单。首先,向NAND FLASH发送60 h指令,FLASH进入块擦除模式,写入3拍的块地址,发送D0h启动块擦除操作;等待R/B信号由‘0’变为‘1’,块擦除结束,状态机跳转至ST_IDLE。图3为块擦除状态机跳转图。

图3 块擦除状态机跳转图

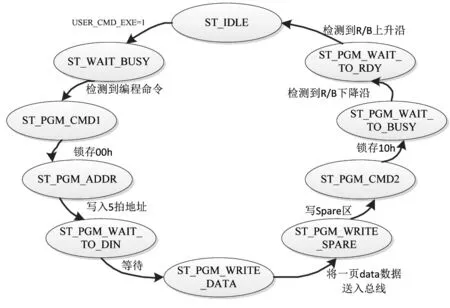

2.3 NAND FLASH编程操作设计

基于NAND Flash的结构,大数据的编程一般采用顺序写入的方法[15],从当前页的0地址顺序写完整页。根据NAND FLASH的数据手册时序图设计编程操作的状态机,编程操作分为10个状态。检测到USER_CMD_EXE脉冲信号,状态机跳转至ST_WAIT_BUSY,随后,解析编程命令信号跳转至编程操作;控制器模块向NAND FLASH发送命令80 h,片子进入编程模式,和读操作一样,写入3个周期的PAGE地址和2个周期的列地址;等待tADL(计数器计数3个CLK)时间,控制器模块将1 PAGE数据顺序送至I/O总线上,下一周期发送命令10 h至NAND FLASH;NAND FLASH检测到10 h之后,开始进行编程操作;NAND FLASH反馈的R/B信号由‘0’变为‘1’时(同读操作,当R/B信号为低时,进行超时检测),说明编程操作完成,状态机跳转至ST_IDLE状态;编程操作的状态机转移图如图4所示。

图4 编程操作状态机跳转图

3 AHB总线接口模块设计

因为星载计算机是CPU+FPGA架构,所以本次设计需要将底层的FPGA挂接到AHB总线上,用来接收CPU(Cortex-M3内核)发送过来的指令和数据。AHB总线是ARM公司提出的一种开放性片上总线标准[16],采用AHB-Lite协议,AHB-Lite是AHB协议的子集,只支持一个总线主设备,不需要总线仲裁器,不支持Retry及Splite响应。本次设计开发环境选用美高森美公司的Libero SOC和Softconsole IDE,将包含Cortex-M3的MSS(微控制器子系统)做Master,整个的FPGA代码顶层模块做Slave,调用Libero IP库中的AHB-Lite Core进行Master和Slave的互连。设计接口模块用于FPGA和AHB-Lite Core进行数据的交换,在该模块中,主要设置7组寄存器用于寄存数据:0x00寄存将要读或者写FLASH片子地址;0x04寄存操作FLASH命令;0x08寄存片选信号;0x0C寄存USER_CMD_EXE信号;0x20寄存CPU发送过来的将要写入FLASH的数据;0x24寄存从FLASH读出的将要送入CPU的数据;0x28寄存FLASH片子是否在写状态;0x2C寄存FLASH片子是否在读状态。

4 仿真验证

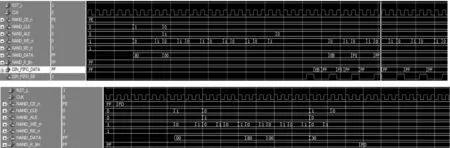

控制器的仿真平台选用ModelSim 10.4。仿真时采用Micron公司编写的NAND FLASH仿真模型,这一仿真模型参数可配,可以模拟NAND FLASH的如各种接口,操作。仿真时对NAND FLASH仿真模型分别进行复位、擦除块、写入、读出1 page数据,进行比对,观察控制器功能是否正常。经仿真测试,该控制器的预期功能正常。图5为控制器编程、读页操作仿真图(上为编程操作,下为读操作)。

5 上板验证

上板测试时,采用专用的复位模块,时钟频率采用50MHz。Cortex-M3内核向底层FPGA发送数据、指令,对NAND FLASH进行复位、擦除、写、读等操作,图6为上板测试的工程顶层模块。其中FLASH_AHB_TOP_MSS为上层CPU模块,编写C代码发送相关操作命令、读取相关数据。FLASH_AHB_ONBOARD为底层控制器的FPGA部分,实现对NAND FLASH的具体操作。底层FPGA和上层Cortex-M3通过CoreAHBLite桥接。

图5 控制器编程、读页操作仿真图

图6 工程顶层模块

在上板之前先进行可靠性测试,例如反复插拔单板,上电下电,复位等。可靠性测试工作完成之后,进行功能测试,写1 page数据最长耗时为760μs,读1 page数据最长耗时为280μs,擦除整个Block为3.5 ms;满足星上毫秒级速率存储要求。

6 结论

本文的创新点在于设计了CPU+FPGA架构的星上NAND FLASH控制器,与专用的星上NAND FLASH控制器芯片相比,基于FPGA的设计接口更多,更加灵活,参数可调可配,提高了控制器的兼容性,功耗降低。通过仿真和上板调试,NAND FLASH的读写等功能都能实现。同时,控制器底层硬件采用FPGA,节约了星载计算机的资源,满足在轨卫星的数据高效存储的要求。