基于OFDM的VDES地面子系统设计*

2018-07-26

(南华大学 电气工程学院,湖南 衡阳421001)

1 引 言

随着世界经济全球化的推进,海上航运事业的发展得到长足进步,同时也带来了海上通信需求的爆炸式增长。传统船舶自动识别系统(Automatic Identification System,AIS)作为应用于船舶定位、船舶航行信息共享、船舶航行通告发布等通信需求的海上通信系统,是当前承载海上通信任务的中坚力量[1]。但因频带资源有限,导致AIS无法充分满足海上通信应用模式多样化的需求,促使国际航标协会(International Association of Marine Aids to Navigation and Lighthouse Authorities,IALA)和国际电信联盟(International Telecommunications Union,ITU)自2013年开始共同努力推动新一代海上数据交换系统VDES的发展[2]。VDES现集成了甚高频(Very High Frequency,VHF)海上移动频段(156.025~162.025 MHz)中VHF数据交换(VHF Exchange System,VDE)、应用特定消息(Application-Specific Messages,ASM)和AIS功能,是一套囊括了船-船、船-岸基、船-卫星、岸基-卫星的空天地一体化的通信系统[2-3]。目前,全球范围内许多国家均对VDES系统展开了积极的科学研究。在VDES未来发展规划方面,自2014年开始法国提出了涵盖规则层和实施层跨度10年的发展规划。特别是关于地面系统建设方面,国外已有许多船台制造商积极投入VDES系统的使用开发中[2]。虽然关于VDES的相关研究及其应用尚处于初期发展阶段,但VDES系统因其具备的丰富应用价值,吸引了国内外大量学者对其进行深入的科学研究。

本文结合VDES地面子系统物理层的技术需求,融合正交频分复用(Orthogonal Frequency Division Multiplexing,OFDM)技术,构造了VDES地面子系统物理层的通信链路系统,完成了系统的硬件设计,并于大连海域完成系统的海上实测。本文系统的设计能够在一定程度上满足较大时延信道环境下的抗多径需求,对VDES地面子系统的实际应用具有一定的价值。

2 VDES系统地面子系统简介

本文在综合调研VDES系统之后,着重针对VDES地面子系统作相关研究。VDES地面子系统即针对船与船、船与岸基之间的高速数据交换系统,它支持实时通信和信息确认回传,信息接收可靠性高,通信半径可达20~50 n mile,拥有6个国际通用无线电通道,同时支持额外的区域性通道等[3]。VDES地面子系统主要的应用场景为海上船与船、船与岸基之间的通信,因而无线信号的传输主要为视距(Line-of-Sight,LOS)传输,同时传播过程中海上遮挡信号传播的障碍物较少(海面可近似等效为镜面),易带来海上VHF信号的反射增加,多径干扰问题较为突出[4]。因此,系统的抗多径性能已然成为VDES地面子系统通信性能优良评判的一个重要指标。

ITU在2015年发布的建议书ITU-RM.2092中在针对抗多径干扰的问题上仅做了常规性的设置,但针对较大时延信道环境下的抗多径干扰问题没有给出特殊的建议[4-5]。遍历当今几种应用成熟的通信标准,OFDM技术均被采用作为物理层通信架构的核心技术,其在抗多径干扰方面具备天然的优势能有效地帮助提升系统的通信质量[6]。

3 VDES地面子系统OFDM核心算法设计

系统整体的通信链路模块和技术指标需求严格遵循建议书ITU-RM.2092和ITU-RM.1842中相关参考标准,同时本文基于OFDM技术对系统物理层相关核心技术模块做相应设计[7]。

3.1 时隙结构设计

系统的带宽和子载波个数的设计参照ITU-RM.1842建议书中示例描述设定为100 kHz带宽内包含32个功率相等的子载波。同时,本文设定每个子载波间隔为2.7 kHz,预留13.6 kHz分布载波两端作为系统保护带宽。

系统的帧结构设计仍遵循ITU_RM.2092中数据帧结构的定义,一帧时长为1 min,共计2 250个时隙。但本文对系统的时隙结构在综合考虑系统需求后做了重新设计,如图1所示。1个时隙包含了69个OFDM符号,每一个OFDM符号的持续时间为T=160 ms/6/69=386.47 μs。对于整个系统,基带采样间隔Ts=1/(2 700×2 048) s。1时隙=160 ms/6/Ts=147456Ts。

图1 系统的时隙结构Fig.1 Slot structure of system

3.2 数据组包设计

系统的数据帧结构和时隙结构确定之后,系统的资源元素个数也被确定了,但不同的调制编码方式(Modulation and Coding Scheme,MCS)对应的初始数据长度是不同的,因而在数据组包过程中除缓升、同步、信号信息、缓冲器外,系统需对数据信息的初始长度单独定义。初始数据长度的确定需要综合考虑MCS的选取和交织器的交织深度等因素。如表1所示,本文给出了系统支持的6种MCS对应的初始数据长度的参数取值。

表1 系统初始数据长度Tab.1 Length of system initial data

3.3 循环前缀设计

系统的子载波间隔为2.7 kHz,则一个OFDM符号本身时间长度为1/2.7 ms,1时隙内正好有160 ms/6/(1/2.7 ms)=72个OFDM符号。系统预留3个OFDM的时长用于设置CP,避免了载波间干扰(Inter-carrier Interference,ICI)和符号间干扰(Inter-symbol Interference,ISI)。为了确保有效的抗ISI性能,也为了保证每一个时隙内包含整数个含有CP的OFDM符号,设置CP长度为16.10 μs,与LTE系统OFDM的最大的扩展CP(16.67 μs)基本相当。这样的CP设置不仅可以避免时延带来的ISI,也能保证在FFT周期内OFDM符号的延时副本内包含的波形的周期个数为整数,载波间的正交性不被破坏,从而有效对抗系统在20~50 n mile的海上传输距离下的严重多径干扰。虽然加入CP占用了一定OFDM符号开销,带来了能量的损失,但消除了ICI和ISI,这样的代价是有价值的。

3.4 同步信号设计

同步信号的设计需满足能够用于系统中信号信息与数据信息的符号定时及频偏估计。本文系统中选取的同步信号是CAZAC(Const Amplitude Zero Auto-Correlation)序列,利用其优良的自相关和互相关特性,便于接收端的相干检测,从而完成系统的粗、细定时同步和整数、分数频偏估计与补偿[8-9]。

此外,同步算法将直接影响系统的同步性能,本文在综合评估算法计算量和同步性能之后采用了Wang算法[10]。本文中训练序列的排列架构为Ss=[A·S,A·S,-A·Q,-A·Q],其中A为ZC序列,S、Q为PN序列,A、S、Q的长度均为1/4个Symbol。特别是PN序列的引入可以进一步减小时域相关性并降低峰均功率比(Peak to Average Power Ratio,PAPR)。

3.5 导频信号设计

系统的导频主要用于完成信道估计和信道质量的测量[11],本文中用于系统仿真中的导频信号采用的是易生成、且有很好的自相关和互相关特性的m序列[12]。

本文所设计的导频起始时域位置为6(信号信息所在Symbol),终止时域位置为66(数据信息的最后一个Symbol),时域上间隔3个Symbol插入一个导频数据,频域上间隔5个子载波插入一个导频数据,同时为避免带来过多的开销,系统导频图样的设计采用了菱形图样设计,如图2所示。

图2 系统的导频图样设计Fig.2 Design of the system′s pilot pattern

4 基于OFDM技术的VDES地面子系统仿真验证

4.1 VDES地面子系统物理层链路仿真流程

本文中VDES地面子系统物理层是基于OFDM系统进行的建模[13]。图3给出了利用MATLAB搭建VDES地面子系统物理层链路的仿真流程。

根据VDES系统基础参数要求和OFDM的相关技术特性[14],首先根据数据帧结构和时隙结构生成特定长度的初始信息数据并插入循环冗余校验(Cyclic Redundancy Check,CRC)完成数据组包。数据经信道编码,完成交织、加扰、调制、插入导频之后,通过N点的IFFT变换,完成多载波调制,使信号可以在N个子载波上并行传输,并添加CP,最后经D/A转换处理之后进入时变信道传输。

图3 系统物理层链路仿真流程图Fig.3 Simulation flow chart of system physical layer link

接收端在接收信号完成自动增益控制(Automatic Gain Control,AGC)和A/D转换之后,根据同步信号与本地同步序列的强相关性完成定时同步和频偏估计,并完成信号的频偏补偿,经过去CP、FFT运算之后完成时隙数据的提取,根据导频图样提取导频,使用LS算法并结合一维线性内插完成各Symbol的信道估计及数据提取,之后通过与发射端相对应的一系列逆变换解调出原始的信息比特。

4.2 系统仿真参数设置

在完成链路系统的整体设计后,需进一步对各子模块进行相应的参数配置,从而完成系统的整体仿真。系统参数的配置是结合ITU-RM.2092建议书中给定参考指标和上文各模块资源配置计算所得,具体设置如表2所示。

电渗析除热稳定盐设备于2016年4月21日开始运行,2016年6月17日结束,共运行57天,除盐后,系统内胺液中HSS含量大幅下降,胺液浓度也有明显的上升。在脱除HSS期间,脱硫装置运行正常,因考虑到运行期间胺液的正常损耗,期间补充新鲜胺液2 t,系统总贮量基本保持不变。在除HSS设备运行期间,相关数据变化趋势如图3所示。

表2 系统仿真参数配置表Tab.2 System simulation parameter configuration

5 系统平台的相关仿真结果

5.1 吞吐量性能比对

系统的吞吐量是评估系统性能的基础性指标,为更直观地评估不同MCS下系统链路的性能,现针对不同MCS的吞吐量作仿真对比。

如图4所示,MCS_0~MCS_5的吞吐量性能依次提升,较建议书ITU_RM_2092中链路吞吐量,实验结果表明本文中建立的仿真平台提升了峰值数据传输速率,提升了系统的吞吐率,能够更好地满足海上船只的通信需求。同时仿真结果表明,MCS_0 - MCS_5对应不同的吞吐量,VDES系统需要考虑根据不同的信道质量指示(Channel Quality Indicator,CQI)选择具有适当链路余量的最高吞吐量格式。

图4 不同MCSs的吞吐量对比Fig.4 Throughput contrast for different MCSs

5.2 不同调制方式下BER对比

在完成对系统基础性能指标的验证,确保系统性能整体可靠的前提下,分别就不同调制模式下的系统性能作仿真对比。

图5给出了高斯信道下、1/2 Turbo码率时不同调制方式的误码率曲线,可以看出在高斯信道环境下,几种调制方式对应的误码率曲线均表征出系统具备较为优良的误码性能,其中误码率性能最好的是QPSK调制,其次是8PSK调制,最后是16QAM调制。

图5 码率为1/2,不同调制方式下性能对比Fig.5 Performance of different modulated modes in 1/2 code rate

5.3 不同Turbo码码率下BER对比

在完成上述系统性能指标的仿真验证后,为进一步评估信道编码对系统性能的影响,分别对两种Turbo码率下的链路系统作性能仿真对比。

图6中给出了高斯信道下、同种调制方式时(同种颜色对应同一调制方式)两种Turbo码率下的误码率曲线,可以看出系统误码性能良好,符合实际环境中随着Turbo码码率的增大,三种调制方式对应的误码率相应增加。

图6 不同码率下的性能对比Fig.6 Performance comparison of different code rates

5.4 不同信道环境下BER对比

在确保系统基础性性能和核心模块参数满足协议指标后,为了更直观地评判系统在模拟真实多径信道环境下的抗多径干扰性能,分别对系统在高斯信道(信道1)、添加3GPP经典多径模型之一的高斯信道(信道2)和添加了逼近CP极限时延的多径模型下的高斯信道(信道3)三种信道环境下作性能仿真验证。

图7中给出了MCS_0和MCS_4在三种信道环境下的BER比对图,可见系统对应的两种典型MCS下,添加了多径干扰的信道环境时,系统仍能保持与高斯信道环境下相当的BER,系统整体具有较好的抗多径干扰能力。特别是信道3的仿真结果进一步表征了系统在ITU-2092建议书中所提假设(100 kHz带宽、信道原始吞吐速率为76.8 ksymbol/s)下,即系统可能存在严重多径干扰时,仍能保持相对优良的误码性能。

图7 不同信道环境下同种MCSs的性能对比Fig.7 Performance comparison of different MCSs in different channel environment

6 系统硬件设计与海上验证

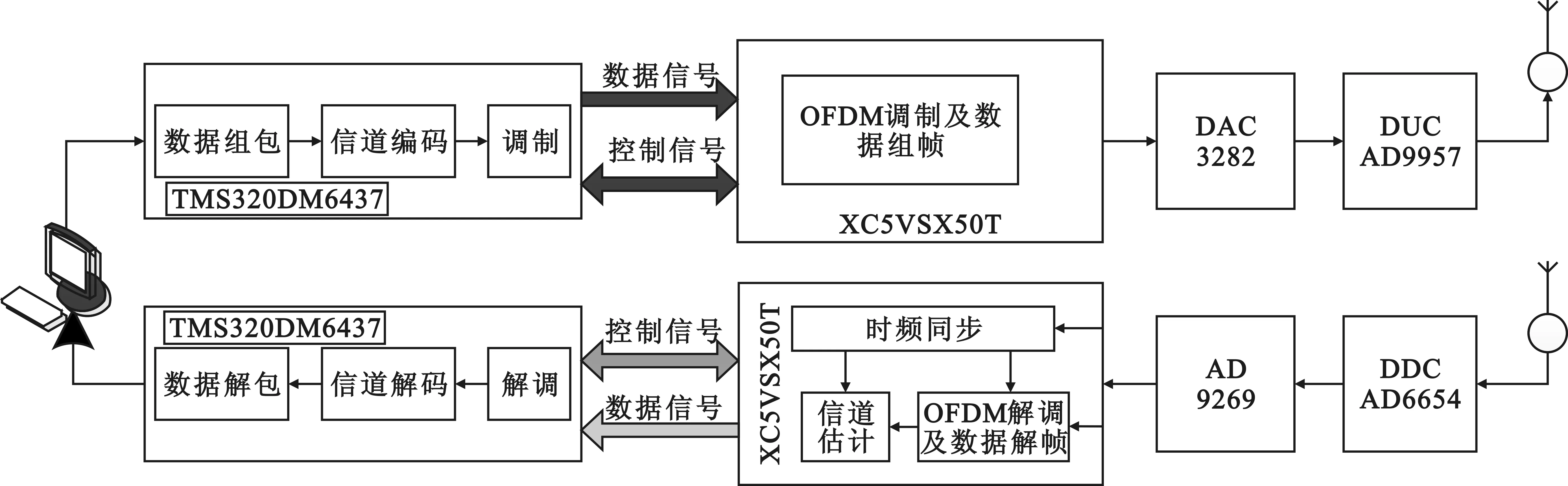

图8 系统硬件设计框图Fig.8 Diagram of system hardware design

本文在硬件设计过程中,综合考虑DSP编程灵活、拥有方便实现任务管理的BIOS内核与FPGA丰富自由的IO引脚、能够快速并行处理数据等优点,分别对DSP和FPGA进行了功能区域划分,具体如图8所示。原始数据由PC机通过USB高速总线传送到DSP内部,数据信号在完成数据组包、信道编码、调制后传递给FPGA进行相应前端数据操作,并完成OFDM调制与组帧以及后续的升采样滤波、IQ调制,然后将数据信号传递给DAC芯片,最终转换为161.837 5 MHz的具有完整帧格式且符合传输带宽要求的中频模拟信号输出至射频模块[15]。同理,接收端的硬件流程设计与发射端逆向对应。

硬件系统联调测试结果与MATLAB链路仿真结果基本一致,很好地验证了系统的整体性能和各项通信指标。

同时,硬件系统在大连海域进行了实际环境下的点对点系统测试。海上测试过程中,分别对相对船速、天线高度、天线仰角、天线增益、最小等效全向辐射功率等条件进行分组设置。同时为确保测试有效性,对系统进行了多次多海域、不同气象环境下的长时间持续通信测试,并对大时延信道环境下的抗多径性能进行了验证。实测结果符合设计预期,特别是系统最大极限空口速率可达312.7 kbit/s,在逼近CP极限时延的场景下系统误码率和误块率均表现优良,系统体现出很好的抗多径性能。

7 结束语

本文在VDES系统协议框架下,将OFDM技术引入VDES地面子系统,完成了对系统时隙结构的重新设计,设计并实现了基于OFDM技术的VDES地面子系统的底层通信链路系统。在经过仿真调试和海上实测验证后综合评估系统性能,表明融合OFDM技术后的系统平台与ITU_RM.2092建议书中系统的地面技术特性相比,各方面性能指标略有提升。同时系统完成设计目标,对VDES地面子系统抗多径问题进行了有益的探索和研究,系统表现出了良好的抗多径干扰性能。文中设计的系统在实现了将OFDM技术融入VDES地面子系统,提升了系统在大时延信道下的抗多径干扰性能,也为下一步研究工作提供了基础性框架和相应的性能参数,具有很强的实用性。后续的研究工作中,将根据系统当前所得参数为系统配置链路自适应控制模块,并进一步考虑系统组网等问题。