基于IPD工艺的无反射低通滤波器设计*

2018-07-26王浩洋邢孟江李小珍杨晓东

王浩洋,邢孟江,李小珍,张 磊,杨晓东

(1.昆明理工大学 信息工程与自动化学院,云南 昆明 650504;2.昆明学院 信息技术学院,云南 昆明 650214)

0 引 言

滤波器在电子系统中普遍存在,其理论研究和实用设计已经持续了一个世纪。在今天,实用性滤波器的设计和实现依然是电子通信领域最活跃的研究领域[1]。传统滤波器通过将阻带信号反射回源端达到滤波效果。这种抑制不需要信号的方式,有时可能由于非线性器件中的杂散混合、敏感有源组件的无意重新偏置或各种信号路径之间的串扰,而导致与系统中其他组件的有害交互[2]。一直以来,设计人员针对减小反射提出了一些措施。比如,在敏感器件前后插入衰减器或隔离放大器,但会降低整个系统的信噪比和动态范围;利用双工器一个端口实现对阻带反射信号的吸收,但这对设计电路有较大的空间需求,且仍然会因为一些反射信号造成阻抗失配;使用差分式滤波器缓解阻带反射信号的影响,使得滤波器的带宽受制于电桥的带宽,使之不适合宽带应用[3];通过卓越的阻抗匹配减小反射,需要很大数量的元件,即使一阶滤波器也需要很多元件[4]。

这些改善方法效果不明显,还会带来其他弊端。因此,设计者开始从拓扑角度关注无反射滤波器的研究。2011年,美国国家射电天文台Matthew A. Morgan等提出了新型的无反射滤波器拓扑结构和设计方法。为验证理论,用分立元件设计测试了325 MHz的无反射低通滤波器和中心频率210 MHz带宽200 MHz的无反射带通滤波器[1]。2014年,电子科技大学秦巍巍等提出了采用微带线结构实现的一种新型吸收式带通滤波器。该滤波器通带内插入损耗小于3 dB,通带电压驻波比小于2,带外驻波比在很大频率范围内小于3.5[5]。同年,上海交通大学张程等利用耦合相消原理设计了一种调频频率为5.17~5.56 GHz的无反射可调带阻滤波器。该滤波器在通带内插损值约为0.44 dB,在阻带抑制大于15dB 的基础上,回波损耗保持在10 dB以上[6]。2016年,韩国的Tae-Hak Lee等人提出了一阶无反射集总元件低通和带通滤波器的设计方法,并采用集总式表面贴装器件(SMD)的方式,设计加工了中心频率为95 MHz、3 dB带宽、30 MHz的无反射带通滤波器[4]。

无反射滤波器从分立元件到集总元件的发展过程,说明了无反射滤波器小型化的必然趋势。它在追求更小器件体积的同时,实现了更小的阻带信号反射。薄膜集成无源器件(Thin Film-Integrated Passive Device,TF-IPD)工艺具有高精度、小尺寸、高可靠性及与半导体工艺相兼容等优点。使用灵活的材料和工艺流程,降低了杂散电感和杂散电容的影响,提高了无源器件的性能,适合于高频应用。IPD工艺与新型无反射滤波器拓扑结合设计制作无反射低通滤波器,能在减小器件尺寸的同时实现更好的无反射效果。

本文基于IPD工艺和新型电路结构设计了一款无反射低通滤波器,其3 dB截止频率为1.25 GHz,带外抑制在1.25~8 GHz之间大于20 dB,带内回波损耗大于28 dB,带外回波损耗在1.25~7.5 GHz之间大于27 dB。器件尺寸仅为1 mm×1 mm×0.3 mm,在许多不同应用中优势明显。

1 IPD工艺

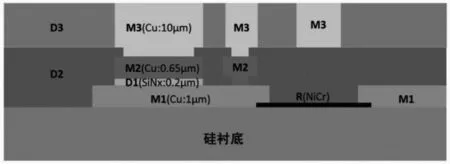

本文所设计无反射低通滤波器采用硅基薄膜集成无源器件工艺[7-9]。衬底采用的高阻硅具有价格低、热导率良好与IC制作工艺兼容等优点。电容采用MIM薄膜电容,利用金属作为电极,降低了电阻值,提高了元件共振频率,适用于高频应用。所用电容均为平行板电容器,两极板之间填充高介电材料提高电容量。电感采用平面螺旋电感,通过硅平面刻蚀技术实现,主要设计考虑如何降低其寄生电容和提高品质因子(Q)。考虑到降低其直流阻抗可以提高Q值,所以电感导线的膜厚设置为10 μm。电阻由NiCr合金组成,采用磁控溅射共沉积方法获得精准电阻。

图1所用IPD工艺叠层图,给出了每一层的材质和厚度。其中,R为NiCr高精度薄膜电阻;M1为1 μm的Cu层,用于互联和MIM电容的下极板;M2为0.65 μm的Cu层,作为电容上极板;M3为10 μm的Cu层,用于实现电感和互联;M1和M2之间的D1层为0.2 μm的SiNx,作为MIM电容的电介质层;D2和D3都是低k电介质层,用于绝缘隔离。

图1 硅基IPD工艺叠层图

2 理论推导与电路设计

2.1 理论推导

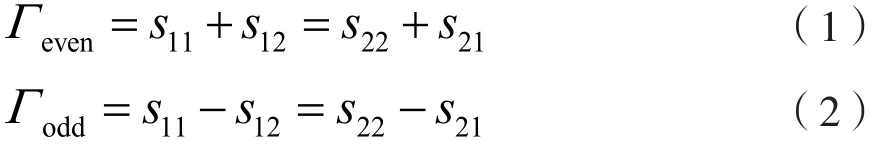

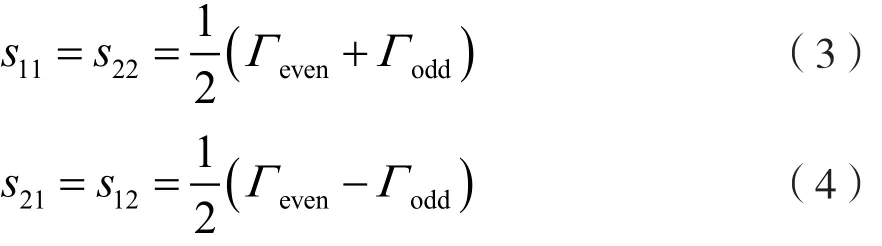

为设计无反射低通滤波器,从一个结构对称的二端口网络开始。对称平面将其分成完全对称的两部分。当施加偶模信号时,因为两端口的信号同相且相等,所以对称平面上没有电流通过,通过对称平面的线相当于断路。此时,这个半电路为偶模等效电路,反射系数为Γeven。当施加奇模信号时,因为两端口的信号相等且反相,所以通过对称平面对地电压为零,通过对称平面的节点相当于对地虚短。此时,这个半电路为奇模等效电路,反射系数为Γodd。

根据线性网络的叠加性,得到:

从而得到:

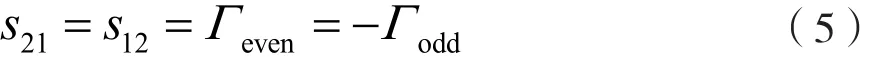

为得到无反射滤波器,s11和s22应为0,得到:

由式(5)可知,偶模等效电路中反射的频率为最终两端口网络传输的频率,说明偶模等效电路和最终全两端口网络的阻带和通带是相反的。以低通滤波器为设计目标时,应以高通滤波器作为偶模等效电路。

得:

由式(6)可知,要使滤波器无反射,需要偶模等效电路的输入阻抗和奇模等效电路的输入导纳相等,这被称作对偶条件。

2.2 电路设计

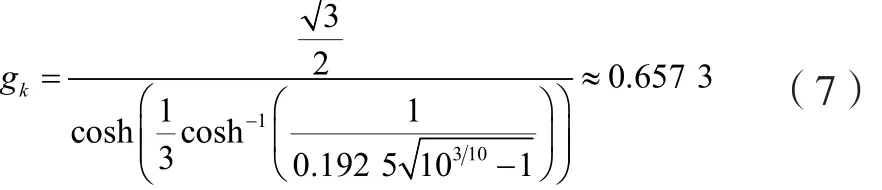

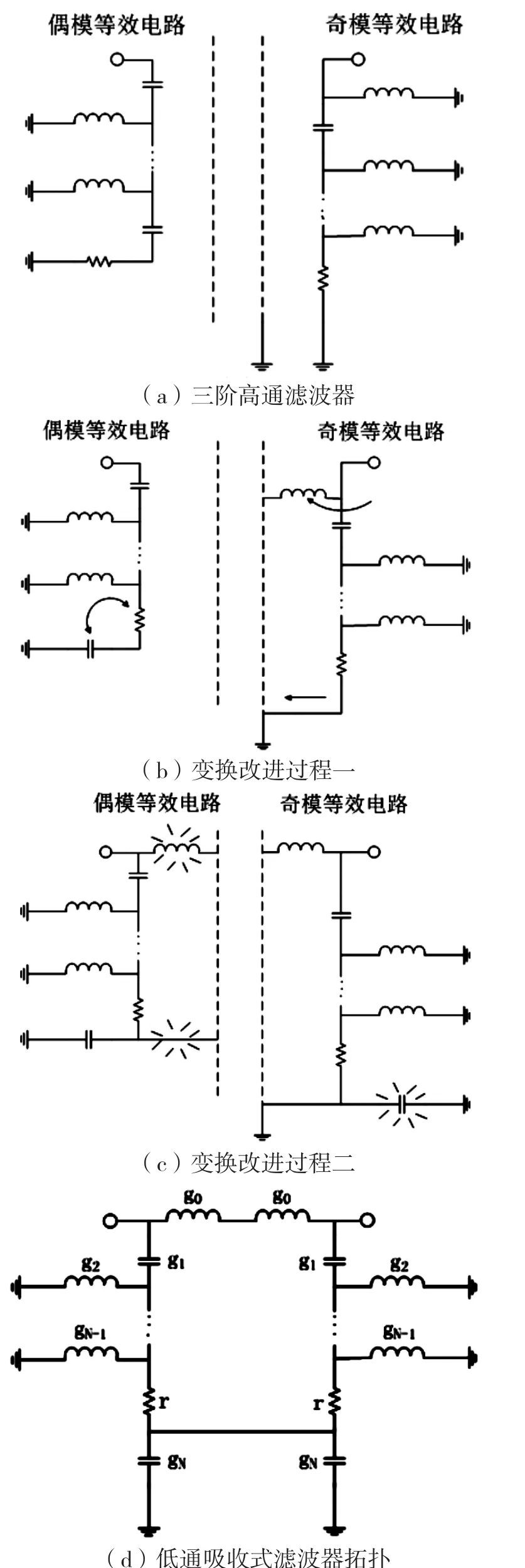

本文以三阶高通滤波器作为设计起点,如图2(a)所示。画出其对偶作为奇模等效电路,依然为高通。此时,并不能看出奇偶模等效电路关于对称平面对称。为了得到对称网络,在不改变原网络输入阻抗和频率响应的情况下,对电路进行以下变化以恢复对称结构[10]。如图2(b)所示,在偶模一侧交换最后的电容和串联的终端电阻的位置;在奇模一侧改变第一个电感和终端电阻的接地连接,由绝对接地变为虚拟接地。如图2(c)所示,在偶模一侧于输入节点和对称平面(是一个开路电路)之间添加一个电感;相似地,在电阻和对称平面之间添加一个开路连接线;在奇模一侧于对称平面(虚短)到地之间添加一个电容。经过以上变换,得到无反射低通滤波器如图2(d)所示,然后根据目标指标求个元件值。

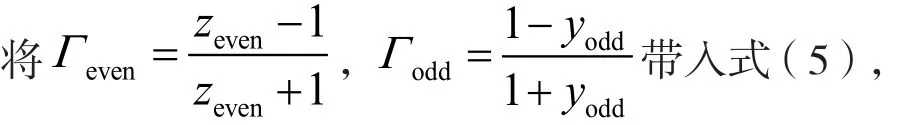

根据文献[11]可知,以3 dB截止频率为设计指标的gk如下:

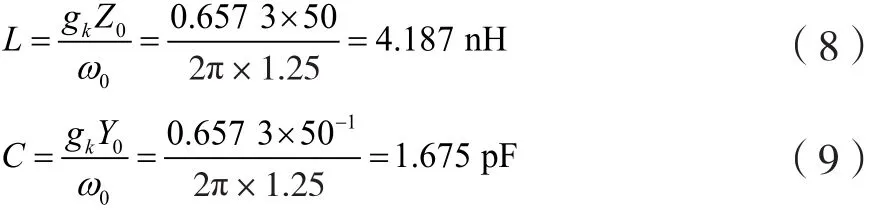

于是,可以计算特征阻抗为50 Ω,3 dB截止频率为1.25 GHz的无反射低通滤波器的元件值为:

图2 无反射低通滤波器拓扑推导

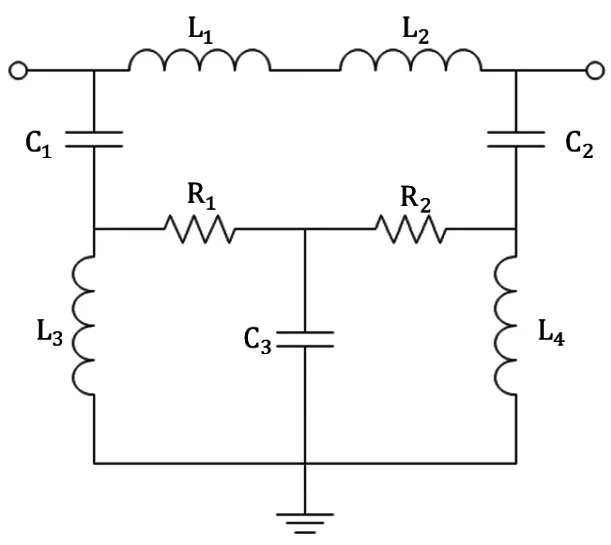

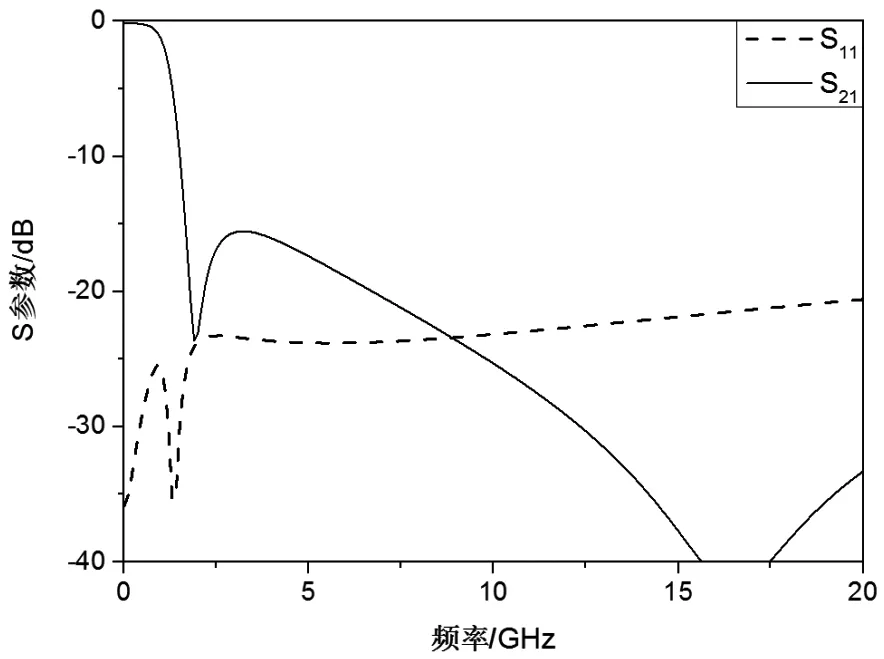

图3为本文设计的三阶无反射低通滤波器的电路原理图。基于图3的电路拓扑和计算得到的元件值,在Ansoft Designer中建立电路并进行仿真优化,得到如图4所示的S参数仿真结果。由图4可知,该滤波器3 dB截止频率为1.25 GHz,带外抑制大于15 dB,回波损耗大于20 dB,满足设计要求,能良好地实现无反射。

图3 无反射低通滤波器原理

图4 无反射低通滤波器的Ansoft Designer仿真结果

3 无反射低通滤波器的建模与仿真

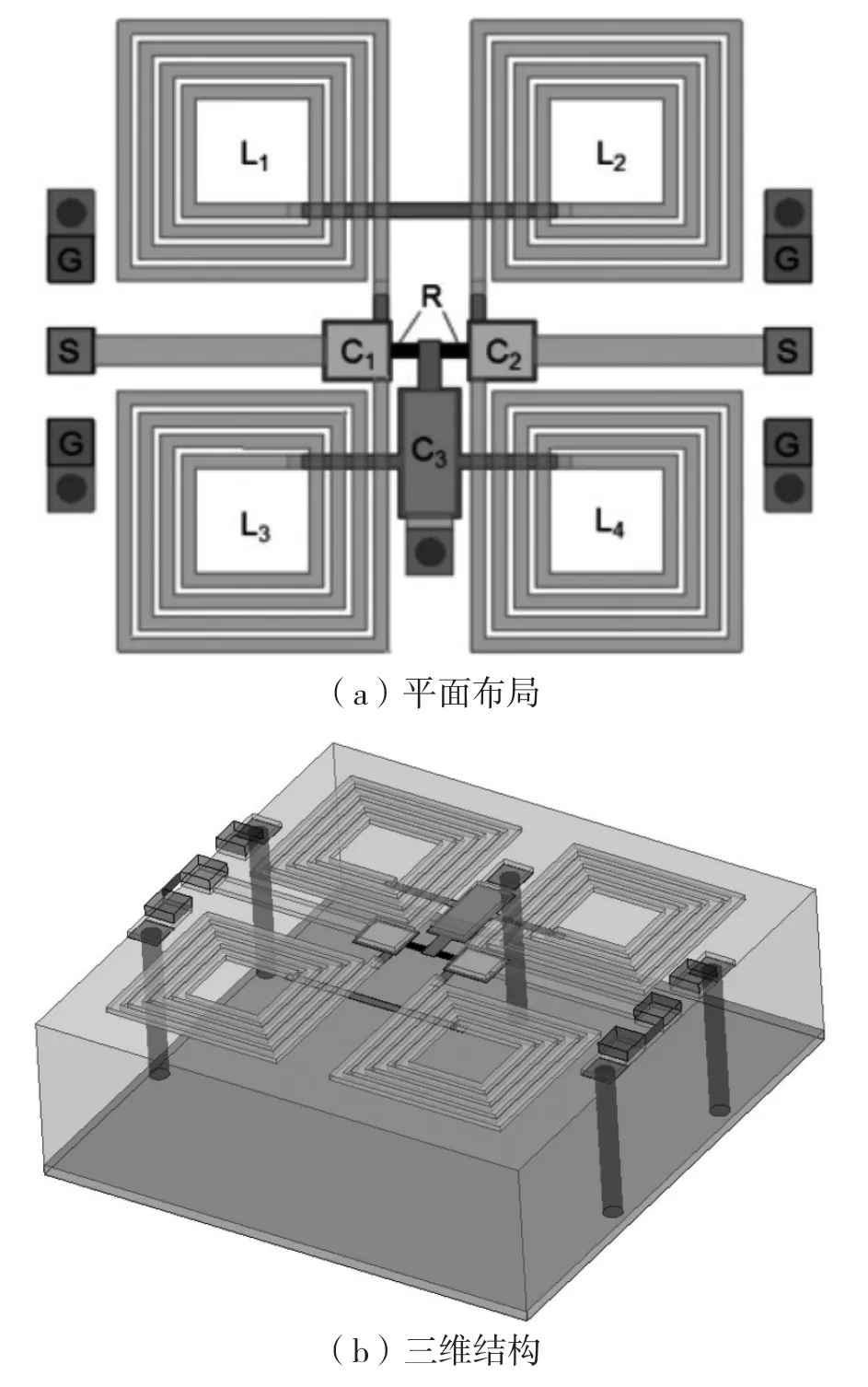

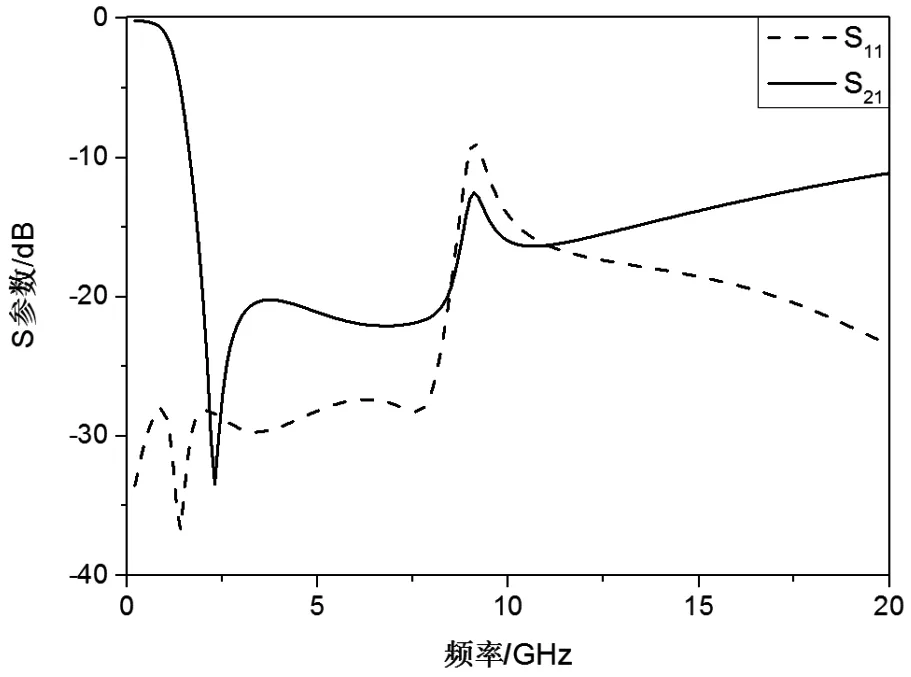

当得到设计的无反射低通滤波器Ansoft Designer的仿真优化结果后,本文基于IPD工艺设计标准,在三维电磁场仿真软件HFSS中建立其三维电磁模型并进行仿真。模型采用平面螺旋电感、MIM薄膜电容和NiCr薄膜电阻。衬底厚度300 μm,平面结构如图 5(a)所示。在1 mm×1 mm的平面结构中,主导器件面积的是螺旋电感,使之均匀分布于四个象限,以减小整体面积。S为信号端,G为接地端,均通过金属垂直通孔接地。图5(b)是无反射低通滤波器集成无源器件三维结构图。用HFSS对模型进行仿真,得到插入损耗(S21)和回波损耗(S11)如图6所示。可知,其3 dB截止频率为1.25 GHz,带外抑制在1.25~8 GHz之间大于20 dB,带内回波损耗大于28 dB,带外回波损耗在1.25~7.5 GHz之间大于27 dB。仿真结果符合设计要求,能良好地实现无反射。分析可知,HFSS的仿真结果与原理图的Ansoft Designer仿真有偏差,原因在于原理图仿真中所加寄生电感不能完全表现模型中的寄生效应。

图5 无反射低通滤波器模型

图6 无反射低通滤波器的HFSS仿真结果

4 结 语

本文基于IPD工艺设计了一款三阶无反射低通滤波器。通过HFSS建模仿真得到该滤波器3 dB截止频率为1.25 GHz,带外抑制在1.25~8 GHz之间大于20 dB,带内回波损耗大于28 dB,带外回波损耗在1.25~7.5 GHz之间大于27 dB。器件尺寸仅为1 mm×1 mm×0.3 mm。这款滤波器体积小、精度高、阻带信号吸收良好,能有效减少各信号路径之间的串扰,在许多对反射信号敏感的电子系统中具有良好的应用优势。