基于VHDL控制的烤面包机

2018-07-23大连理工大学城市学院丁书亚谢印庆石海锋

大连理工大学城市学院 丁书亚 谢印庆 石海锋

1 引言

随着人们生活节奏的加快,面包在早餐中的比重越来越重,面包加牛奶成为最受欢迎的早餐搭配之一,然而不经加工的切片面包无论是口感还是色泽都欠佳,基于这种状况烤面包机的出现很有必要。

本文基于VHDL控制的烤面包机设计,内置状态控制电路、数据装载电路、计时电路、显示译码电路四个模块。可控制烤面包机的加热、停止等状态并实时更新显示数据。烤面包机设定烘烤时间,放入切片面包,机器自动开始计时,到达指定时间后,烤面包机停止烘烤,将面包弹出,无需担心因无人看管而导致面包烤糊的情况,并且本设计结构简单,可以量产。

2 系统设计

2.1 系统设计方案

烤面包机系统由四个电路模块组成。其中包括控制烤面包机的工作状态转换并发出控制信号的状态控制电路;控制定时、测试数据、计时并完成信息载入的数据装载电路;通过时钟计数并发出烘烤完成信号的计时电路;显示各种工作状态的显示译码电路。[1]

如图1所示为烤面包机的系统框图。

图1 烤面包机系统框图

烤面包机的工作流程如下:首先,对系统进行复位清零;设置信号SET_T有效时,将烘烤时间读入DATA【15…0】,系统复位并显示设定时间。按下开始键START,系统进入烘烤状态,COOK信号变为高电平,计数器开始运算,显示烘烤时间。烘烤结束,系统恢复初始状态,数码管显示烘烤结束信息。

当系统处于复位清零状态时,按下显示管测试按钮TEST,将对显示管是否正常工作进行测试,正常工作时,显示管输出全1。[2]

2.2 硬件设计

2.2.1 状态控制模块

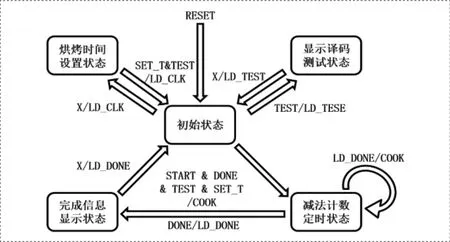

状态控制模块的功能是根据输入信号和当前状态,完成状态转换以及输出控制信号,四个输出端LD_DONE、LD_CLK、LD_TEST、COOK分别指示烘烤结束状态信息、输入时间、测试数据并显示驱动信息、烘烤的状态并控制计时器计数。[3]

图2 状态控制器状态转换图

根据烤面包机工作流程,对状态转换条件和输出信号的分析,可以得到如图2所示的烤面包机的状态转换图。

当RESET信号有效时,系统复位清零;输入和输出对应四种状态,分别为:烘烤时间设置、显示译码测试、完成信号显示以及减法计数定时,并进行相应的转换。

2.2.2 数据装载模块

数据装载模块(loader)中LD_DONE、LD_CLK、LD_TESTLOAD都为高电平有效的端口,分别用来输出烘烤完成的信息、输出设置的烘烤时间、输出测试数据;LOAD用于指示电路信号模式。

2.2.3 计时模块

计时模块(counter)中LOAD和COOK均为高电平有效;烘烤结束用DONE表示,用MIN和SEC显示剩余时间、测试状态以及烘烤完成状态信息等。

3 系统仿真及原理图

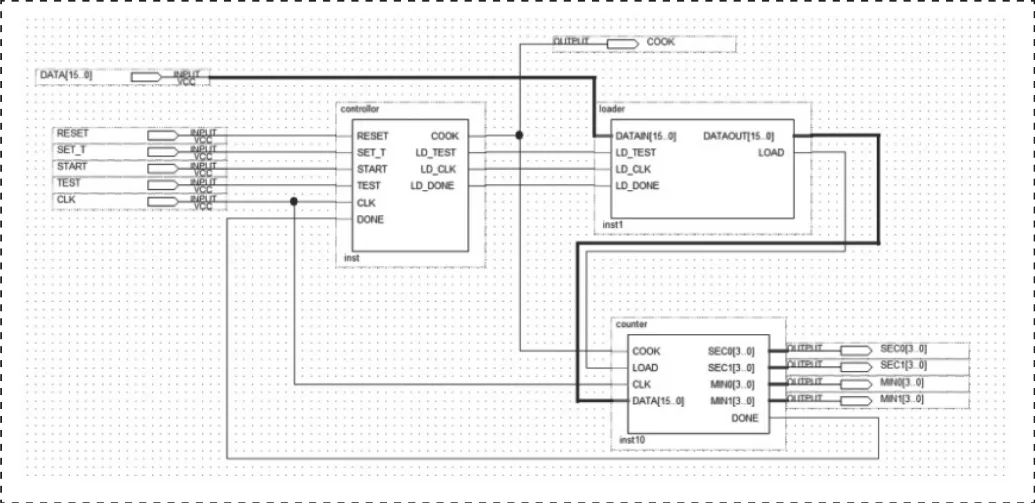

3.1 系统原理图(图3)

图3 烤面包机原理图

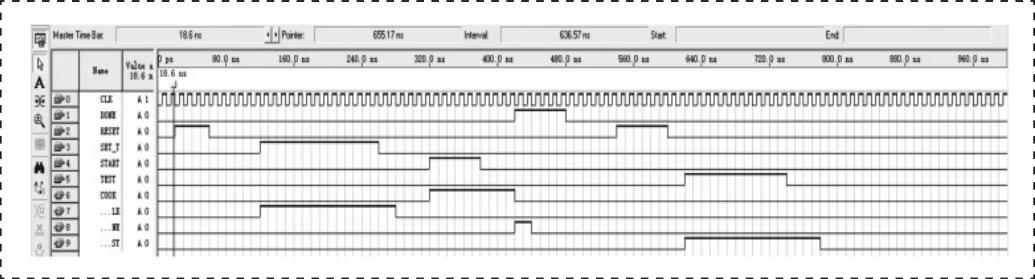

3.2 状态控制电路模块的仿真(图4)

图4 状态控制电路模块的仿真

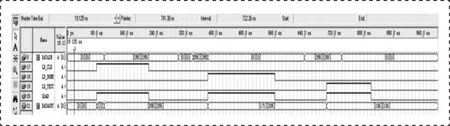

3.3 数据装载电路模块的仿真(图5)

图5 数据装载电路模块的仿真

通过以上两个部分的仿真图以及系统的原理图可以看出,此系统能够实现烤面包机预期的基本功能(计时电路及复位和测试功能的仿真省略)。[4]

4 结束语

本文设计了一个基于VHDL控制的烤面包机,可实现定时、烘烤、停止、状态显示等功能。相较于其他语言,VHDL语言功能强大、设计灵活、支持广泛,具有强大的系统硬件描述能力。本设计使烤面包机从烘烤到结束全自动化进行,节省了人们日常生活中的时间,提高了成功率,避免了面包烤糊、烤生等口感不佳的情况。同时结构简单、可形成生产链,在经济与未来发展的角度具有实际意义。