基于TSV技术的3D电感的设计与实现

2018-07-17张洪泽刘鹏飞

薛 宇,张洪泽,刘鹏飞,朱 健

(南京电子器件研究所,江苏 南京 210016)

摩尔定律发展到现阶段,行业内有两条路径:一是继续按照摩尔定律往下发展,走这条路径的产品有CPU、内存、逻辑器件等,这些产品占整个市场的50%;另外就是所谓超越摩尔定律的 “More than Moore”路线,芯片发展从一味追求功耗下降及性能提升方面,转向更加务实的满足市场的需求。这方面的发展包括了模拟/RF器件、无源器件、电源管理器件等,大约占到了剩下的50%市场[1]。

三维集成电路(3D IC)被认为是超越摩尔定律最有前途的选择。三维集成并不是一味地进行小型化,而是利用垂直维度实现更高的集成密度,具有更短的导线长度、更小的占地面积、更高的速度和更低的功耗,并且与当前的技术完全兼容。

硅通孔(Though Silicon Via,TSV)技术的出现将集成电路的发展带入了三维时代,是实现三维集成电路的关键技术。TSV技术通过在硅衬底上打孔,填充金属,实现芯片之间高纵横比的垂直互连,形成垂直信号、电源和散热路径。为实现多功能、高速度、高集成度的集成电路提供了良好的解决方案。同时,硅通孔也被用于制作集成无源器件,其中之一便是3D电感。与传统结构的片上电感相比,基于TSV的电感可以实现更小的占位面积和更高的电感密度。

硅基集成电感是射频集成电路的重要元件之一,在放大器、混频器、压控振荡器等电路中发挥着重要的作用。然而常用的硅基集成电感采用的是平面螺旋结构,在CMOS工艺中,组成螺旋电感的绕线金属电阻较大,硅基衬底损耗较高,使得螺旋电感品质因数(Q值)很难提高,同时平面绕线结构所占面积较大,这些都影响集成电感在实际电路中的应用[2-6]。

为了在减小占用空间的同时达到更高Q值与电感密度,本文提出了基于TSV技术的全新3D螺旋电感模型,分析该电感模型的损耗原理,通过软件HFSS对电感性能参数进行仿真研究并做出实物。对3D螺旋电感进行性能测试,研究其可行性,使其能够满足高性能无源集成器件的要求。

1 3D电感的结构模型与损耗原理

1.1 3D电感的结构模型

图1是基于TSV技术的4匝3D螺旋电感模型。它利用TSV和厚导电金属(在顶层金属层或RDL层上)来形成电感回路。该结构的电感具有布线层上的占位面积最小、高电感密度的优点。

图1 3D电感的结构示意图Fig.1 Perspective view of 3D inductor

1.2 金属损耗

3D电感中的损耗主要分为金属损耗和介质损耗。

当3D电感的金属导体中流过信号电流时,导体电阻会引起欧姆损耗。导体电阻分为直流电阻Rdc和交流电阻Rac。其中,直流电阻与导体的长度成正比,与横截面积成反比。

3D电感体内的电流分布会随着信号频率的上升产生趋肤效应和临近效应。趋肤效应和临近效应都会使金属的有效导电截面积减小,从而增大电阻,进而加大损耗,使得电感的Q值降低。

相比于平面片上螺旋电感,3D电感在水平方向上也受到工艺对金属层的线宽和厚度限制,而在垂直方向,TSV的横截面积比水平金属线的横截面积大,因此电阻值相对较小。

1.3 介质损耗

在3D电感中,衬底损耗分为电场引起的损耗和磁场引起的损耗。电场引起的损耗是电感中的部分电流以位移电流的形式,金属和衬底之间产生耦合电容流入衬底,从而损耗部分能量。磁场引起的损耗是由电感的交变磁场在衬底中感生出涡流产生,涡流可以在衬底中产生热损耗,并且由于其具有时变性,这就会使涡流的磁场阻碍电感的磁场变化,从而影响电感值。

与平面电感相比,3D电感因TSV直接穿过Si衬底,因此与衬底的耦合更加紧密。同时,螺旋管轴线方向上磁场完全穿过Si衬底,因此引起的涡流损耗更大[7-8]。

2 仿真与分析

本文3D电感尺寸参数设计如表1所示。其中,硅通孔半径为10 μm,相邻TSV之间的间距为150 μm,相对TSV之间的间距为450 μm,水平金属线的宽度与硅通孔直径保持一致为20 μm,电感匝数N取4。硅衬底的厚度为200 μm,且具有高电阻率。整个4匝3D电感的占位面积保持在500 μm×500 μm以内。

表1 3D电感的尺寸参数Tab.1 3D inductor size parameters

3D电感的S参数由全波高频三维电磁仿真软件HFSS仿真,结果如图2所示。

图2 3D电感的S参数仿真结果Fig.2 S-parameter simulation for 3D inductors

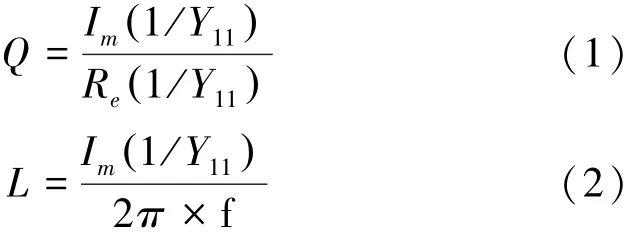

利用公式(1)、(2)得到3D电感的Q值与电感值的仿真数据如图3所示。

式中:Y11为二端口网络中2端口短路时1端口的输入导纳;Im为虚部;Re为实部;f为频率。

图3 3D电感Q值与电感值仿真结果Fig.3 Quality factor and inductance simulation for 3D inductor

3 工艺实现

基于TSV技术的3D电感首先采用具有高电阻率的硅作为衬底材料,由处于硅衬底顶部和底部金属层中的水平金属线和垂直穿透硅衬底的硅通孔共同构成。

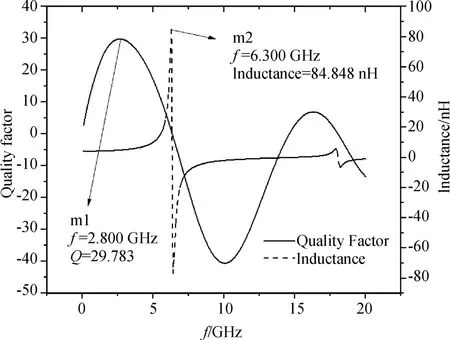

制造3D电感的工艺流程图如图4所示。首先制作TSV:第一步光刻出TSV图形,经打底膜去胶后,通过ICP刻蚀出TSV通孔,采用PECVD工艺沉积绝缘层SiO2和SiN、PVD工艺沉积阻挡层Ta和种子层Cu,阻挡层跟种子层制备完成后采用电镀填充金属Cu、CMP正面抛光,至此,TSV基本制作完成;然后制作金属连接线:经第二步光刻出正面金属层连接线图形,电镀6 μm金属层Au后采用临时键合工艺将硅片背面减薄至200 μm,后经第三步光刻出背面金属层连接线图形,同样电镀6 μm的金属层Au,至此,金属连接线全部制作完成;最后划片得到待测试的3D电感。

图4 工艺流程图Fig.4 Process flow

图5为高倍显微镜下的3D电感实物图。

图5 4匝3D电感正面图Fig.5 Top view of 4 loop 3D inductor

4 测试结果与分析

采用Cascade Summit 9000探针台和Agilent 5234A矢量网络分析仪对3D电感进行测试,S参数测试结果如图6所示。

图6 4匝3D电感的S参数Fig.6 S-parameters for 3D inductors with number of turnsN=4

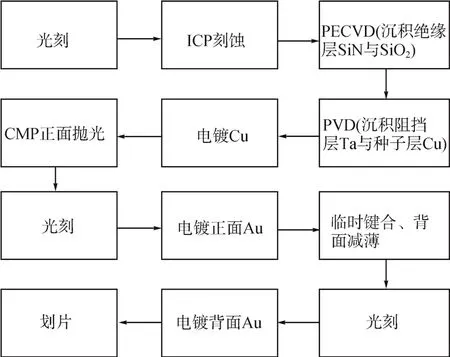

利用公式(1)、(2)计算得到3D电感的Q值与电感值的实测数据如图7所示。

图7 4匝3D电感的Q值与电感值Fig.7 Quality factor and inductance for 3D inductors with number of turnsN=4

由图可见,4匝3D电感在占位面积仅为500 μm×500 μm的情况下,其Q值在2.55 GHz可以达到峰值25左右,电感值在3 GHz内可以稳定在4 nH左右,在5.7 GHz可以达到50 nH左右,自谐振频率为6 GHz左右,与仿真结果基本保持一致,其间误差由工艺误差比如电镀金属层的厚度误差等以及测试误差所致。

5 结论

本文首先提出了基于TSV技术的3D电感的概念,然后构建了3D电感的模型,讨论了其损耗机理,最后展示了软件仿真结果与实物测试结果,并进行了比较与分析,结果证明基于TSV技术的3D电感的可行性,实现了更高的Q值、更小的占地面积,并为TSV技术在诸如滤波器等无源器件中的应用奠定了基础。