一种提高功率MOSFET击穿电压的终端结构

2018-07-03林洪春

林洪春,薛 斌

(中国电子科技集团公司第四十七研究所,沈阳110032)

1 引言

功率MOSFET器件的固有特性及应用前景,决定了其市场占有率将逐渐增高。而国外公司对高性能MOSFET的技术垄断及禁运,使用户直接面临断货的风险。因此,开发中高压大电流MOSFET迫在眉睫。中高压MOSFET的击穿电压与管芯面积及导通电阻的矛盾,一直是制约MOSFET性能的关键[1]。以此为突破口,基于对MOSFET的结构特征和电学特性的深入了解,重点研究在提高MOSFET击穿电压的同时,如何尽可能小地影响其他参数,比如保证衬底电阻率不变、导通电阻没有明显提高等等,具有很大的现实意义。

2 MOSFET的结构特点

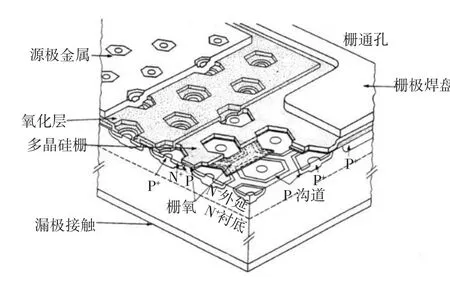

MOSFET最基本结构为垂直导电双扩散VDMOS型,源极的形状(基本单元)有三角形、正方形、六角形等多种设计。图1所示即为功率MOSFET的基本结构。图中每一个六角形是一个MOSFET的原胞(cell),因为原胞是六角形的(hexangular),所以常把它称为HEXFET。典型的功率MOS器件一般采用多晶硅作为栅极,使工艺大为简化,同时也降低了沟道电阻。

图1 功率MOSFET的基本结构

图1中已标明了漏和源。漏源之间的电流通过一个沟道上的栅来控制。按MOSFET的原意,MOS代表金属 (Metal)-氧化物 (Oxide)-半导体(Semiconductor),即以金属层的栅极隔着氧化层利用电场的效应来控制半导体[2],场效应晶体管(Field Effect Transistor,FET)的名字也由此而来。然而HEXFET中的栅极并不是金属做的[3],而是采用多晶硅(Poly)来做栅极,也就是图中所注明的多晶硅栅。

导通电阻Ron是影响功率VDMOSFET最大输出功率的重要参数之一。当器件导通的时候,就有电流流过导通电阻,在导通电阻上形成导通压降,导致在电阻上有功率损耗。在器件的设计过程中可以通过优化外延参数、元胞结构的设计、单胞结构的布局以及芯片面积等因素减小导通电阻。器件的导通与击穿电压成矛盾关系,在提高击穿电压的同时降低导通电阻是当前厂商关心的焦点,文中研究的终端结构在不牺牲芯片面积降低导通电阻的同时,提高了MOS管的击穿电压。

3 MOSFET的终端结构

3.1 击穿电压

漏源击穿电压BVDS为VGS=0时在漏源间所加的最大反偏电压,它表征了器件耐压的极限能力[4]。对于VDMOS器件而言,其芯片内部有源区各个元胞在表面和体内有基本相同的电位,因此元胞之间并不存在击穿的问题[5]。但是,在最外圈的元胞与衬底之间,存在由于上述原因引起的高电压和高电场,会大大降低器件的耐压能力[6]。为此,需额外增加终端结构设计以减少器件边缘及表面的电场集中,提高击穿电压。

3.2 提高击穿电压的设计

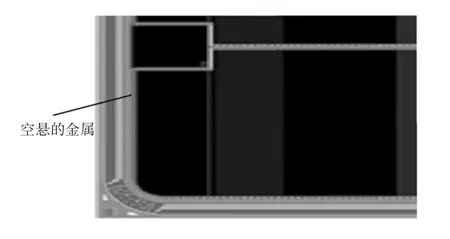

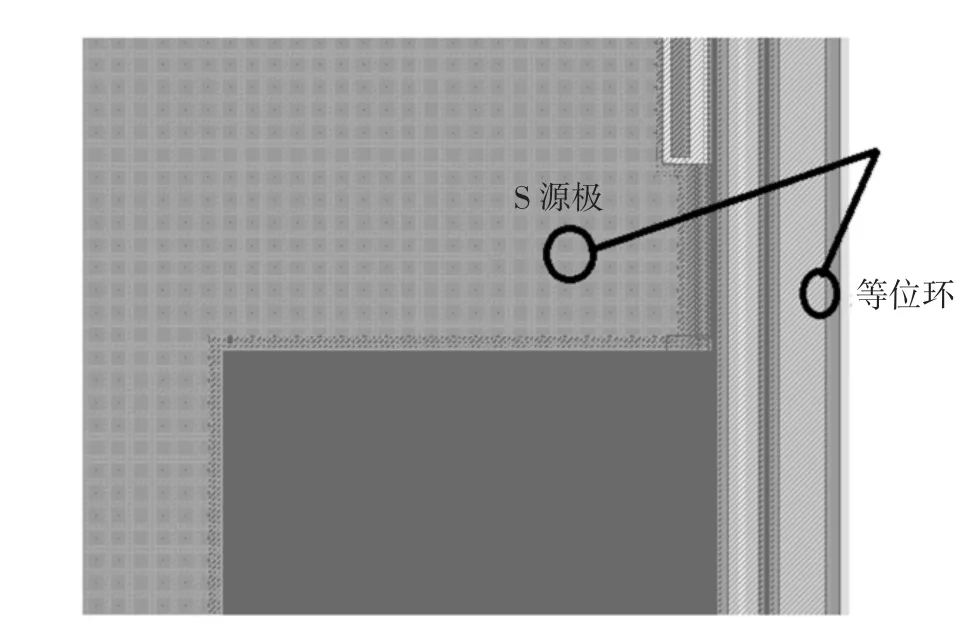

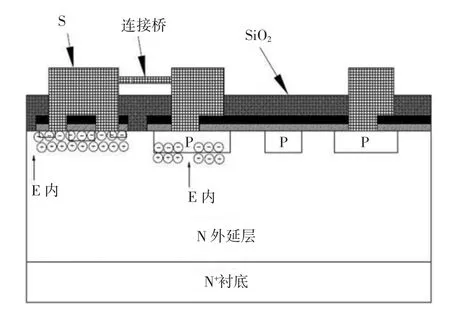

一般的情况下等位环上面的金属采用空悬的方法设计,但这样只能利用金属势垒的作用来减小等位环下的电场集中效应,作用不十分明显。如果想要提高VDMOS器件的击穿电压,需要多个分压环起作用,这样不仅浪费了芯片的面积,降低了器件的电流密度,而且芯片外端的分压环还有可能起不到缓解电场的作用,继而器件就产生了击穿。设计采用一个等位环,一个分压环,即可解决耐压和导通电阻矛盾的问题。图2为普通结构的VDMOS终端,图3为采用S极等位的VDMOS终端结构。

图2 普通结构的VDMOS终端

图3 采用S极等位的VDMOS终端结构

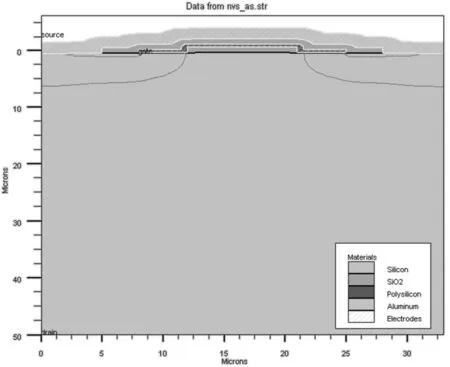

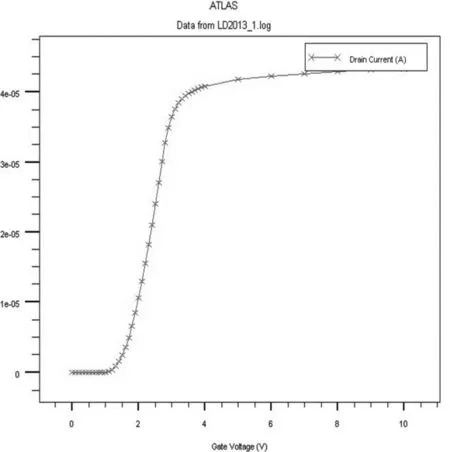

完成终端设计后,采用TCAD模拟2D元胞模型进行了模拟仿真,仿真结果如图4、图5和图6。其中,图4为TCAD模拟2D元胞模型、图5为2D元胞模型开启曲线仿真结果、图6为2D元胞模型输出特性仿真结果。

由于理论计算的结果与实际参数要求存在差异,在器件模拟仿真过程中要不断地修正器件尺寸参数、调整网络优化,直至得到理想器件输出特性参数。

图4 TCAD模拟2D元胞模型

图5 2D元胞模型开启曲线仿真结果

图6 2D元胞模型输出特性仿真结果

图7 采用S极等位的VDMOS终端结构

4 终端结构原理

第一分压环和第二分压环(等位环)如图7所示。其中,第一分压环与源极通过金属连接,以形成电压等位环。此结构设计第一分压环和第二分压环,通过将第一分压环与源极金属连接,使第一分压环在通电状态下与源极电压始终相等,构成等位环。这种设计,与现有技术中通常采用电阻率相同的衬底的情况相比,MOS器件反向击穿压有大大的提高。

在一般的提高击穿电压的设计方法中,设计原理为器件引出端S极通过金属化工艺、腐蚀及刻蚀工艺,与器件的第二分压环(等位环)进行连接,经过金属连接后的两个区域的电压值相等。设计的目的为S极下方的P阱电场经S极加反偏电压后,电场向器件的等位环方向延伸,到达一定边界条件后,由第二个等压环承接,以此类推,增加多个等压环来提高击穿电压[7]。但这样的做法浪费了器件的面积,同时,等位环上面的介质层质量很难控制,稍有工艺误差,就将会引起器件下面电场的集中分布,不仅没有提高击穿电压,反而容易在损坏的边缘造成击穿。

新方法采用S及阱与等压环电压等位,如图7所示。器件内部电场E内在加上反偏电压后,电场线将向器件外部延伸。在延伸到等位环的时候,由于电场线在等位环E内处于器件内部等压,这样能有效地吸收电场,提高击穿电压能力,且节省了多余等压环会占用的芯片面积,终端工艺也相对简单[8]。节省下来的器件面积用来提高单位器件的元胞数量,这样就解决了中高压MOSFET器件电压/电流与导通电阻的矛盾关系,从而实现了研制目标[9]。

5 结束语

基于上述研究,最终使用Sivaco TCAD和Sentaurus TCAD对器件进行模拟仿真,绘制了器件的版图,投产流片。在实际的流片完成后,实测得知:源漏击穿电压≥400 V;连续漏极电流≥14A;导通电阻≤3Ω。同时,对器件进行了封装及测试考核,所有技术指标均已达到设计要求。

[1]SINGH P.Power MOSFET failure mechanisms[C]//Telecommunications Energy Conference,2004.Intelec 2004.International.IEEE,2004:499-502.

[2]YANG X,LIANG Y C,SAMUDRA G S,et al.Tunable oxide-bypassed trench gate MOSFET:breaking the ideal superjunction MOSFET performance line at equal column width[J].IEEE Electron Device Letters,2003,24(11):704-706.

[3]王佳宁.VDMOS终端结构研究 [D].南京:东南大学,2007.WANG Jianing.Research on VDMOS terminal structure[D].Nanjing:Southeast university,2007.

[4]王英,何杞鑫,方绍华.高压功率VDMOS管的设计研制[J].电子器件,2006,29(1):5-8.WANG Ying,HE Qixin,FANG Shaohua.Study on Power VDMOS of High Voltage[J].Chinese Journal of Electron Devices,2006,29(1):5-8.

[5]JaeyoungP,Dongjun K,Sanggyu P.DMOS-based avalanche-mode Power-Rail ESD Clamp for a 0.35μm BCD Process[J].Ieice Technical Report,2007,107:209-212.

[6]陈龙,沈克强.VDMOS场效应晶体管的研究与进展[J].电子器件,2006,29(1):290-295.CHEN Long,SHEN Keqiang.Research and Progressof VDMOS field-effect Transistors[J].Chinese Journal of Electron Devices,2006,29(1):290-295.

[7]石存明,冯全源,陈晓培.一种900V JTE结构VDMOS终端设计[J].微电子学与计算机,2016,33(4):129-132.SHI Cunming,FENG Quanyuan,CHEN Xiaopei.A 900V JTE structure VDMOS terminal design[J].Microelectronics&Computer,2016,33(4):129-132.

[8]陈龙.功率VDMOS物理结构与特性的研究与建模[D].南京:东南大学,2006.CHEN Long.Research and modeling of physical structure and characteristics of power VDMOS[D].Nanjing:Southeast university,2006.

[9]胡佳贤,韩雁,张世峰,等.高压VDMOS结终端技术研究[C]//2010’全国半导体器件技术研讨会论文集.2010.HU Jiaxian,HAN Yan,ZHANG Shifeng,et al.Resarch on Junction Termination TechniqueforVDMOSFET[C]//2010’national semiconductor device technology seminar.2010.