一种用于FPGA的片上可配置SRAM设计

2018-05-25王文,曹靓,王栋

王 文,曹 靓,王 栋

(中国电子科技集团公司第五十八研究所,江苏无锡 214072)

1 引言

FPGA能够为用户提供大量高性能可编程资源,支持灵活的现场可编程能力。因为其集成度高、灵活性高、开发周期短、可靠性高等特性,在电子系统领域得到越来越广泛的应用,成为电子系统中的一个关键器件。在FPGA电路中,为了实现数据的快速存取,需要采用片上SRAM来满足数据的存储需要,同时提高数据访问的效率。

传统的SRAM设计以及各个工艺厂提供的SRAM IP,都是定制化的SRAM存储器。其数据位宽、存储数据的数量都是固定的。FPGA作为通用的可编程器件,应用于各种不同数据、信号处理领域,可能需要存储不同位宽和不同数量的数据,所以传统的SRAM设计难以满足FPGA高灵活性的需求,无法在各种不同的应用需求下保持较高的资源利用率。本文提出了一种用于FPGA的片上可配置SRAM存储器设计,可以根据用户的需要自主配置SRAM的数据位宽和存储容量,从而提高存储器资源的利用效率。

2 电路设计

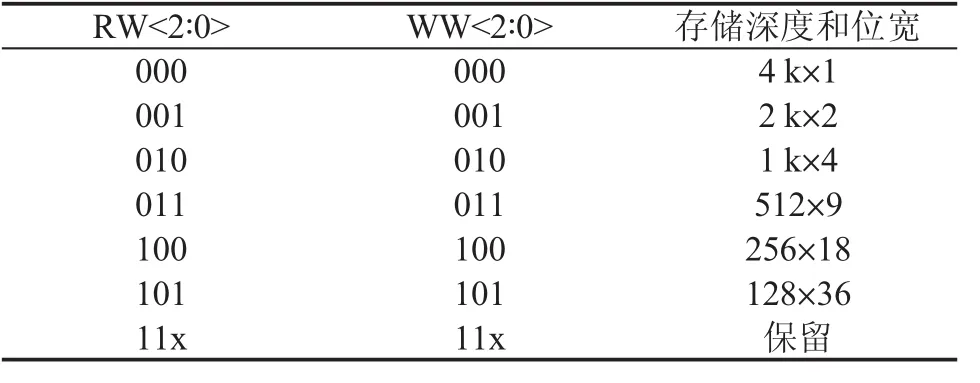

根据FPGA设计的需要,设计的可配置SRAM总容量为4608 Bits。在实际使用时可以通过配置分别实现 128×36、256×18、512×9、1 k×4、2 k×2、4 k×1 共 6 种存储方式。设计的可配置SRAM为双端口存储器,具有一个读端口和一个写端口。2个端口完全独立,可以同时对存储器进行访问,同时两个端口的配置模式完全独立,根据实际需要和配置可以实现不同的写入数据位宽和读出数据位宽。写端口和读端口数据位宽的配置通过WW<2∶0>和RW<2∶0>来进行控制。位宽配置如表1所示。

表1 RW、WW值和配置结果

可配置SRAM中,不同位宽、不同存储容量的控制由RW和WW来配置,具体分别由写控制电路和读控制电路来实现,写电路根据位宽配置和地址信号控制对应的数据写入存储阵列中,读出电路读出数据后控制选择对应位宽和地址的数据输出。

2.1 存储单元设计

传统的SRAM设计一般采用6个晶体管构成的6T SRAM单元,电路结构如图1所示。传统的SRAM单元以6T SRAM单元为核心结构,包括2个互相耦合的反相器以及2个访问管。写访问时,两根位线BL和BLN根据写入的数据分别驱动到VDD或者GND,访问管的控制信号WL字线跳变到高电平,访问管被打开,存储节点Q和QN通过写访问管被拉到位线BL/BLN的电平,数据被写入存储单元中。读访问时两根位线BL和BLN都被预充到VDD。字线WL被驱动到VDD电平,打开访问管。当Q存储低电平时,BL的电平通过访问管下拉,和BLN之间形成电压差,通过灵敏放大器读出。图1所示的6T SRAM单元是一种比率特性的单元结构,晶体管的读稳定性、写稳定性和静态噪声容限受到单元中晶体管尺寸比率的极大限制[1-2]。

图1 传统的6T SRAM单元结构

6T SRAM单元结构中,读稳定性和写稳定性对SRAM单元期间尺寸比率的要求相互冲突,导致单元在低压和先进工艺中难以实现良好的稳定性[3-4]。

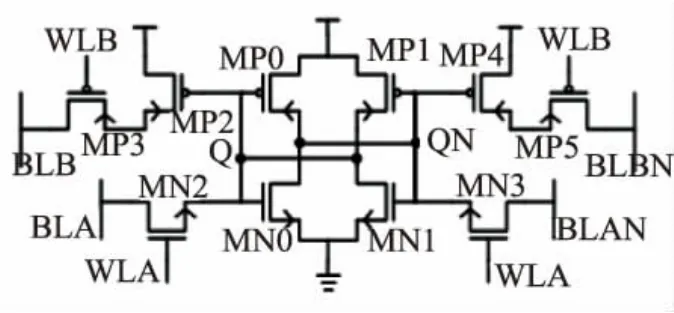

为了便于在不同数据位宽下能够灵活控制写入的数据,在可配置SRAM中设计了如图2所示的SRAM存储单元。

图2 可配置SRAM的存储单元电路

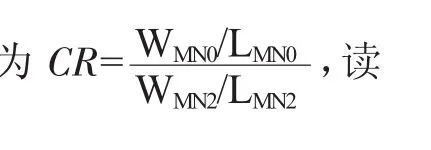

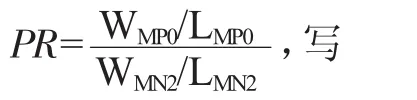

当存储单元中存储数据1,Q节点存储VDD电平,QN节点存储GND电平,写字线WLA被驱动到高电平,打开写访问管MN2和MN3;写位线BLA/BLAN被驱动到VDD/VDD,写位线BLAN通过写访问管MN3将对QN节点充电,将QN电平上拉。由于BLA为VDD电平,所以Q节点电平VDD保持不变。Q点高电平使得下拉管MN0导通,对QN节点放电,将QN节点电平下拉。从图2和表2中的晶体管尺寸可知,下拉管MN0的尺寸要大于写访问管MN3的尺寸。所以,QN一直保持较低的电平,不会发生翻转。在写操作结束后,访问管MN2/MN3关闭,QN的电平恢复到GND,存储单元的数据保持不变。

表2 可配置SRAM单元器件尺寸

图2所示的存储单元在SMIC 0.15 μm工艺下,设计的晶体管尺寸如表2所示。经过特定设计,该存储单元具有2个重要的特性。

(1)写访问中,当BLA/BLAN都为VDD时,可以保证存储单元中的数据不发生改变。当存储单元中存储数据1,Q点为VDD电平,QN点为GND电平。WLA被驱动到VDD,2个写访问管打开,BLA/BLAN=VDD/VDD。写位线BLAN通过写访问管MN3对QN节点充电,将QN的电平向上拉。但是由于BLA电平为VDD,使得Q点的电平保持VDD。下拉管MN0导通,将QN节点电压下拉。由于下拉管MN0的尺寸和驱动能力要强于访问管MN3,使得QN节点保持在低电平。在结束写访问后,2个访问管MN2/MN3关闭,QN节点恢复到GND电平。存储单元中存储的数据保持不变。

(2)采用图2中所示的2个PMOS管的读出访问结构,在读出操作时BLB/BLBN上的充放电不影响存储节点Q和QN的电平状态,存储单元可以保持理想的读稳定性,且不受晶体管尺寸的影响。所以,该存储单元结构不存在读稳定性和写稳定性的冲突,可以将写访问管的尺寸减小,获得良好的写稳定性[3-4],如图2所示。同时,由于读访问电路不影响存储单元的稳定性,所以设计的读访问电路的器件尺寸较大,可实现高的访问速度。

2.2 写控制电路

写控制电路由 WW<2∶0> 和 WA<4∶0> 来实现对数据位宽和存储深度的控制。可配置SRAM中由写控制电路实现对写数据的选择,实现写入不同位宽的数据到存储器中,同时根据位宽调整SRAM的深度。SRAM中最大的数据位宽为36 Bit,所以设计了36个写驱动电路,可以最多一次写入36 Bit数据。写驱动电路如图3所示。每一个写驱动电路输入6个数据,分别对应6种不同的数据位宽,根据数据位宽选择其中之一。同时写驱动电路包括一个使能信号wrOE进行控制,wrOE为0时,所有4组位线对全部驱动到VDD/VDD。写驱动电路输出4组位线对,有4选1的列选择信号进行选择。没被选中的列的BLA/BLAN被驱动到VDD/VDD,因而写操作时不改变存储单元的数据。

图3 写驱动电路

6种数据位宽的指示控制信号wriWidCon<5∶0>由配置信号WW<2∶0>译码产生,写驱动电路的使能信号wrOE<35∶0>由位宽指示信号和写地址 WA<4∶0>控制产生,如图4所示。存储器用WW<2∶0>来配置数据位宽,同时用WA<4∶0>来实现对存储深度的扩展。当 WW<2∶0>=3’b010 时,数据位宽为 9 Bit,WA<4∶3>有效,控制将存储器的存储深度从128个扩展为512个数据。WW<2∶0>=3’b011 时,数据位宽为 1 Bit,WW<4∶0>将存储深度扩展为4 k个,可以独立写入4 k个1 Bit数据到存储阵列中。存储器控制器根据配置提供相应位宽的写入数据。

图4 写位宽控制电路

2.3 读控制电路

SRAM的读控制电路包括36个灵敏放大器电路,每个读访问读出36 Bit数据。读出的36 Bit数据由读位宽控制电路根据读位宽RW<2∶0>和地址RA<4∶0>进行选择。其中灵敏放大器基于锁存型灵敏放大器的结构[5-6],实现高速度和高的判断准确率。在典型的锁存灵敏放大器结构上进行改进,增加了对读位线的选择部分,如图5所示。

图5 锁存型灵敏放大器电路

每个灵敏放大器实现对4对读位线检测数据,由列选择信号选择一对读位线传输到锁存型灵敏放大器的输入端。灵敏放大器使能信号OE1和OE2都被驱动到GND时,读位线对上的电压差传输到交叉耦合的反相器的输入端,被放大到逻辑电平,读出数据。数据读出后,由位宽控制电路进行数据输出选择,电路如图6所示的36-9 Bit读位宽控制电路和图7所示的4-1 Bit读位宽控制电路两个部分。其中36-9 Bit位宽控制电路每4个灵敏放大器对应1个,总共9个,实现输出36 Bit、2个18 Bit或4个9 Bit数据的输出。

图6所示的1个36-9 Bit读位宽控制电路包括4级。第一级根据位宽配置和地址RA<4∶0>实现输出4 Bit数据,2种2 Bit数据,4种1 Bit数据,总共实现7种不同的数据输出。第二级,MUX数据选择实现Pipeline模式和Flowthough模式两种读出模式的选择。数据经过DFF寄存则为Pipeline流水线模式,数据增加一级时钟延时,但相对读时钟的延时小,适合于高速系统。数据不经过DFF寄存,则实现Flowthough模式,数据直接输出,总读出延时小。第三级,根据读位宽配置,锁存输出数据或者输出高阻。第四级电路,选择1 Bit数据输出。输出的9 Bit数据中低8位提供给后面的4-1 Bit位宽控制电路。

图6 36-9 Bit读位宽控制电路

图7 4-1 Bit读位宽控制电路

图7 所示的4-1 Bit读出数据位宽控制电路,将8个输入数据根据读位宽配置,控制输出2个4 Bit、4个2 Bit或8个1 Bit输出数据。最后,存储器控制器读出相应位宽的数据。

可配置SRAM根据配置,可实现6种写位宽和6种读位宽。根据可配置SRAM的电路设计,6种位宽对应的数据位如表3所示。

表3 数据位宽和对应的数据位

当写位宽和读位宽相同时,对应的写入数据位和读出数据位也相同,固定为特定的数据位。存储器的控制器根据数据位宽的配置以及表3中的数据位,写操作时对写数据总线的特定位传输数据,读操作时读取读数据总线的特定位。

当位宽小于36 Bit时,则需要利用WA<4∶0>和RA<4∶0>来进一步控制数据的地址。如读取9 Bit数据中的2个4 Bit数据,则需要RA<2>来进一步选择。

3 仿真验证

在SMIC 0.15 μm工艺下,对设计的片上可配置SRAM进行仿真验证,利用Hsim进行仿真。将写数据配置为 9 Bit数据位宽,WW<2∶0>=3’b011。读出时,先按照9 Bit数据位宽进行读出,然后按照4 Bit进行读出,分别读出2个4 Bit数据,片上数据输出端加负载0.5 pF。仿真结果如图8~10所示。

图8 写位宽控制和写电路使能仿真结果

图9 读操作灵敏放大器控制信号和输出

如图8所示为写位宽控制信号和对36个写电路的使能信号。WW<2∶0>=3’b011,位宽控制为第四种,wriWid<5∶0>=6’h08,9 Bit写数据位宽。wrOE<35∶0>控制在36个写电路中选择开启9个写电路,高电平有效。

如图9所示为读出灵敏放大器的控制信号和输出。在读时钟信号reCLK上升沿时,读译码使能信号和灵敏放大器开启信号产生一个上升脉冲信号。读字线驱动到GND电平,打开存储单元,对读位线充电。在灵敏放大器开启信号Read_A的高脉冲期间,对读位线BL/BLN的电压差状态进行读出,输出有效的逻辑数据。

图10 读写数据仿真结果

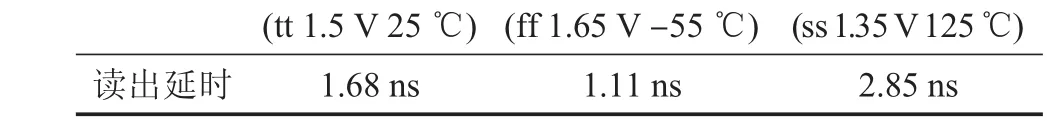

图10中的仿真结果显示,先写入9 Bit数据,然后对相同的地址读出4 Bit数据,分别读出2个4 Bit。其中9 Bit数据的最高位无法读出。仿真结果显示,读出的2个4 Bit数据即为9 Bit数据中的低8 Bit数据。直通模式读访问,在SMIC 150 nm工艺下,输出片上负载500 fF读出数据的延时如表4所示。

表4 片上可配置SRAM读出延时

传统的SRAM中,36 Bit位宽的结构即使是采用字节写特殊功能,也最多能实现36 Bit、18 Bit和9 Bit的数据位宽。当需要存储和访问4 Bit数据时,存储器中存储资源的有效利用率为44.4%。存储和访问2 Bit数据时存储资源的有效利用率为22.2%,难以满足FPGA适应各种不同需求的灵活性要求。

而可配置SRAM中,如表2所示,当位宽为36 Bit、18 Bit和9 Bit时,存储器的总容量为4608 Bit,当位宽为4 Bit、2 Bit和1 Bit时,存储器的总容量为4096 Bit。此时,存储器中存储资源的有效利用率为88.9%。

4 结论

针对传统SRAM结构难以满足FPGA适应各种不同数据位宽应用需求的问题,我们设计了一种用于FPGA的可配置SRAM存储器,可以根据用户实际使用的需要,对SRAM的数据位宽进行配置,同时自动调整存储器存储的深度,在低数据位宽时能够存储更多的数据,在各种位宽配置下都能保证存储资源的有效利用率在88.9%以上。仿真结果表明,存储器能够实现对位宽的配置,可以实现写入位宽和读出位宽独立配置。在SMIC 0.15 μm工艺、TT工艺角下,存储器直通模式下读出延时为1.67 ns,实现了很高的访问速度。

参考文献:

[1]Cheng W,Chung Y.Bit-area efficient embedded pseudo-SRAM utilizing dual-threshold hybrid 2T gain cell[J].IET Circuits,Devices&Systems,2014,8(2)∶107-117.

[2]Andrei Pavlov.CMOS SRAM Circuit Design and Parametric Test in Nano-Scale Technologies[M].Springer,2008∶13-21.

[3]Lin S,Kim Y B,Lombardi F.Design and Analysis of a 32 nm PVT Tolerant CMOS SRAM Cell for Low Leakage and High Stability[J].INTEGRATION,the VLSI Journal,2010,43(2)∶176-187.

[4]Andrei Pavlov.Design and Test of Embedded SRAMs[D].Thesis of PhD.University of Waterloo,Ontario,Canada,2005.

[5]Wicht B,Nirshl T,Schmitt-Landsiedel D.Yield and Optimization of a Latch-Type Voltage Sense Amplifer[J].IEEE Journal of Solid-State Circuits,2004,39(7)∶1148-1158.

[6]Wicht B,Nirshl T,Schmitt-Landsiedel D.A Yield-Optimized Latch-Type SRAM Sense Amplifer.In∶Solid-State Circuits Conference[C].2003,ESSCIRC’03.Proceedings of the 29thEuropean,IEEE,2003∶409-412.