一种高效的熔丝并行修调方案

2018-05-25吴熙文

吴熙文

(中国电子科技集团公司第五十八研究所,江苏无锡 214035)

1 引言

熔丝是集成电路生产中所使用的一项重要技术。在圆片测试时,通过熔丝技术可以根据每颗电路的实际基准值将其在一定范围内进行修调,即按照实测值与设计要求的目标值的差异熔断所需的熔丝,使出厂电路的基准值更加接近设计要求的目标值,一致性更好。随着熔丝技术在电路设计中的应用普及,当前产品对于参数精度的要求越来越高,需要修调的铝条数目也越来越多。电源类芯片的铝条数通常设计有10段以上,尤其在多工位测试越来越普遍的情况下,熔丝修调的时间成倍增长,传统的串行修调方案中熔丝修调时间通常会占总测试时间(总测试时间包括参数测试时间、熔丝修调时间和探针台走步时间)的50%以上。因此,优化熔丝修调时间可大幅提升测试效率,节约生产成本。

2 并行修调方案的原理与效率提升

2.1 串行修调方案

传统的修调方案一般采取串行逐段修调,即按照工位数逐工位逐段熔断需要修调的熔丝段。假设某产品参数测试时间为500 ms,探针台走步时间为500 ms,共设计有20段对地熔丝,修调每段熔丝的时间为30 ms。因为每颗电路的实际基准值不同,所以所需修调的熔丝段也不同,假设平均每颗电路有10段不同的熔丝需要熔断,那么8工位测试时需要的总熔丝修调时间就已经达到2400 ms,占用了测试总时间的70%。按照此方案计算,8工位测试平均每颗电路的总测试时间为(500+2400+500)/8=425 ms,而单工位测试的总测试时间为1300 ms,8工位测试仅提升了3倍左右的测试效率,多工位测试所带来的效率提升被大幅减小了。

2.2 并行修调方案

最初的并行修调方案为同时熔断同一工位所有需要熔断的熔丝[1]。这种修调方案相对于串行修调方案在效率上有明显提升,但存在一些缺陷。由于不同产品的熔丝材料不同,熔断所需的能量也相差甚远,对于需要使用较大能量去修调的产品来说,这种方案存在熔丝修调不彻底的风险,容易产生熔丝熔断后基准值的变化量与理论值有差异的情况,导致产品良率损失;对于熔丝设计为PAD之间的产品该方案无法适用,例如需要同时熔断B1与B2之间、B2与B3之间、B3与B4之间的熔丝时,无法使用该方案形成修调回路。

优化后的并行修调方案原理为同时熔断不同工位的同一段熔丝。由于各工位修调用的源是相互独立的,因此不存在同时修调能量不足的情况,同时该方案也能适用于熔丝设计为PAD之间的产品。该并行修调方案相对于串行修调在效率上有大幅提升,以上文提及的产品为例,将20段熔丝编号,记为B0~B19。在修调时,根据每颗电路所需熔断的熔丝段,通过切换不同的继电器开关控制的方式,将不同工位编号相同的熔丝段同时熔断,该方案最多仅需要进行20次熔丝修调,即可满足所有工位的熔丝修调需求。按照并行修调方案计算,8工位测试时,熔丝修调时间为600ms,平均每颗电路的总测试时间为(500+600+500)/8=200 ms,相对于单工位提升了6倍以上的测试效率。

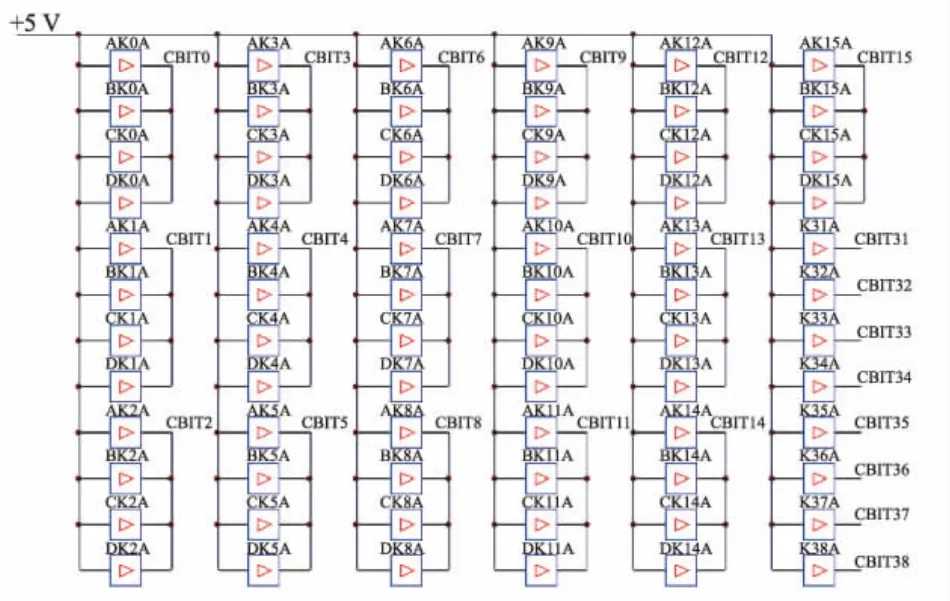

图1 并行修调方案原理图

受图片篇幅限制,图1为前4个工位前8段熔丝的原理图,后4个工位以及后12段熔丝的连接方式以此类推。图中K31B、K32B、K33B、K34B分别为前4个工位的熔丝总开关,闭合后可开启相应工位的熔丝修调;AK0B、AK0C为一组双刀双掷继电器,控制前两个工位B0段熔丝是否修调,该继电器与BK0B、BK0C共用继电器控制位K0,即同时闭合同时关断,其余双刀双掷继电器的连接方式和作用依此类推;B0_S1表示第一工位的B0段熔丝,B0_S2表示第二工位的B0段熔丝,其余熔丝名称标示依此类推;DVI0_F、DVI1_F、DVI2_F、DVI3_F 为前 4 工位的电压源,提供修调所需的能量。

由于该产品设计的熔丝数较多,如果每个工位的每段熔丝都分配一个继电器控制位控制其熔断与否,则8工位测试仅修调部分就共需要160个控制位,再加上控制外围测试线路所必需的若干继电器控制位,常用的测试机是无法满足的,且占用的继电器控制位越多越不利于生产维护和异常处理。为了满足8工位测试,节省继电器控制位的使用数量,采用了双刀双掷继电器,并且将继电器控制位复用(如图2所示),即所有工位相同编号的熔丝采用同一个继电器控制位控制,每个工位增加一个总开关控制该工位的当前熔丝段是否需要修调。例如,当需要同时熔断第一、第三工位的B0段熔丝且其余工位的B0段熔丝不能熔断时,则将K0、K31、K33闭合后再将DVI源上电即可。按照此连接方式计算,8工位测试的修调部分仅需要28个继电器控制位,并且测试时间不受影响。

图2 继电器控制位复用连接图

该方案提出后,首先针对品名为S0XX的芯片进行验证,该产品工位数较多、熔丝段数较少,相对适合验证方案的可行性。S0XX共7段熔丝,原修调方案为电容充放电串行修调,8工位测试。改为并行修调后,该产品单片的测试时间由优化前的100 min/片缩减至60 min/片,效率提升40%左右,且未出现熔丝误烧、漏烧、烧不彻底等质量问题,新程序交接生产后已量产十余批次。

可行性验证成功后,又将熔丝并行修调方案应用到熔丝参数更多、熔丝段数更多的OB23XX中去以验证方案的可靠性。该产品有5个参数需要修调,总共15段熔丝,同样未出现熔丝误烧或漏烧的现象,8工位测试效率提升可达50%左右。

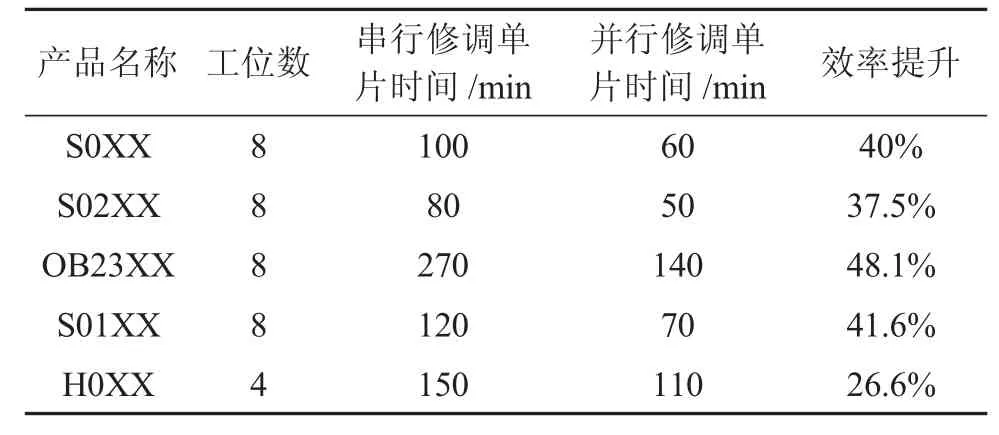

到目前为止,共有3个老品、2个新品采用熔丝并行修调方案(如表1中所示),涉及电源管理、LED驱动等多种类芯片,效率提升根据产品的SITE数、所需要熔断的熔丝数以及熔丝修调时间占总测试时间的比例不同略有浮动,大约在30%~50%。

表1 熔丝并行修调方案单片效率提升对比

以下为部分熔丝并行修调程序代码,该段代码对芯片的Ton参数进行修调,共有B0、B15两段熔丝会影响Ton参数的变化。

void TRIM_TON()

{

int B0[8]={0},B15[8]={0},TRIMN[8]={0},i=0;

int a=100,b=100,c=100,d=100,e=100,f=100,g=100,h=100; //定义8个标志位,控制每个工位的总开关

for(i=0;i<8;i++)

{

if(TH[i]>=5.973&&TH[i]<6.853){B0[i]=0;B15[i]=1;}

if(TH[i]>=6.853&&TH[i]<7.900){B0[i]=0;B15[i]=0;}

if(TH[i]>=7.900&&TH[i]<8.991){B0[i]=1;B15[i]=1;}

if(TH[i]>=8.991&&TH[i]<9.731){B0[i]=1;B15[i]=0;} //TH[i]为每个工位Ton参数的实测值,查表确认每个工位B0、B15是否需要熔断,如需熔断则置1

TRIMN[i]=B0[i]*10+B15[i];

pSite->RealData[i]=TRIMN[i]; //以二进制表示B0、B15的熔断情况

}

AdToPparam(0,0,1.0);

if(TrimEn==1)

{

DVI_SetMode(CH0,FV,VRang_20V,IRang_1A,990,-990);//设置电源为电压源模式

DelaymS(2);

a=100;b=100;c=100;d=100;e=100;f=100;

g=100;h=100;//k100未使用,作为总开关关断标志

if(B0[0]==1||B0[1]==1||B0[2]==1||B0[3]==1||B0[4]==1||B0[5]==1||B0[6]==1||B0[7]==1)

//修调B0前进行判断,如8个工位的B0段熔丝均不需要修调,则跳过该步骤

{

if(B0[0]==1){a=31;}

if(B0[1]==1){b=32;}

if(B0[2]==1){c=33;}

if(B0[3]==1){d=34;}

if(B0[4]==1){e=35;}

if(B0[5]==1){f=36;}

if(B0[6]==1){g=37;}

if(B0[7]==1){h=38;} //根据每个工位B0段是否需要熔断,选择该工位的总开关是否开启CBIT_SRelayOn (a,b,c,d,e,f,g,h,0,-1);//同时闭合需要熔断B0的工位的总开关,以及k0

DelaymS(2);

DVI_SetOutVal(CH0,5); //电压源加5 V,进行熔丝修调

DelaymS(25); //修调等待延时

CBIT_SRelayOn(-1); //继电器复位,所有继电器断开

DelaymS(2);

DVI_SetOutVal(CH0,0); //电压源复位

}

a=100;b=100;c=100;d=100;e=100;f=100;g=100;h=100;//所有工位的标志位复位

if(B15[0]==1||B15[1]==1||B15[2]==1||B15[3]==1||B15[4]==1||B15[5]==1||B15[6]==1||B15[7]==1)

{

if(B15[0]==1){a=31;}

if(B15[1]==1){b=32;}

if(B15[2]==1){c=33;}

if(B15[3]==1){d=34;}

if(B15[4]==1){e=35;}

if(B15[5]==1){f=36;}

if(B15[6]==1){g=37;}

if(B15[7]==1){h=38;}

CBIT_SRelayOn(a,b,c,d,e,f,g,h,15,-1);

DelaymS(2);

DVI_SetOutVal(CH0,5);

DelaymS(25);

CBIT_SRelayOn(-1);

DelaymS(2);

DVI_SetOutVal(CH0,0);

}

DVI_SetOutVal(CH0,0);

CBIT_SRelayOn(-1);

}

}

3 总结

该种熔丝并行修调方案相对于传统的串行修调可大幅提升测试效率,且工位数越多、熔丝数量越多提升的效率越高。熔丝并行修调方案可行、可靠、稳定,且效率提升明显,后续多工位熔丝修调类产品均可采用该方案进行修调,可以直接将该方案运用到新品开发设计中去,已有大量老品也可参考该方案来优化测试时间,提升测试效率,降低成本消耗,提升公司竞争力。

参考文献:

[1]张鹏辉,王己钢.熔丝类电路的修调探索[J].电子与封装,2010,10(4).