FPGA测试压缩技术研究

2018-05-25解维坤肖艳梅

解维坤,陈 龙,黄 晋,肖艳梅

(1.中国电子科技集团公司第五十八研究所,江苏无锡 214035;2.江南大学物联网工程学院,江苏无锡 214122)

1 概述

现场可编程门阵列(FPGA)已成为当前电子系统中普遍采用的核心数字芯片之一。超大容量的FPGA产品在新一代主流系统中的使用越来越多,其质量及可靠性要求越来越高,对FPGA测试的需求越来越大。随着FPGA的规模发展到千万门级甚至是亿门级,配置码越来越大,一段配置码可高达数百兆,完成一款FPGA测试往往需要成百上千段配置码,测试数据量非常庞大。

数量巨大的测试向量会带来很多问题。首先,测试系统需要非常大的向量深度来存储这些向量;其次,FPGA配制过程所占的时间比重越来越大,造成测试成本急剧增加。FPGA测试压缩技术能够有效地减少测试数据量,也能够降低对测试系统向量深度和数据传输通道的需求,还可以减少测试时间,降低测试功耗,提高测试效率。

目前,测试压缩技术主要集中在大规模数字集成电路的ATPG压缩编码算法和可测性设计方面,如文献[1]~[7]介绍了一些测试激励和测试响应压缩编码算法以及SOC的内建自测试(BIST)测试压缩结构等,这些测试压缩方法都需要在待测芯片内部增加解压缩电路。本文主要从FPGA的配置码流生成和配置加载方面研究FPGA的测试压缩方法,不需要在芯片内部增加解压缩电路[1-7]。

2 压缩测试原理

压缩测试可以有效地减少数字电路测试向量体积和测试时间,从而降低芯片的测试成本。传统的测试压缩思路如下:测试激励向量经压缩后,通过测试设备传送到芯片的解码电路;解码电路解码还原出原始测试向量,施加到待测电路完成测试;测试响应再通过响应压缩电路压缩后传送到自动测试设备上完成比较。测试压缩体系结构原理如图1所示[1]。

图1 测试压缩体系结构原理图

测试数据包括测试激励和测试响应,因此测试数据的压缩技术也分为测试激励压缩和测试响应压缩两大类。测试激励压缩包含基于编码、广播式、逻辑变换等方法。测试响应压缩根据压缩电路特性的不同可有多种分类,如空间压缩与时间压缩、电路相关压缩与电路无关压缩、线性与非线性压缩以及组合压缩与时序压缩等。

不同于一般数字集成电路,FPGA的测试需要先进行配置然后再测试,对FPGA进行完整测试需要经过反复多次“配置-测试”过程,FPGA的测试时间主要发生在配置上。随着FPGA规模的增大,FPGA内部集成多种IP,想要完成全部覆盖的测试需要越来越多的测试用例,缩短配置时间可以有效提高整个测试效率。配置时间的长短主要由配置下载频率和配置位流大小决定,在配置频率固定的情况下,减少配置位流大小可以有效缩短配置时间。FPGA的测试压缩方法主要从配置位流压缩和加载角度开展研究。

3 FPGA配置原理

FPGA的配置过程是将FPGA设计软件生成的位流文件下载到FPGA中的过程,配置时间的长短由配置速度和位流文件大小决定。

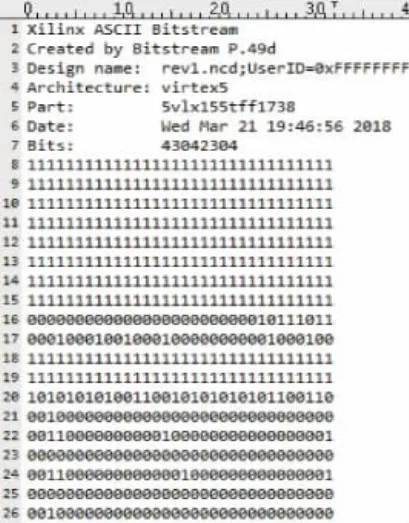

位流是表示FPGA配置信息的一种形式,是由FPGA开发软件根据设计生成的配置信息。位流以32位的二进制数表示一个字,41个字组成一帧数据。位流以位流文件形式下载到FPGA中,位流文件是位流生成器生成的一种ACSII编码格式的文件,由文件头、数据帧以及文件尾构成,其结构如图2所示。图2中TYPE000代表互连和BLOCK配置信息,TYPE001代表BRAM初始化内容。位流文件样式如图3所示。

图2 位流文件构成

图3 位流文件样式

配置过程是通过帧地址来写入帧数据,每一个帧地址都对应一帧数据。正常配置模式是根据器件BLOCK的顺序连续写入帧数据,在开头的部分直接指定要写入字的个数,从帧地址0开始按照帧地址顺序,遍历完成整个芯片的配置过程,配置顺序如图4所示,先写Type000,后写Type001,在每一个Type中先写上半部分,后写下半部分,然后按行写入帧数据。

图4 配置流程图

4 FPGA位流压缩方法

在FPGA配置时钟频率固定的情况下,可以通过减少配置位流文件的大小来提高配置速度。传统FPGA的配置是根据帧地址顺序配置的,配置位流文件大小由芯片规模决定。本文所述位流压缩算法,提出一种多帧写位流压缩方式,通过统计FPGA中帧内容相同的帧放在一起进行配置,帧内容相同的帧中先以普通模式配置第一帧,随后以压缩模式配置剩余帧。这种压缩方式的压缩比通常可以达到80%以上,可以有效缩小配置位流文件大小,提高配置速度,并且不需要在芯片内部实现解压缩电路。

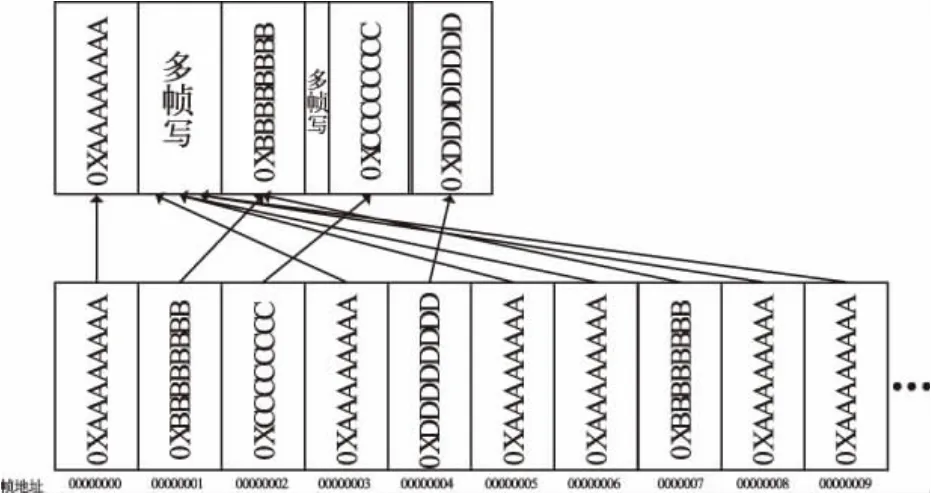

多帧写的原理是以行为单位,统计一行中配置帧数据相同的帧,将这些帧内容相同的帧放在一起配置,而不是严格按照帧地址顺序配置。位流压缩的原理如图5所示,图中所示帧地址和帧数据只是为了便于显示说明,并不代表实际内容。首先正常配置帧内容为0XAAAAAAAA的帧地址00000000,然后以压缩模式配置(多帧写)该行剩余所有帧内容为0XAAAAAAAA的帧地址。相对于正常配置每帧需要配置41个字,压缩模式除了首次配置外,剩余为多帧写模式,多帧写模式下每帧写只需要4个字。所以对于一些配置帧内容有比较多相同的用例,可以极大地减小配置文件的大小,缩短配置时间,提高配置速度,从而提高测试效率。

图5 位流压缩原理图

5 基于ATE的测试压缩

FPGA测试压缩还可以从ATE的角度采用X模式(X4/X8)或Multiport方式进行测试压缩,进一步压缩测试向量长度,缩短加载时间,提高测试效率。

5.1 基于ATE的X模式

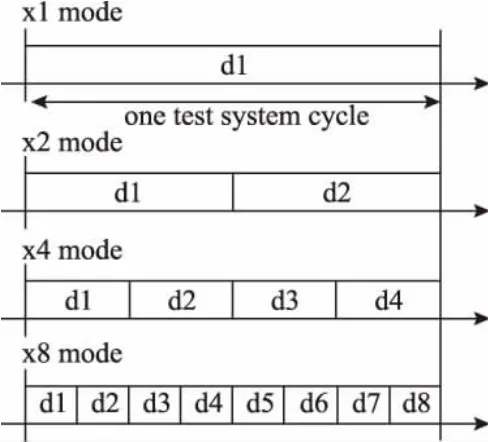

利用ATE加载配置码时,通常是一个周期加载1行(最大32 bit)配置向量,通过Timer X8模式,将8行向量压缩成一行,向量长度压缩了8倍,可以使FPGA配置pattern装载时间大大缩短。图6为ATE的X模式示意图[8]。

图6 基于ATE的X模式示意图

5.2 Multiport方式

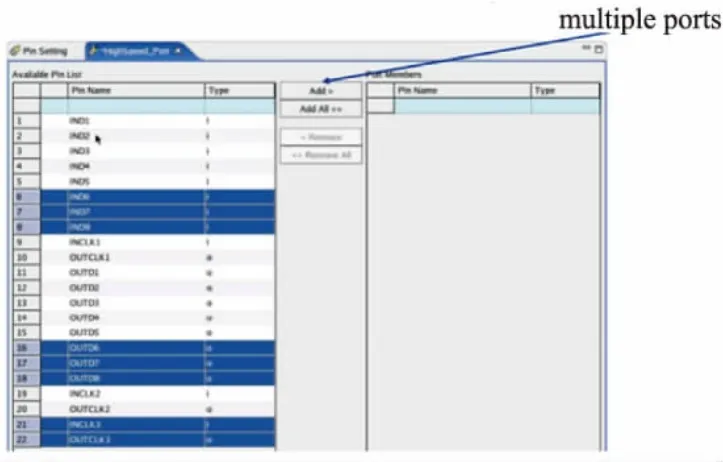

V93000测试加载向量时会将全部定义的管脚进行空间分配,由于FPGA的管脚多(往往高达1000 PIN以上),但配置码只需要用到部分管脚,这样每个配置码的向量大小装载在机器里会自动变大,影响装载和测试速度。通过图7中Multiport(多种管脚分组)的方法可以将需要用到的管脚单独分成一组,进行相应的设置后,装载向量时会关联到单独定义的组,这样向量大小就会大大缩小,明显提高了向量装载和测试速度。

图7 Multiport方法示意图

6 测试实例

为了验证FPGA测试压缩方法的使用效果,本文以Xilinx公司Virtex-5系列FPGA-XC5VLX155T为例进行测试验证。XC5VLX155T是一款典型的千万门级FPGA,系统门数1550万门,封装管脚达到1738 PIN。测试过程中,分别选取一段不压缩和压缩的LVTTL电平模式配置码对XC5VLX155T进行配置时间的测试。

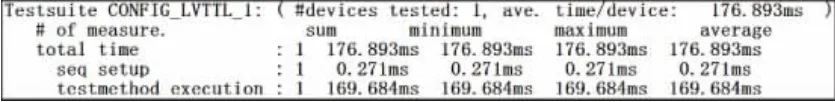

不采用位流压缩、基于ATE的X模式和Multiport方式进行测试时,一段LVTTL配置码的位流长度为43042304位(详见图3第7行bit数),文件大小43 MB左右。利用ATE在系统快速配置方法,采用32位从并模式对电路进行配置,配置时间为176.893 ms。实验数据如图8所示。

图8 不采用压缩实验的数据

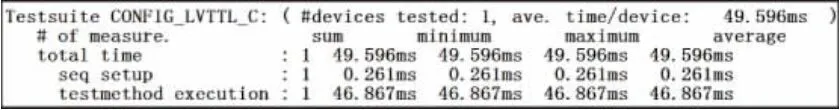

采用位流压缩、基于ATE的X模式和Multiport方式进行测试时,利用ATE在系统快速配置方法,采用32位从并模式对电路进行配置,一段LVTTL配置码的配置时间为49.596 ms,实验数据如图9所示。

图9 采用压缩实验的数据

可见,通过测试压缩仅一段配置码配置时间就缩短了127.297 ms。对FPGA芯片XC5VLX155T进行完整的测试通常需要两百多段配置码,单颗电路测试时间至少可节省25.5 s。另外,若不进行测试压缩,需要占用更多的测试系统向量空间,一个测试程序往往只能加载几十段配置码,两百多段配置码需要多个测试程序,这样便需要多次测试,大大降低了测试效率。FPGA测试压缩可降低对测试系统向量空间的需求,缩短了测试时间,提高了测试效率。

7 结束语

本文主要介绍了压缩测试和FPGA配置原理,并从位流压缩和向量加载角度出发,提出了一些缩短FPGA配置时间和提高测试效率的FPGA测试压缩方法,并分别通过压缩和不压缩方式对Xilinx公司Virtex-5系列FPGA XC5VLX155T进行测试配置验证。实践证明,文中提到的FPGA测试压缩方法可降低对测试系统向量空间的需求,大大缩短FPGA的测试配置时间并提高测试效率,该方法对其他类型数字电路的测试也有一定借鉴作用。

参考文献:

[1]韩银和.数字电路测试压缩方法研究[J].中国科学院研究生院学报,2007:848-849.

[2]韩银和,李晓维.数字电路的测试压缩方法[J].中国计算机学会通讯,2007:47-55.

[3]徐卫林.集成电路测试压缩方法研究[C].全国电工理论与新技术学术年会2007论文集,2007:75-77.

[4]李建新,吴孝银.测试数据编码压缩技术研究[J].宿州学院学报,2010:31-33.

[5]陈田,梁华国.基于优化编码的LFSR重播种测试压缩方案[J].计算机研究与发展,2012,49(2):443-451.

[6]刘娟,詹文法.数据块相容性统计的测试数据压缩方案[J].计算机工程与应用,2013,49(22):26-28.

[7]N Sitchinava,S Samaranayake,R Kapur,E Gizdarski,F C Neuveux,T W Williams.Changing the scan enable during shift[C].In Proceedings of IEEE VLSI Test Symposium,2004∶73-78.

[8]Advantest.Advantest V93000 SOC Basic User Training Rev.7.2.2[P].2014.