基于FPGA与高速AD9144的信号源设计

2018-05-14周希辰张志武翟刚毅李云飞

周希辰,张志武,翟刚毅,李云飞

(1.中国舰船研究院,北京100101;2.中国船舶重工集团公司第七二四研究所,南京 211153)

0 引 言

随着大宽带数据处理应用,数模与模数转换器的分辨率和采样率不断增加。传统的DAC由于其通道集成度低,在实现高采样速率、多通道的信号产生时,其大量的输出管脚导致PCB布局复杂度大大增加。为减少成本,并实现PCB布局的优化,基于JESD204B协议的数据传输接口应用而生[1-4],并大量应用在AD/DA转换器和RF收发器中。最新的JESD204C已经可支持高达32Gbps的数据速率传输。本文利用FPGA的高速收发器实现JESD204B接口并完成与高速DAC的对接。采用FPGA内部的DDS IP核[5],通过基于FPGA DDS IP核+D/A的方式,灵活产生多种宽带高采样率调制信号。另一方面,由于FPGA工作时钟相对于DAC的采样率目前仍然较低,其无法直接用DDS IP核产生符合DAC需求的高采样率大带宽信号,因此本文采用多通道并行DDS合成技术,将多通道DDS信号通过JESD204B接口高速送入DAC,最终产生200 MHz带宽的线性调频信号。

1 原理简述

1.1 多通道宽带DDS工作原理[6-7]

本文利用4通道DDS IP核并行产生信号数据,其实现方式如图1。

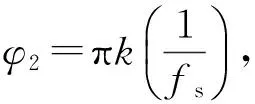

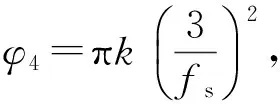

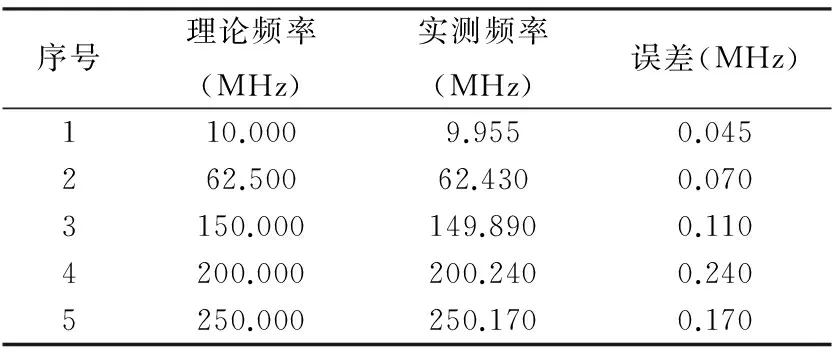

设DDS IP核的时钟为f_clk,信号带宽为B,信号时宽为t_max,调频斜率为K,最终合成信号数据率为fs=4×fclk,信号的数据点n=1,2,3…fs×t_max,其中,通道DDS1的数据点为输出信号的1、5、9…个点,通道DDS2的数据点为输出信号的2、6、10…个点,3、4通道类推。根据单通道DDS原理,对4个DDS通道的初始相位、频率步进进行分析。

DDS1:初始相位码字φ1=0,数据步进码字:

1.2 JESD204B协议简介

JESD204B是一种连接在逻辑器件(FPGA)和转换器(ADC和DAC)之间的高速串行接口[8-9],支持单通道最大传输速率12.5 Gbps。JESD204B协议系统结构大致可分为传输层、链路层和物理层。传输层是收发设备的第1部分,执行转换样本与帧传输、非加扰8位字节之间的映射,发射端旨在把多位样本数据转换成一系列非加扰8位字节,接收端旨在按照发射端的逆过程还原有效数据。链路层实现FPGA与转换器之间的链路初始化,包括实现8B/10B编解码、代码组同步(CGS)、初始通道同步(ILA)以及数据传输。物理层以设置好的线速率接收或发送字符[10]。收发框图如图2。

2 方案设计与实现

2.1 电路设计

本文采用Xilinx的K7C325T FPGA为主控芯片,配置芯片内部集成的DDS IP核、JESD204BIP核以及高速串行收发器GTX,将FPGA产生的数字信号通过JESD204B协议高速传输给AD9144数模转换器,通过低通滤波器最终输出所需模拟信号。系统框图设计如图3。

AD9144是ADI公司最新推出的四通道、16位、高动态数模转换器,主要性能参数如下:

• 支持高达2.8 GSPS的采样速率;

• 灵活可配置的8通道JESD204B接口;

• 可选1x、2x、4x、8x插值滤波器;

• 数字混频器;

• 高性能、低噪声锁相环时钟倍频器。

时钟芯片是ADI公司的AD9523-1,可输出14路最大支持1 GHz的低抖动时钟。本系统中,共输出四路时钟,均为同源时钟,确保收发器件时钟同步。其中一路用作DACCLK,一路用作GTX的参考时钟,两路用作SYSREF同步时钟。

2.2 软件设计

主要基于Vivado 2017.3开发环境下进行逻辑软件开发,包括对时钟芯片AD9523-1、AD9144、DDS IP 核以及JESD204BIP核的参数配置,实现JESD204B协议。

在设计中,将AD9144配置为模式5,即两个转换器(converter)和四链路(lane)模式。通过内置时钟倍频器将DAC采样率配置为2.4 GHz,其中DAC0和DAC1分别用来转换信号的I路和Q路。SERDOUT0和SERDOUT1分别传输通道DAC0的奇数采样信号N/2+1和偶数采样信号N/2,SERDOUT2和SERDOUT3奇数采样信号N/2+1和偶数采样信号N/2。每一个链路上的数据率:

其中,M为转换器数,N为分辨率,L为链路数,Fs为采样率,A为插值滤波器值。当Fs=2.4 GHz、M=2、N=16、L=4、A=4时,每个通道传输数据率为

因此,发射端GTX发射速率为6 Gbps。将FPGA JESD204B IP核配置为发射端,具体参数配置:每帧字节数F=2,多帧数K=32,链路数L=4。GTX核的参考时钟为150 MHz,其线速率:

3 方案验证与分析

信号产生硬件实物图如图4所示。

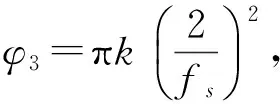

为验证信号输出性能,利用一台安捷伦的DSO9254A示波器和一台R&S的FSV30频谱仪对输出信号的波形及频谱进行测试与分析。对单频信号进行数据分析可知,输出信号误差小,精度较高,如表1所示。

表1 输出频率数据分析

图5、图6分别给出输出150 MHz时的波形图及频谱图。

对线性调频信号进行分析。通过DAC内集成的数字混频器,设计产生中心频率600 MHz、带宽为200 MHz、脉宽10 μs的线性调频信号。测试结果如下图7、图8。从频谱图可以看出,信号在DAC转换器输出后,在带外虽有较小的杂散信号,但带内平坦度较好,信号高质量合成。

4 结束语

本文通过对转换器及JESD204B IP核的参数配置,以数字频率合成技术为基础,基于JESD204B协议,利用FPGA高速收发器GTX,设计实现了基于FPGA和数模转换器DA9144芯片的6Gbps的高速数据传输以及高质量信号合成,并对产生的模拟信号进行测试分析。结果表明,合成信号性能良好,可用于工程中。

参考文献:

[1] 欧阳靖,姚亚峰,霍兴华,谭宇.JESD204B协议中自同步加解扰电路设计与实现[J].电子设计工程,2017,0(7):148-151.

[2] 张峰,王战江.基于JESD204协议的AD采样数据高速串行传输[J].电讯技术,2014,54(2):174-177.

[3] 焦喜香,吴兵,李武建,向海生.基于JESD204B协议的高速雷达数字接收机设计[J].信息通信,2016,0(6):42-44.

[4] 綦睿,罗丰,吴顺君.基于DDS的雷达中频信号源设计与实现[J].火控雷达技术,2006,35(3):47-49.

[5] 黄志林.基于FPGA的并行DDS技术研究[J].现代电子技术,2013,36(7):54-56.

[6] 席安安,张春荣.DDS在复杂信号产生中的应用研究[J].火控雷达技术,2005,34(1):17-19.

[7] 蒋迺倜,江涛,陈建军.并转串换法合成多通道宽带DDS信号[J].雷达与对抗,2009(4):31-34.

[8] 刘安,禹卫东,马小兵,吕志鹏.基于FPGA的高速串行数据收发接口设计[J].电子技术应用,2017,43(6):48-51.

[9] 张金凤,孟爱全,袁子乔.基于JESD204B协议的高速数据传输接口设计与实现[J].火控雷达技术,2011,1(6):16-19.

[10] 田瑞,刘马良.JESD204B协议的高速串行转换器接口[J].西安电子科技大学学报,2017,4(3):69-74.