高速PCB设计中的阻抗匹配与方式研究

2018-04-24吴红芳姚腾飞张建宁

吴红芳,姚腾飞,张建宁

(1.中国航空工业导弹院,河南 洛阳 471009;2.凯迈(洛阳)测控有限公司,河南 洛阳 471009)

在能量传输过程中,最常见是阻抗匹配。进行数据传输的线路阻抗需要在数值上与负载阻抗基本一致,由此在传输过程中阻止反射作用的发生,此时主要由负载吸收产生的一切能量。否则,预示着能量在传输中发生了损失。高速PCB设计工作中,信号的质量好坏直接与阻抗匹配相关。本文以高速PCB设计中存在的阻抗匹配问题为研究对象,研究其阻抗匹配的原理、不同频率的阻抗匹配以及阻抗匹配的方式。

1 阻抗匹配产生

首先,选择直流电压源中负载方面的内容。任意电压器内部都会存在内阻因素,所以在实际工作中常把电压源看作为一个理想的电压源串联一个电阻r的组合样式。电压源的负载电阻定为R,电动势定为U,电源的内阻定为r,在此基础上就可以运算获得电阻R上通过的电流值,即I=U/(R+r)。

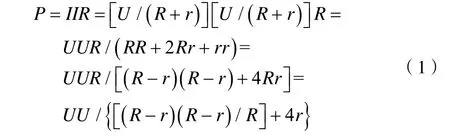

当电源的负载电阻R值变小时,其输出电流变大。负载R上的电压可以表示为UO=IR=U[1+(r/R)]。可以得出,如果负载电阻R变大,那么其输出电压值UO就会变高。那么,电阻R上消耗的功率为[1]:

对于已经给定的信号源,其内阻r是固定的,其负载电阻R可以根据需要自行选择。(R-r)(R-r)/R中,如果R=r,(R-r)(R-r)/R能够获得最小值0,此时负载电阻R获得的最大输出功率为Pmax=UU/(4r)。换句话说,在数值上,如果负载电阻和信号源内阻基本一致,那么在此负载上可以得到最大的输出功率。上述结论在低频电路与高频电路中一样可以应用。然而,在容性或者感性阻抗存在于交流电路中时,阻抗匹配将发生变化,这时的信号源与负载阻抗在实部方面保持一致,但其虚部互为相反数,一般将这样的匹配方式称为共轭匹配。

2 不同频率电路中的阻抗匹配

2.1 低频电路中的阻抗匹配

处于低频电路时,通常不会对传输线互相匹配问题考虑过多,一般只权衡负载和信号源间的实际情况。究其原因,主要表现在线路中的低频信号远远超过了传输线的长度,即传输线相对变成了“短线”,其造成的反射通常不予考虑[2]。因此可以认为,选择数值较小的负载R,可能够获得输出大电流;如果选择较大的负载R,可以得到较大的输出电压。同时,选择与信号源内阻相匹配的电阻R时,可以使输出功率达到最大值。另外,有些仪器输出端的负载为专门的条件设置,假如负载的条件变化,将导致仪器达不到初始性能,称为阻抗失配。

2.2 高频电路中的阻抗匹配

当信号频率很高时,电路的反射问题应该引起重视。高频信号对应的波长较短,如果其传输线长度等于波长,原信号就会与反射信号互相叠加,引发原信号的形变。

假如传输线的特征阻抗与负载阻抗数值上不等,将导致负载端产生反射作用。一般而言,剖析导致PCB阻抗不匹配的影响因素、求解办法,均要求传输线路的特征阻抗是通过解二阶偏微分方程实现。需要指出的是,决定传输线特征阻抗的直接因素是其使用的材料及结构,往往与传输线长度、信号频率等关系不大。家用电视的闭路线输电线的特征阻抗阻值为75 Ω,其他的射频设备同轴线的特征阻抗大多数为50 Ω。先前电视天线架上八木天线的馈线则常采用扁平平行线作为传输线,特征阻抗为300 Ω。

由于馈线特征阻抗阻值为300 Ω,与电视机射频输入端75 Ω的输入阻抗不匹配。为了实现线路匹配,需要在电视机前加入阻抗变换器。阻抗变换器可以以75 Ω替换300 Ω的阻抗,基本能够处理好线路匹配的难题[3]。

特性阻抗与平常所说的电阻概念不同。特性阻抗与传输线的长度无关,因此使用欧姆表无法测量具体的阻值。要尽可能消除反射,那么负载阻抗与传输线的特征阻抗应基本一致,以期达到阻抗匹配的目的。如果阻抗不匹配,线路中会出现反射,使得能量传递不流畅,极大地降低了传输效率,同时也会使功率不能发射,进一步损坏发射设备。

3 阻抗匹配的途径

3.1 终端串联

信号源端的阻抗比传输线特征阻抗低,是串联终端匹配的重要前提。终端串联主要是在信号源端与传输线二者间串联电阻R,实现电源端输出阻抗与传输线特征阻抗的互相匹配。这样可以阻挡负载端反射的信号,进而避免再次发生反射[4]。

至于串联匹配,很小的电流驱动力就可以满足其信号驱动器的要求。在实际设计工作中,经常串联终端匹配电阻值,因为传输线特征阻抗等于匹配电阻值与驱动器输出阻抗的和。理想状态下,信号驱动器输出的阻抗为0。然而,实际输出阻抗一般都会存在且数值较小,同时信号具有电平变化,其输出阻抗也会发生变化。需要注意的是,串联终端匹配在链状拓扑结构的网路中不太适用。短时间内,负载端信号幅度是原始信号幅度的50%左右,这时低信号噪声容限和信号不定逻辑态将较为明显。

3.2 终端并联

信号源端的阻抗保持很小状态时,在负载端并联电阻能够实现输入阻抗与传输线的特征阻抗相匹配,同样可以消除负载端反射。通常,使用单电阻与双电阻并联的形式。当芯片输入的阻抗处于较高状态时,单电阻的负载端所并联的电阻值需要与传输线特征阻抗保持尽可能一致。上述就是匹配电阻选择原则。

终端并联匹配易操作,缺点是无法消除直流功耗。信号占空比与单电阻直流消耗关系密切。高电平、低电平中的双电阻方式都会存在直流功耗,却比单电阻形式减少50%的电流。类似地,SSTL驱动器广泛应用于高速信号,采用单电阻模式,可将其并联于VTT中,而DDR2的数据信号内置于芯片中。单电阻形式也常常在TMDS接口使用较多,如果接收设备端并联IOVDD时,其单端阻抗值为50 Ω[5]。

目前,虽然并联终端匹配容易施行,却会引起直流功耗。在TTL、CMOS系统中,由于单电阻方式没有完全适用于驱动,因此会导致其需要有两个电阻形式。同时,要求有两个元件与之相匹配,这样对PCB的板面积就有了具体要求。因此,在密度较高的印刷电路板中,并联终端匹配是不适合的。

4 高频电路阻抗匹配实例分析

基于SOPC的DDS波形发生器。采用的方案很简单,即FPGA模拟DDS逻辑,然后经过一个DA转换,将来自FPGA的IO口的数字信号转换为模拟量。电路图在IO口和DA数字端都连接了电阻,即进行了PCB的阻抗匹配。

其实,速度快的器件无论频率高低都应该加。反射和上升沿有关,一般走线长度大于上升沿传播距离的1/6就要加。假如信号是100 MHz,而上升沿可能只有1~2 ns(电路板上信号的传播速度并不是光速,而是与介电常数有关,表层微带还与线宽、介质厚度有关,带状5.4 inch/ns,微带7 inch/ns),取20 cm/ns,那么传播距离只有20~40 cm。所以,超过5 cm就应该匹配。

实现阻抗匹配的常用方式有串联、并联电阻。选择串联匹配电阻,一般要求匹配电阻与驱动输出器的阻抗之和等于传输线的特征阻抗。而当电路系统中芯片的输入阻抗很高时,需要使用并联电阻。要求并联的电阻值与传输线特征阻抗基本一致,常使用双电阻模式,如22的或是33的。这是因为在射频领域,传输线通常是50 Ohm的。所以,33 Ohm比较合适。对于数字电路传输线阻抗通常在75~100 Ohm,且可以再大一些。

匹配电阻不仅存在取值问题,而且存在位置问题。如果是串联匹配,要靠近源;如果是并联匹配,要靠近负载。几乎所有器件都是低阻抗输出高阻抗输入,所以一般串连匹配电阻是在源端匹配,并联匹配是对终端匹配。一般,总线采用源端匹配。

5 结 论

阻抗匹配是PCB设计中最常遇到的问题。匹配方式通过变压器实现阻抗的转换、采用串联或者并联电容的手段以及串联或者并联电阻等常用手段。三种阻抗匹配各有适用的范围,因此在具体的设计工作中应认真分析处理。例如,高频电路中的阻抗匹配时,选用串联或者并联匹配。需要注意适用原则,即串联匹配要靠近源,并联匹配则需要靠近负载。

参考文献:

[1] 孙小孟.射频阻抗匹配器的设计与研究[M].昆明:昆明理工大学,2012.

[2] 黄继承,黄继文,彭星波,等.高速电路设计研究[J].通信电源技术,2015,32(6):41-44.

[3] 戴 文,王 芳,刘燕竹.高速数字电路PCB设计中的阻抗控制[J].电子技术应用,2006,32(6):134-136.

[4] 张健楠,鲍 丹,刘婷婷.差分线对在高速PCB设计中的应用[J].电子元器件应用,2011,(1):23-24.

[5] 李 树.无线通信模块PCB电磁兼容性研究[D].北京:华北电力大学,2014.