基于DSP的卷积码通信性能研究

2018-04-09肖雪芳左石凯苏国良雷国伟

肖雪芳,左石凯,苏国良,雷国伟

(1.厦门理工学院光电与通信工程学院,福建 厦门 361024;2.福建省高校光电技术重点实验室,福建 厦门 361024;3.厦门市LED照明应用工程技术中心,福建 厦门 361024;4.集美大学理学院,福建 厦门 361021)

随着当代通信的高速发展,高速率传输以及高可靠性传输被称为信息传输中最重要的两个方面。而在这方面,卷积码都有着非常大的优势。已广泛应用于各类无线通信系统中。卷积码是由伊莱亚斯在1955年提出的一种非分组的连环码[1],具有高结构化的映射关系,由连续的信息序列比特构成,是一种向前纠错型的编码类型[2]。在卷积码中,译码方法有许多种,Viterbi的最大似然译码是迄今为止性能最好的一种译码算法。文献[3-4]在不同类型的数字信号处理(digital signal process,简称DSP)技术芯片上使用Viterbi方法进行卷积码的译码。文献[5-6]在DSP上实现了咬尾卷积码的编译码。文献[7-8]从不同约束长度的角度,讨论在DSP上实现不同卷积码结构的性能。除了上述对卷积码结构的性能比较外,关于卷积码的幸存路径、进制等还需要进行性能比较。

本文分析了不同进制、不同码率下的编码结构,并从译码角度探讨了不同幸存路径下的译码性能,并在TMS320C5509系列平台上搭建卷积码的编译码系统。系统中,对卷积码的码字进行模拟干扰,以便更好地分析比较卷积码的性能。最后通过实验仿真,验证了卷积码在不同编码结构、不同幸存路径、不同进制等条件下译码的性能。

1 卷积码原理

1.1 编码原理

卷积码编码的基本原理是编码器对数据流进行1 bit或kbit编码运算,编码输出n个bit的编码符号。在通常情况下卷积码是用(n,k,m)来表示。其中,n为一个编码器输出的编码标志个数,k表示为输入的信息码元长度,m为连续式输入的寄存器个数。编码率r=k/n。卷积码就是在编码的时候,将kbit的信息编译生成nbit的编码组,这就让编码的产生不单单与当前状态下k比特的信息有关联,还与当时这个信息段的前面m-1个信息有关[1],其中m为编码约束长度。二进制(2,1,3)和四进制(3,1,3)编码器结构如图1所示。图1(a)和图1(b)均由3级移位寄存器组成。其中图1(a)由两个模2加法器和两个输出构成,图1(b)由3个模4加法器和3个输出构成。

(a)二进制(2,1,3)(b)四进制(3,1,3)

图1编码器结构

Fig.1Convolutionalencoder

1.2 译码原理

卷积码的译码方式一般有两种。第一种方式是代数译码[9],第二种方式是概率译码。前者有大数逻辑译码,后者也被称为最大似然译码。维特比(viterbi,VB)译码算法是一种最大似然译码算法,即它对整个信息比特序列译码的差错概率最小。当前应用最多最广的是维特比译码方式,其基本思想是把接收到的矢量,和网格图上诸种可能的路径比较,删去距离大的路径,保留距离小的路径,以距离最小路径作为发码的估值。具体来说,就是在每个单元时间,运算出2L个分叉的度量,加到相对应之前路径上的度量中。然后进行对比2L个度量,找出路径度量中拥有最多的度量路径。像这种结果路径就被叫做幸存路径[10]。经过路径度量相加后比对,找出幸存路径,就是硬判决。而在离散信道中,软判决运用的欧式距离,将可信度最大的作为幸存路径。正常来说软判决的译码结果相对于硬判决的译码结果来说性能会比较好。图2是编码器图1(a)的状态网格图。从图2可以看出,当输入为(1011100)时,输出为(11100001100111),码率为1/2(见加粗标注路径)。

图2 状态网格图Fig. 2 Trellis graph

2 基于DSP的卷积码通信系统与实验步骤

2.1 系统框架

在DSP平台上模拟搭建卷积码通信系统,该实验系统有丰富的硬件资源,如CPU板,E_LAB总线接口、模拟信号源、A/D与D/A转换单元、I/O单元、键盘接口单元、液晶显示单元、JTAG仿真器等。可以完成多种DSP基础实验、算法实验、控制对象实验和编解码通信实验。该DSP平台所选用的DSP芯片为TMS320C5509系列。该卷积码通信系统主要由信源、交织器、编码器、信道、译码器、解交织器、判决等部分组成。

信源模块由rand()函数产生随机小数,再通过round()函数取整后产生0或1的随机数。四进制的随机数产生比较简单,只要将rand()函数产生的随机小数乘以3,然后通过round()函数取整即可得到。交织器是对随机数进行块交织,重新编排其数据顺序。本质上来说就是一种实现最大限度的改变信息结构而不改变信息内容的器件。使信道传输过程中所突发产生集中的错误最大限度的分散化。编码器是对交织后的数据进行卷积码编码。卷积码属于信道编码,它能增强数据在信道中传输时抵御各种干扰的能力,提高信息传输的可靠性。信道模块由rand()函数产生模拟信道噪声。译码器是编码器的逆过程,一般借助状态网格图对数据进行维特比译码。解交织器是对译码数据按原序重排。判决器是将译码结果与源信息数据进行一一核验,统计错误数量。最后计算系统的误码率。

2.2 实验步骤

编码过程:运行CCS3.0软件,新建项目juanji.pjt;然后添加编写好的juanji.c(源文件)、juanji.cmd(cmd文件)、rts.lib(库文件)。该源文件包括信源模块、交织模块、编码模块以及信道模块。模拟信道就是对编码文件bianmazhi.txt添加模拟噪声,生成bianmazhi2.txt文件。

译码过程:新建yima.pjt;然后添加yima.c(源文件)、yima.cmd(cmd文件)、rts.lib(库文件)。该源文件作用是先从c://bianmazhi.txt文件中接收卷积码字,进行维特比译码,结果保存到c://yimajieguojz.txt文件当中,并对数据进行解交织,保存到c://jyimajieguo.txt文件当中去。

最后判决就是取出译码文件c://jyimajieguo.txt与源数据文件c://bianma.txt核对统计误码率。

为了更好地评估卷积码性能,在原有误码率的基础上,引入扰码率的概念,对编码后的卷积码字进行随机干扰,即扰码率=传输中的扰码/所传输的总码数×100%,误码率=译码错误个数/传输数据总数×100%。然后从幸存路径、编码标志数、进制等不同侧面来比较分析其性能。

3 研究结果与分析

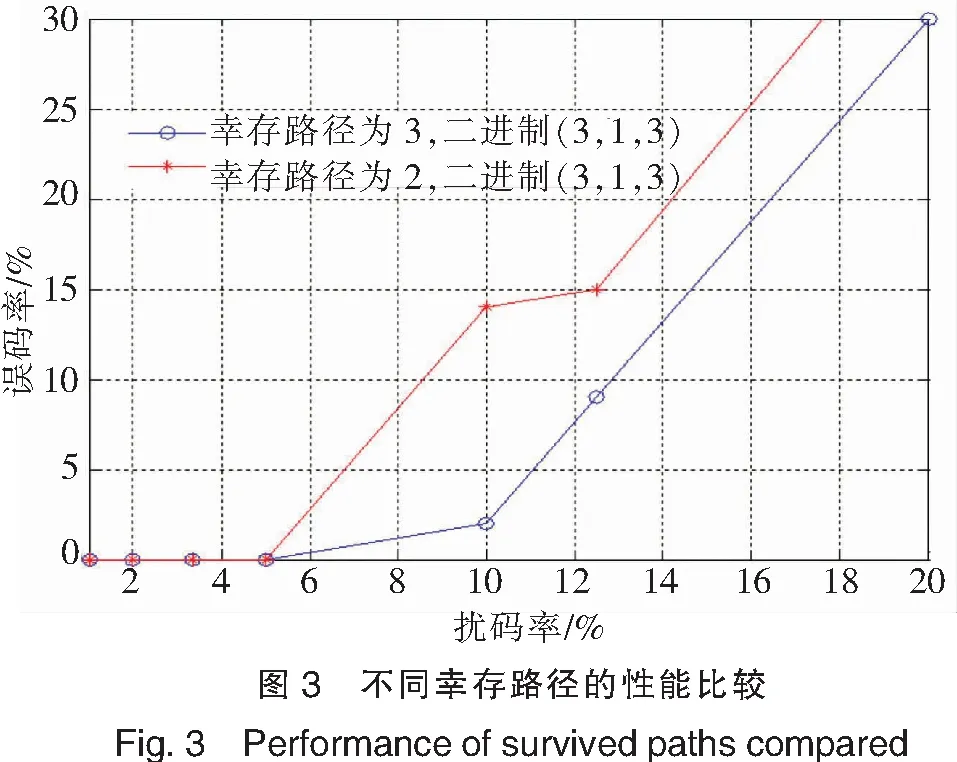

3.1 幸存路径对卷积码的影响

由图3可见,在相同卷积码结构中,幸存路径较大的维特比译码方式的抗噪能力较优于幸存路径较小的译码方式。

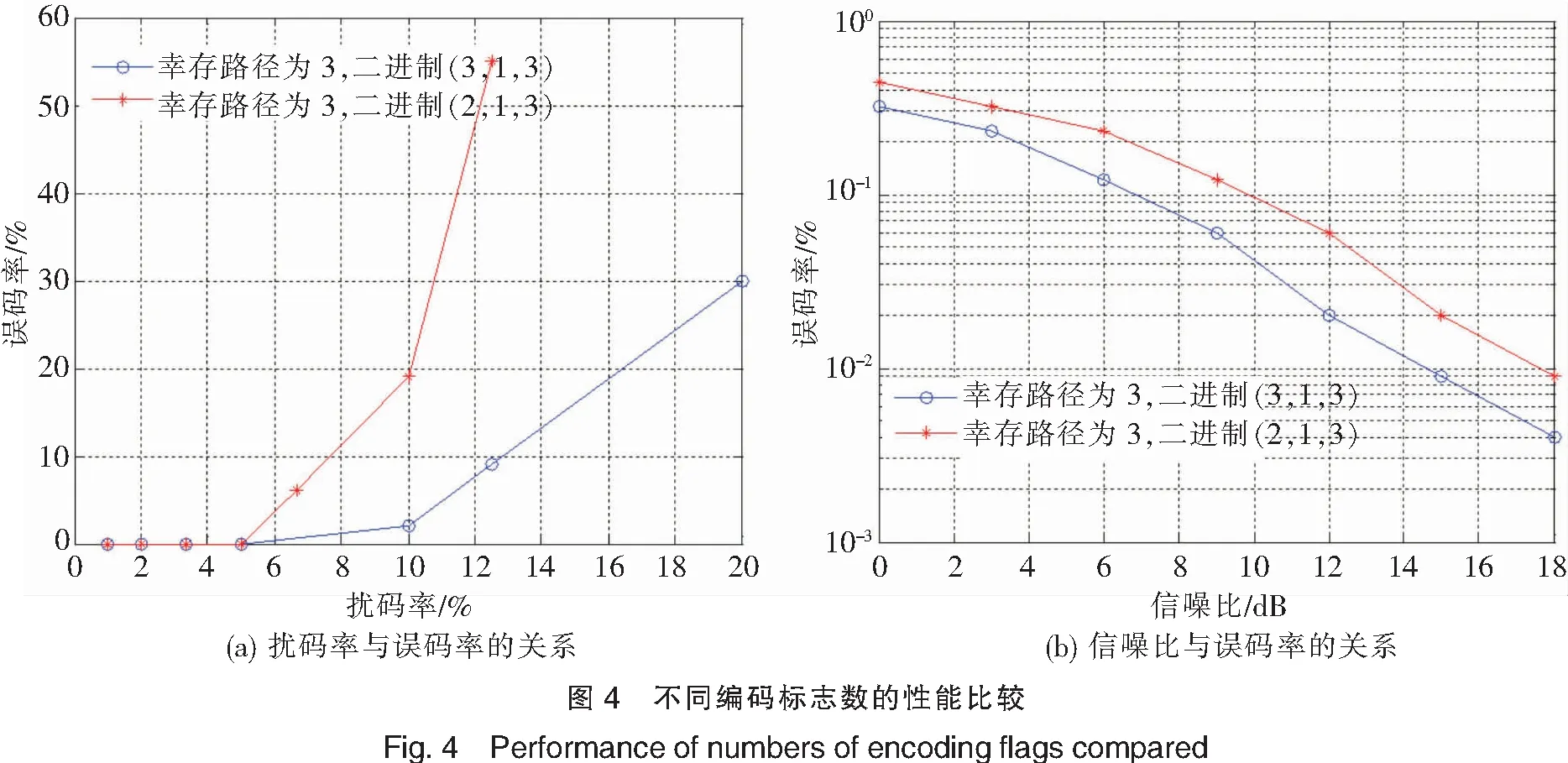

3.2 编码标志数对卷积码的影响

图4显示了卷积码的编码标志数对卷积码的影响。从图4(a)可以看出,在相同扰码率下,卷积码二进制(3,1,3)的误码率远低于卷积码二进制(2,1,3)的误码率。这意味着卷积码编码标志数n越大,其抗噪性能越优。图4(b)是从另一个侧面来分析,当信噪比一定时,卷积码二进制(3,1,3)的性能要优于卷积码二进制(2,1,3)。图4说明了编码率r=k/n对卷积码性能的影响。虽然(3,1,3)的误码率要低于(2,1,3),但(3,1,3)的编码率仅为r=1/3,而(2,1,3)的编码率为r=1/2。因此对卷积码而言,编码率与误码率是难以调和的两个性能指标。要提高系统的抗干扰性能,就不得不靠增加更多的冗余比特,这样就无形中降低了有效信息的比重。反之,若要实现高速率传输,就不得不降低抗干扰性能。

3.3 不同进制对卷积码的影响

由图5(a)可以看出,在相同扰码率下,四进制卷积码(3,1,3)的误码率低于二进制卷积码(3,1,3)。图5(b)是从另一个侧面来分析,当信噪比一定时,四进制卷积码(3,1,3)的性能要优于二进制卷积码(3,1,3)。并且当信噪比逐渐增大,效果更明显。因此,采用多进制的卷积码,不啻为另一种实现高速率传输的手段。

4 结论

基于DSP平台,模拟搭建了卷积码的通信系统。通过实验,引入扰码率的概念,从幸存路径、编码标志数、进制等不同侧面对比分析其性能。结果显示:幸存路径越大,译码性能越好,但是要以译码复杂度为代价;编码标志数越大,抗噪性能越优,但是要以牺牲数据率为代价;而高进制编码不啻为改善性能和提高数据率的有效方法之一。高速率传输与误码率是一对难以调和的矛盾。要降低误码率就需要为信息位增加冗余比特,以增强纠错性能。而本文提到的多进制卷积码,绕开了这种单纯靠约束长度来降低误码率的方法。本文的分析结果也适用于任何型号的DSP芯片,特别对未来的无线通信、卫星通信、以及高速宽带的通信都具有重要的意义。

[参考文献]

[1]RYAN W E,林舒.信道编码:经典与现代[M].白宝明,马啸,译.北京:电子工业出版社,2017.

[2]MCELIECE R J,LIN W.The trellis complexity of convolutional codes[J].IEEE Transactions on Information Theory,1996,42(6):1 855-1 864.

[3]周军,韩晓莉.Viterbi译码及其DSP算法研究[J].通信与广播电视,1999(2):15-21.

[4]赵冰.卷积编码及基于DSP的Viterbi译码器设计[J].信息与控制,2002,31(5):473-476.

[5]罗友宝,李小文.LTE系统的Viterbi译码算法仿真及DSP实现[J].光通信研究,2010(3):67-70.

[6]陈发堂,孙鹏,代修文,等.TD-LTE系统中咬尾卷积码的DSP实现及性能测试[J].电子技术应用,2014,40(6):115-118.

[7]魏旭,陈双良.基于高性能DSP的(3,2,2)卷积编解码应用研究[J].贵阳学院学报(自然科学版),2012,7(2):48-50.

[8]王宏俊,杜长斌,杨自恒,等.基于(2,1,7)卷积码实现低误码率通信的DSP设计[J].电子器件,2014,37(1):97-102.

[9]徐英杰.卷积编码及基于DSP的Viterbi译码器设计[D].北京:北方工业大学,2005.

[10]张博.卷积码的译码研究及DSP实现[D].天津:天津大学,2008.