适用动态存储的自适应刷新机制算法设计

2018-04-07龚泉铭姜秀杰安军社

龚泉铭 ,姜秀杰 ,安军社

(1.中国科学院复杂航天系统电子信息技术重点实验室中国科学院国家空间科学中心北京100190;2.中国科学院大学北京100190)

在航天研究领域,空间飞行器会在运行过程中进行各类科学数据的采集工作,例如图像处理系统和高速数据采集系统,需要在短时间内实现数据的采集、处理以及传输和存储,因此需要一种大容量、高速度、高性能的缓存设备缓存各类科学数据。同步动态随机存储器(Synchronous Dynamic Random Access Memory,SDRAM)具有的密度高、速度快、成本低的特点,使其在民用和军工领域都有着广泛的应用。虽然集成电路工艺在不断提高,但SDRAM对存储单元的充电刷新依然是十分重要的操作程序,同时也造成性能上的开销和额外的功耗。对于密度小的SDRAM,刷新造成的影响很小,但随着摩尔定律的发展,密度的提高使得刷新的性能和开销呈指数增加,成为了影响SDRAM使用的关键因素[1]。

采用传统刷新机制的SDRAM控制器实现瞬时数据吞吐率保持在100 MB/s左右,能够满足视频数据的处理需求的控制器,例如文献[2]所设计的视频解码器的高性能SDRAM控制器。为了优化刷新性能,部分控制器开展了对SDRAM刷新机制的研究,例如文献[3]中提出通过读写进程与刷新进程的交替机制,使得用户在进行全页突发写或者突发读时不考虑SDRAM刷新请求,在一定程度上优化了对SDRAM的操作。

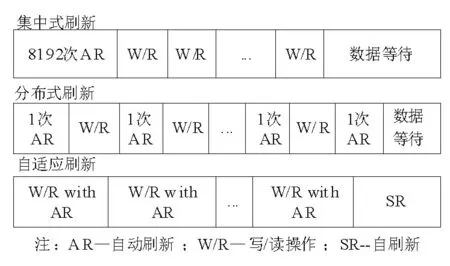

目前对刷新的优化方法结合两种刷新模式的特点,主要分为两种:集中式刷新机制和分布式刷新机制。集中式刷新机制,即在64 ms内一次性完成8192次自动刷新操作,一次性完成刷新后,在剩余的时间可全部用来完成SDRAM的数据吞吐工作。分布式刷新机制则是每7.8 ms进行一次自动刷新操作,通过自动刷新将64 ms划分为8192个时间片段,SDRAM的数据吞吐全部在时间片段中完成[4]。

文中设计实现了一种SDRAM控制机制,结合两类优化思路,研究自刷新工作模式和自动刷新工作模式的不同工作特点,针对多路数据复用情况下改善刷新模式在读/写操作中的合理分配,保证数据高效、稳定的传输和存储,同时尽量降低SDRAM的功耗。

1 SDRAM控制器整体设计

SDRAM是由PN结电容存储0/1信号的存储设备,如图1所示。由于漏电的存在,一定时间之后两级板间电位差会逐渐消失,也就是会使之前保存的信号1变成信号0,造成存储数据异常。为避免该情况发生,要在规定时间内根据存储单元里的内容补充电荷,该过程即为SDRAM的刷新操作。

图1 SDRAM数据存储单元电路图

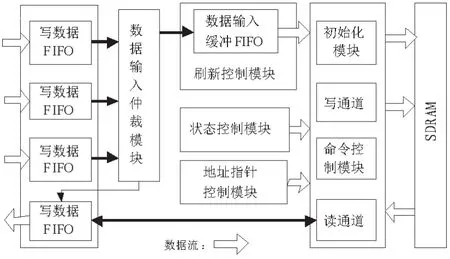

SDRAM控制器主要模块包括:输入数据缓存模块、仲裁模块、状态转换控制模块、地址指针控制模块和主控制器5部分组成,如图2所示。其中输入数据缓存模块和仲裁模块,用于缓存多路输入数据,并进行轮询仲裁后,输出给后端模块;状态控制模块用于产生各类SDRAM控制命令;地址指针控制模块对片选信号、Bank信号、行地址信号和列地址信号进行管理,并配合读/写命令输出相应地址。

图2 控制器模块组成示意图

主控制器完成对SDRAM的直接命令控制,其中包含的初始化模块,对SDRAM上电后的执行初始化;仲裁模块用于对三组输入数据的优先级仲裁;状态转换控制模块用于对SDRAM的写操作、读操作、自刷新操作和自动刷新操作的控制和转换;地址指针控制模块用于对SDRAM的片选、Bank、行地址和列地址的控制和写入。读通道则根据系统运行状态,在无数据写入请求的情况下将数据读出,进行相应转换(如并串转换)然后下传数据。其中对SDRAM的刷新机制进行了重点设计,下面进行详细阐述。

2 自适应刷新模式工作机制

SDRAM提供两种刷新模式:自动刷新模式和自刷新模式,本节首先对两种刷新模式的特点进行介绍分析;然后结合两种刷新模式特点以及实际应用需求,设计了自适应刷新工作机制;并且,对自适应刷新工作机制进行数学建模,分析讨论使用该机制运行的关键参数。

2.1 SDRAM刷新模式的工作特点

自动刷新操作,即用户向SDRAM发送刷新命令,SDRAM芯片接收到刷新命令后首先对所有的Bank进行预充电操作,然后自动向某些存储单元进行刷新重写维持电容的电压以保证数据正确,自动刷新操作完成后会再执行一次预充电操作。每一次自动刷新命令的执行,SDRAM会自动决定刷新的相应行地址和列地址,无须用户再次输入刷新地址。但是,自动刷新操作的重点是,两次行地址刷新时间间隔不能超过tREF=64 ms,使得该操作具有局限性。

自刷新模式,即SDRAM在接收到自刷新模式启动指令后独立完成所有的刷新操作,通常用于在低功耗模式下使用。一旦进入自刷新方式,SDRAM将禁止所有的外部时钟和外部输入信号,直到接收自刷新跳出信号后退出自刷新模式。为了降低功耗,刷新地址和刷新时间全部由器件内部产生。同时,需要在退出自刷新模式的过程中给出较为复杂的输入节拍予以配合。

比较两者刷新工作模式的特点:自动刷新模式,在每次刷新时都需要输入自动刷新命令,两次刷新之间相互独立,可以控制刷新的时间间隔和次数,具很好的灵活性和可操作性,但是操作相对复杂且功耗较大;自刷新模式,一段时间的刷新操作无需都多次命令输入,操作简单,功耗较低,但可控性较差,无法实现对刷新次数的控制和追踪。

2.2 自适应刷新工作机制设计

对于数据传输系统来说,数据在芯片之间传输阶段需要经历相应的控制、等待、响应等过程,因此不可能保证数据持续不间断的读写访问。单位时间内系统传输的数据量影响该系统的传输效率。SDRAM芯片由于刷新、预充电等必需操作,不可能实现全时段的数据吞吐,因此,适当合理的刷新次数,将影响SDRAM的工作效率。

根据航天应用中数据传输协议的要求,以数据包作为一个基本的传输单元,一个完备的数据包包括固定识别标识和数据包大小。为保证有写请求时数据能够第一时间写入SDRAM,尽量避免数据在合路先入先出队列(First In First Out,FIFO)处拥塞,将SDRAM的操作过程设计为写操作优先于读操作。

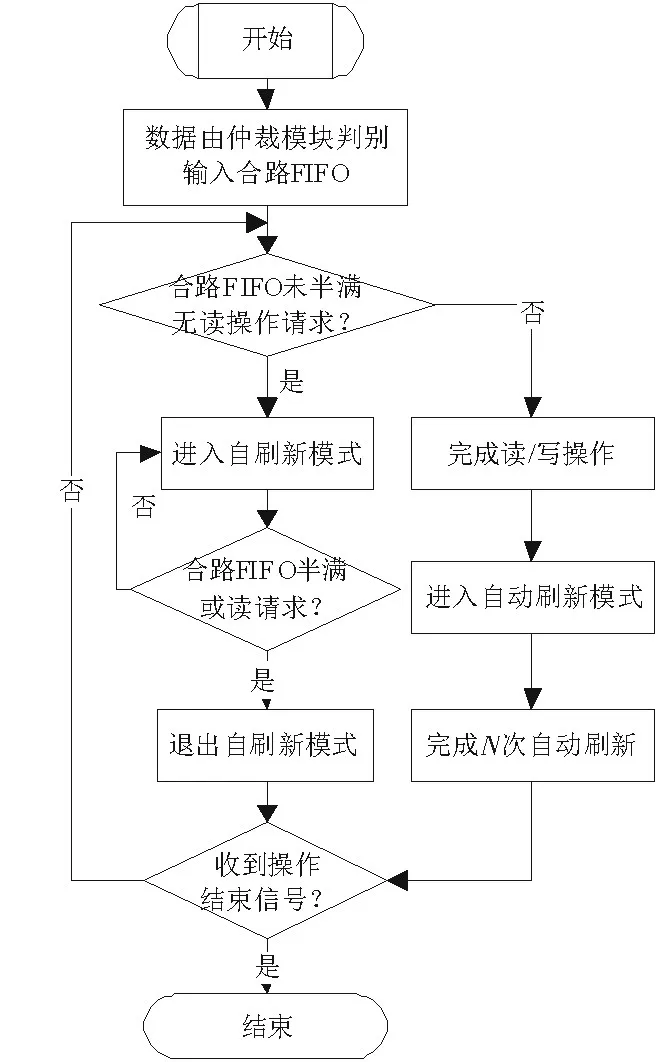

上电复位后,数据由各端口输入,采用轮询仲裁方式将外部数据进行合路处理,再由合路数据缓存模块向SDRAM中写入数据,若合路FIFO半满信号有效,认为有一个数据源包需要写入SDRAM。如若合路FIFO半满信号无效且无读操作请求需要执行,则认为SDRAM与外部无数据交互,此时SDRAM处于空闲状态,可以关闭SDRAM端口进入自刷新状态。反之,则完成读/写操作,结束后进行N次自动刷新,完成后开始下一次读/写操作。此时认为SDRAM处于繁忙状态,因而只在读/写操作间隙进行固定次数的自动刷新。具体判别流程如图3所示。

刷新控制模块通过缓存合路FIFO的状态,将SDRAM将要处于的工作状态区分为空闲状态和繁忙状态。通过判断外部输入数据的状态,自适应地选择SDRAM需要采用的刷新模式。保证在忙状态时SDRAM中数据不丢失的前提下高效有序的运转,又能在空闲状态下转入功耗更低的模式。从而实现航天领域对数据存储的可靠、高效、低功耗等要求的均衡处理。

图3 刷新工作机制流程图

2.3 刷新机制的算法设计

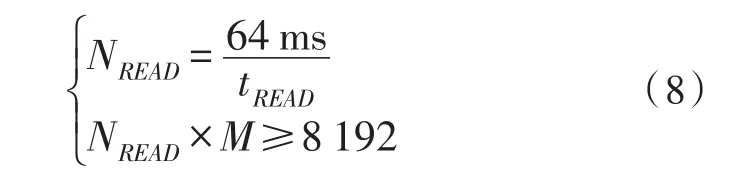

由于SDRAM的芯片手册要求,在64 ms内必须完成8 192次自动刷新操作,同时两次自动刷新操作的时间间隔需满足tRC(67.5 ns),因此在64 ms内,8 192次自动刷新占用的时间固定,即至少为tRC×8 192=553 230 ns。考虑满负荷情况下,即SDRAM一直在进行读写操作,在64 ms时间内只完成读操作、写操作以及自动刷新操作。在此情况下,保证64 ms完成8 192次自动刷新即可保证SDRAM中数据正常。因此在64 ms能够进行读写操作的次数,决定了在每次读写操作后需要进行自动刷新的次数。

在SDRAM芯片执行读写操作时,除了完成的数据写入或读出的操作之外,还需要伴随相应的其他操作,包括行激活操作(Active),即根据端口信号选择SDRAM某一行,使之进入准备读/写状态;数据转预充电操作(data in to precharge lead time,DPL),即写操作命令输入后等待写操作完成;预充电操作(Precharge),即对于已经激活并完成读/写操作的行进行充电从而结束活动状态。在完成读操作后,需要2或3个时钟周期的延迟,即延迟等待(latency)。

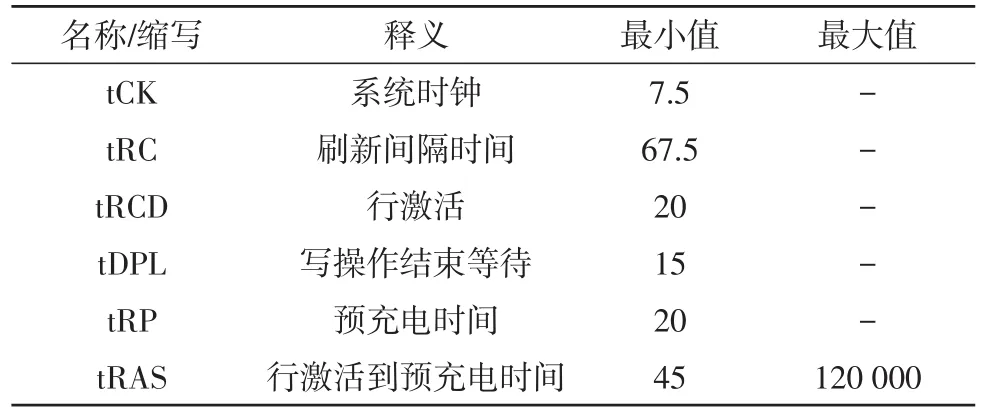

SDRAM对以上操作都有相应的时间要求,详见SDRAM时序特性表(表1)。

表1 SDRAM时序特性表

为了准确地讨论自适应刷新机制中自动刷新次数的计算问题,现给出参数定义,并且根据读写操作的区别,分析得出读写操作所使用的时间。

N:一次读操作或写操作的数据量;

M:一次连续自动刷新次数。

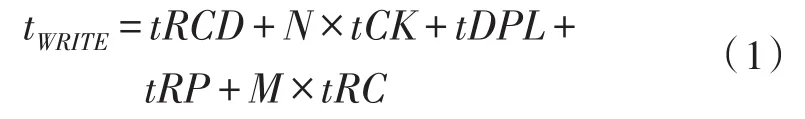

写操作:完成一次包含自动刷新的写操作所需时间为行激活操作时间、N的数据量写入的时间、写操作结束等待时间、预充电时间和M次自动刷新的时间之和。其中,考虑一个时钟周期进行一次数据操作,N个数据的输入时间为N×tCK,M次自动刷新的时间为M×tRC,其他操作的时间如表1所示,所以一次自动刷新的完整写操作时间tWRITE可表示为:

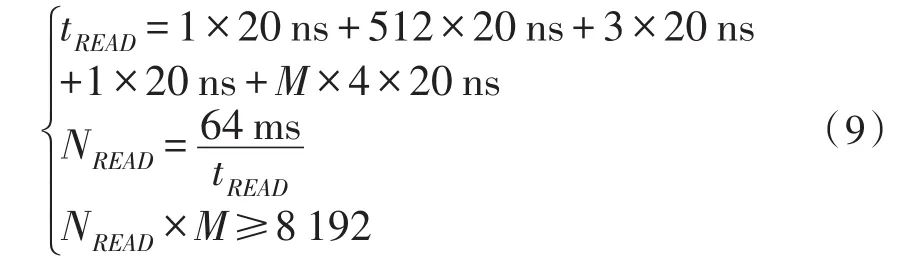

读操作:完成一次包含自动刷新的读操作所需时间为行激活操作时间、N的数据量读出的时间、读操作结束等待时间、预充电时间和M次自动刷新的时间之和。所以一次包含自动刷新的完整读操作所需时间tREAD为:

由于行激活到预充电时间的限制为tRAS,完成一次操作的数据量和系统时钟需满足以下关系:

综上所述,由式(1)、(2)可知,在单次读操作或写操作过程中,自动刷新次数M由系统时钟tCK和一次操作的数据量N决定,并且tCK和M需满足式(3)的要求。

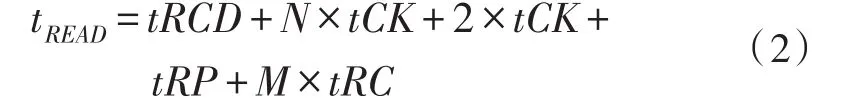

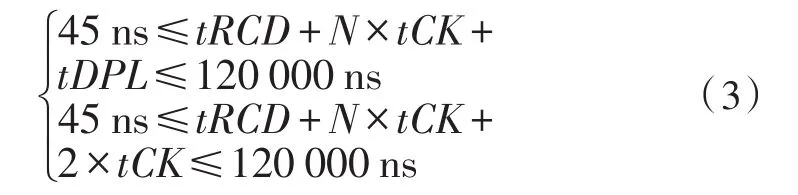

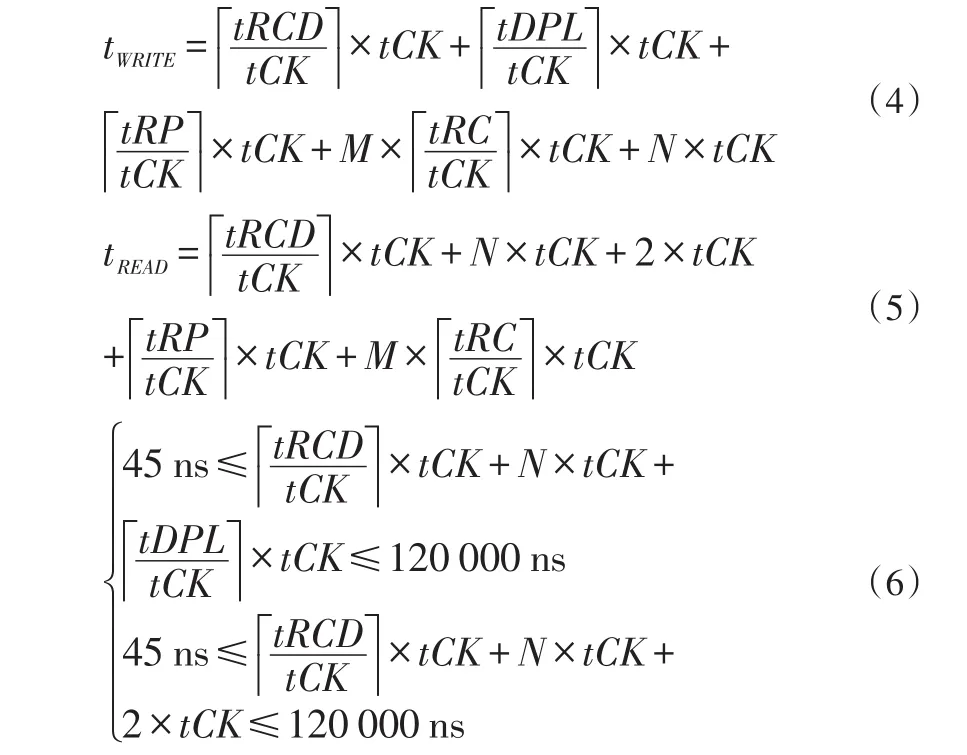

为了简化在实际FPGA设计中,对时序要求的精确实现导致的复杂度,通常采用系统时钟加计数的方式实现时序控制。对式(1)、(2)、(3)按系统时钟进行优化后,得出读写操作完成所需时间的公式如下:

由芯片手册知,该SDRAM的最大工作频率为133 MHz,即最小时钟周期为7.5 ns。同时由表1可知,tDPL≥15 ns,所以

由(1)、(2)、(7)式,可知tWRITE≤tREAD,即一次完整写操作所用时间不会大于一次完成读操作所用时间。为简化运算,将写操作的时间也等化为读操作的时间。所以64 ms内可进行的读操作次数NREAD可表示为:

其中,M取满足条件的最小整数。

由式(4)、(5)、(6)分析可得出如下结论:单次读操作或写操作内需自动刷新次数M由系统时钟tCK和单次操作的数据量N决定。

因此,当控制器的系统时钟tCK和输入的数据源包大小N给定的情况下,便可得出单次数据操作时的自动刷新次数,进而使用自适应刷新机制作为控制器的刷新方式。

现根据实际应用需求,确定实际各个执行的参数,说明如下:

1)系统时钟频率为f=50 MHz,即tCK=20 ns;

2)单次操作数据包为N=512。

采用公式(4)、(5)、(8)得出如下结论:

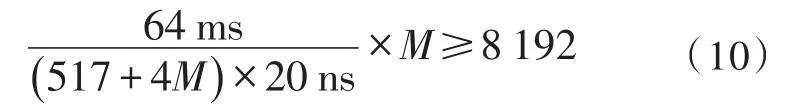

对(9)式化简可得:

计算上述式(10)求解可知:M2。

小结:对于一个使用自适应刷新机制的SDRAM控制器而言,当系统时钟为50 MHz,传输数据源包大小为512时,SDRAM完成一次数据包读/写操作后,再进行2次自动刷新操作,即可在64 ms的规定时间内完成足够次数的自动刷新操作,保证SDRAM在数据输入输出及存储过程中数据不会出现异常或丢失。

3 测试仿真与分析

本节将对SDRAM自适应刷新机制的数学模型进行测试,根据测试结果对该自适应刷新机制的工作性能进行分析。

3.1 刷新次数对传输效率的影响

以上节中的例子为基础,讨论刷新次数对传输效率的影响。以1 s作为单位时间进行分析。

1)当M=1时,由于不满足SDRAM最低的刷新次数要求,不予讨论。

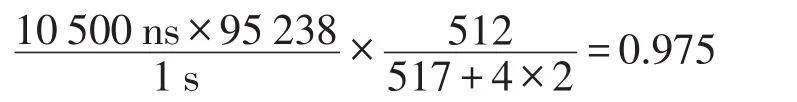

2)当M=2时,一次包含自动刷新的数据源包的传输时间为(517+4×2)×20 ns=10 500 ns,1 s时间内能够传输的总的数据包为95 238。单包读/写操作过程中数据源包传输时间占总读/写操作时间的比例为512/(517+4×2)。传输效率可表示为

3)当M=3时,一次包含自动刷新的数据包的传输时间为(517+4×3)×20 ns=10 580 ns,1 s时间内能够传输的总的数据包为94 517。单包读/写操作过程中数据源包传输时间占总读/写操作时间的比例为512/(517+4×3)。同理可得出传输效率为0.961。

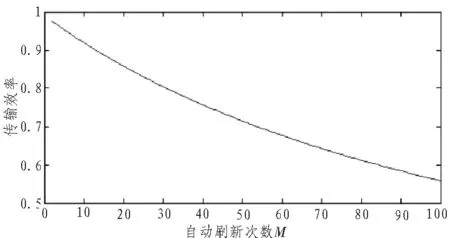

以此类推,从而得出单位时间内,不同的自动刷新次数对传输效率的影响,如图4所示。

图4 不同刷新次数下的传输效率

随着自动刷新次数M的增加,完成一次读写操作的时间增加,单位时间内传输的总数据量不断减少,传输效率也随之下降。可得出推论:当自动刷新次数M取满足约束条件最小值时,传输效率达到最大。

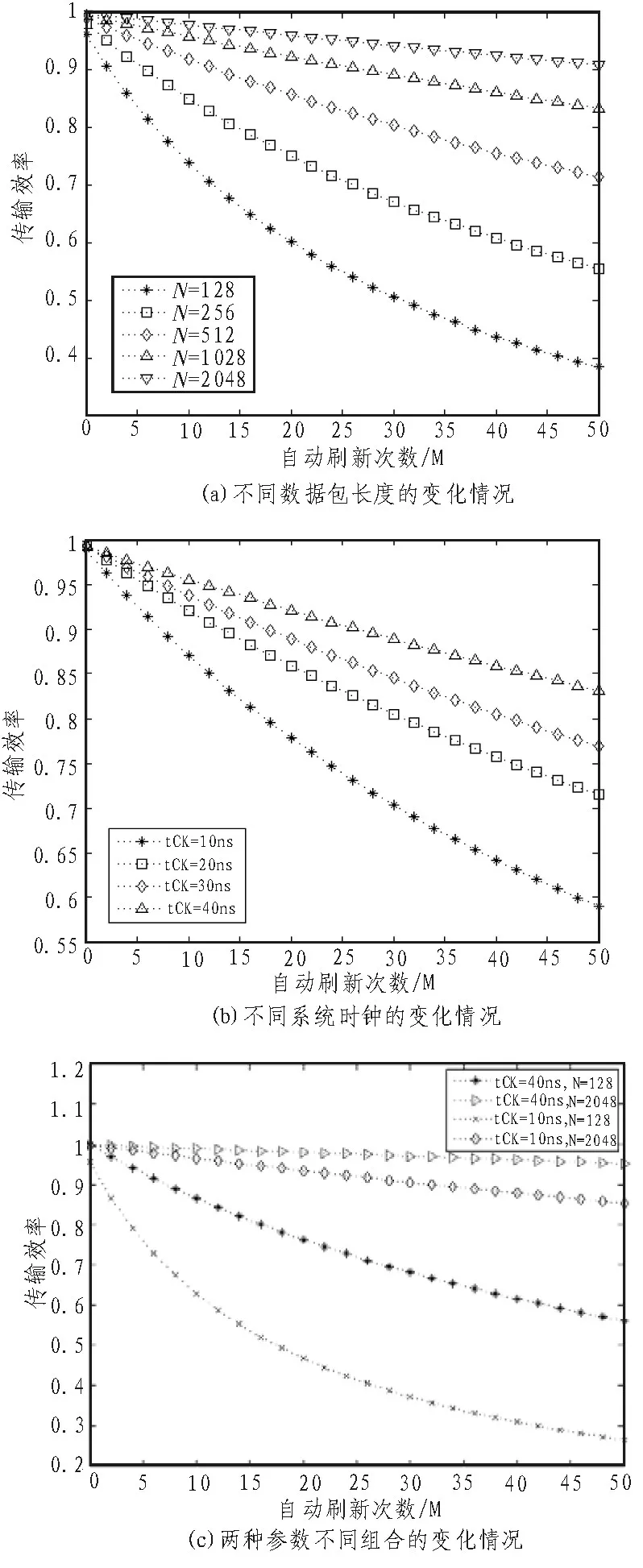

现将其推广到不同的系统时钟和不同的数据包长度的情况下进行讨论。设定系统时钟tCK为10~40 ns,即时钟频率f=25~100 MHz;数据源包长度N为128~2 048。对其在相同系统时钟下不同的数据包长度、相同的数据包长度下不同的系统时钟等工作情况进行分析,如图6所示。

图6 不同系统时钟和数据源包长下的传输效率

如图6(a)(b)所示,当系统时钟相同的条件下,数据源包长度越长,自动刷新次数M对传输效率的影响越小,同时,数据包长度越长传输效率在M值较小的时候变化率也更小;同样,当数据包长度一定的条件下,系统时钟越大,自动刷新次数M对传输效率的影响越小,在M值较小的区间内传输效率的变化率也变小但没有数据源包的影响明显。

通过图6(c)对4种极限情况的分析可知,数据源包长度N对传输效率的影响强于系统时钟tCK。本文提出的自适应刷新机制在系统时钟和数据源包都较大时,表现效果更稳定。同时,由于在实际选取自动刷新次数时,尽量选择满足条件的最小值,而由图6可知,当自动刷新次数M取值较小时,4条曲线的区分度较低。说明该刷新机制在各种条件下都能达到较好的传输效果。

3.2 刷新机制对SDRAM耗能影响

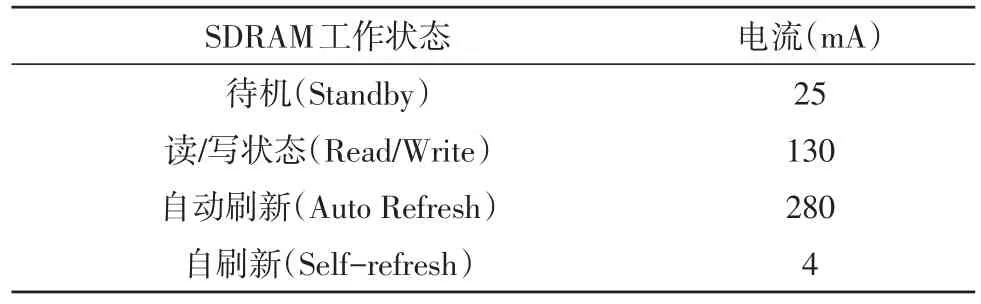

SDRAM的读/写操作会使SDRAM处于不同的工作状态,而不同的工作状态所消耗的能量不同,即不同工作状态下的电流大小不同,如表2所示。

表2 SDRAM部分工作状态下电流值

为方便分析自适应刷新机制对功耗的影响,我们将其与本文开头介绍的两种通用刷新方式(集中式刷新和分布式刷新)进行比较分析。为保证分析尽量完备,现分为3种工作情况进行讨论:

工况一:满负荷工作情况,在该工况下,SDRAM一直进行读/写操作,除必要命令外,无空闲时间。

工况二:典型工作情况,在该工况下,SDRAM间歇性的进行读写操作,即部分时间在进行读/写操作,部分时间处于等待状态。

工况三:待机工作情况,在该工况下,SDRAM处于数据等待状态。

由于SDRAM在不同工作状态下,工作电流差异较大(如表2所示)。当SDRAM处于满负荷工况下时,3种不同的刷新机制的工作情况相同,只会执行必要的读/写操作指令和足够次数的自动刷新操作。因此,在功耗上差异不大,不做具体分析。

在典型工况下,3种刷新机制的大致操作过程如图7所示。

图7 3种刷新机制的操作流程

由图7可知,在典型工况下,集中式刷新必须完成全部8 192次刷新操作,再进行其他读写命令;分布式刷新操作则按照7.8 us一次的频率刷新,无论是否有数据需要读写;自适应刷新则只在由读写操作时进行自动刷新,数据等待时间则保持在自刷新模式下。由表2可知,自动刷新的工作电流最大,而自刷新的工作电流最小。因此,在典型工作状况下,读写相同的数据量后,自刷新次数越少,SDRAM的耗能越低。

同理,在待机的工作情况下,相较于其他两种刷新机制,自适应刷新机制会让SDRAM处于自刷新状态,此时相比于待机状态功耗更小。

综上所述,SDRAM控制器通过自动刷新和自刷新两种刷新方式的自适应选择,实现两种刷新模式的协同工作,从而降低非满负荷情况下自动刷新次数;在保证数据正确传输的基础上,将自动刷新操作碎片化嵌入到每一次读写操作中,大幅度提高了传输的连续性;并在保障数据完整性的前提下,降低器件的运行功耗。

4 结 论

文中针对动态存储设备的刷新工作原理,结合自刷新与自动刷新的特点,提出了自适应刷新模式,推导了适用于典型星载大容量存储设备的自适应刷新模式参数配置计算方法;然后建立数学模型,通过蒙特卡洛模拟仿真了不同参数配置、不同工况下的动态存储传输效率变化特性,通过实际硬件平台测试验证了自适应刷新模式的有效性,对系统功耗影响的效果。研究成果:自适应刷新机制能够降低非满负荷情况下自动刷新次数,大幅度提高了传输的连续性,同时降低器件的运行功耗;能够满足复杂航天应用对数据存储的高可靠和低功耗兼顾的要求。同时,为同类型的动态存储器,例如DDR、DDR2等,提供设计参考。

参考文献:

[1]崔泽汉,陈明宇.大容量DRAM的刷新开销问题及优化技术综述[J].计算机研究与发展,2016,53(2):416-430.

[2]高战立,余桂英,唐玮.FPGA图像采集系统研究与设计[J].中国计量学院学报,2014,25(1):75-79.

[3]张林,何春.高速SDRAM控制器设计的FPGA实现[J].电子科技大学学报,2008,1.

[4]高子旺,顾美康.一种基于FPGA的低复杂度SDRAM控制器实现方法[J].计算机与数字工程,2010(1):194-196.

[5]陈朝阳,张伸,沈绪榜.一种改进的SRAM并行BIST电路设计[J].系统工程与电子技术,2005,27(1):159-162.

[6]Kim J S,Oh C S,Lee H,et al.A 1.2 V 12.8 GB/s 2 Gb Mobile Wide-I/O DRAM With 4 128 I/Os Using TSV Based Stacking[J].IEEE Journal of Solid-State Circuits,2012,47(1):107-116.

[7]Makam D,Jayashree H V.An innovative design of the DDR/DDR2 SDRAM compatible controller[C]//Nanoscience,Engineering and Technology(ICON⁃SET),2011 International Conference on.IEEE,2011:600-603.

[8]Shuang-yan C,Dong-hui W,Rui S,et al.An innovative design of the DDR/DDR2 SDRAM compatible controller[C]//2005 6th International Conference on ASIC.IEEE,2005,(1):62-66.

[9]Bakshi A,Pandey S S,Pradhan T,et al.ASIC im⁃plementation of DDR SDRAM Memory Controller[C]//Emerging Trends in Computing,Communica⁃tion and Nanotechnology(ICE-CCN),2013 Inter⁃national Conference on.IEEE,2013:74-78.

[10]Singh P, ReniwalB, Vijayvargiya V and Vishvakarma S K.Design of high speed DDR SDRAM controller with less logic utilization[J].2nd International Conference on Devices,Circuits and Systems(ICDCS),2014(14):1-6.

[11]Liu S,Pattabiraman K,Moscibroda T,et al.Flik⁃ker:saving DRAM refresh-power through critical data partitioning[J].ACM SIGPLAN Notices,2012,47(4):213-224.

[12]Liu J,Jaiyen B,Veras R,et al.RAIDR:Reten⁃tion-aware intelligent DRAM refresh[C]//ACM SI⁃GARCH Computer Architecture News.IEEE Com⁃puter Society,2012,40(3):1-12.

[13]Lee D,Kim Y,Seshadri V,et al.Tiered-latency DRAM:A low latency and low cost DRAM architec⁃ture[C]//High Performance Computer Architecture(HPCA2013),2013 IEEE 19th International Sym⁃posium on.IEEE,2013:615-626.

[14]Jevdjic D,Volos S,Falsafi B.Die-stacked DRAM caches for servers:hit ratio,latency,or band⁃width?have it all with footprint cache[J].ACM SI⁃GARCH Computer Architecture News,2013,41(3):404-415.

[15]3D PLUS DETAIL SPECIFICATION.8Gbit SDRAMEDS5104ABdatasheet[EB/OL].(2003-01).http://www.elpida.com.

[16]Micron Technology Inc.General DDR SDRAM functionality[EB/OL].[2013-01-13].http://www.micron.com.