一种高电源抑制比无片外电容LDO设计

2018-04-02张伟袁圣越田彤

张伟,袁圣越,田彤

(中国科学院上海微系统与信息技术研究所,上海200050)

随着集成电路制造工艺水平的迅猛发展,不同的功能模块,比如数字,模拟,射频电路集成在一块芯片上。然而电源噪声会大大削弱对噪声敏感的电路模块的性能,如改变VCO输出信号的频率和相位,所以必须通过电源管理模块对外部电源进行处理,得到模块所需性能标准的电压[1-3]。

低压差线性稳压器(Low Drop-Out Regulator,LDO)是电源管理中的重要模块,电源抑制比(Power Supply Rejection,PSR)决定了其对电源噪声的抑制能力[4],由于传统LDO的PSR较低,且需要外接大电容来提高电路的稳定性,不利于集成,所以,高性能LDO相继被提出[5-11]。文献[5]和[6]分别提出一种无片外电容LDO,但电源抑制比较低,不能满足对噪声敏感的射频模块的需求,文献[9]提出了一种利用两个低通滤波器提高PSR的LDO,但面积较大,不利于片上集成。

文中采用UMC 65 nm RF CMOS工艺,引入PSR增强电路,设计了一种用于射频芯片供电的,可片上集成的,高电源抑制比的无片外电容LDO。

1 LDO的PSR分析

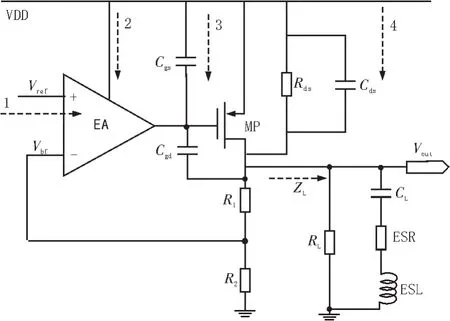

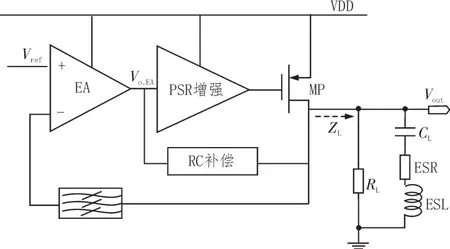

传统LDO基本结构如图1所示,主要包括误差放大器(EA),电阻反馈网络(R1,R2),功率调整管MP。

图1 传统LDO电源噪声到输出路径

电源噪声主要通过4条路径传送到输出端[11-12]。路径一是通过带隙基准电路,误差放大器和调整管传送到输出端,此通路的传输函数和带隙基准的电源抑制比PSRbg相关。路径二是通过误差放大器,调整管传送到输出端,此通路的传输函数和误差放大器的电源抑制比(Power Supply Rejection Ratio,PSRR)PSRRe相关,路径一和二的传输函数为式(2)。路径三是通过调整管MP的栅源寄生电容Cgs和调整管,将电源噪声转化为输出电流,从而影响输出电压。路径四是通过调整管有限的源漏电阻rds和漏源电容Cds传送到输出端,路径三和四的传输函数如式(3)所示。

其中,Ae和ωe分别是误差放大器的低频增益和输出极点,gm和rds分别是功率调整管的跨导和沟道电阻,R1和R2是反馈电阻,ZL(s)是输出端等效负载阻抗,He(s)是LDO的开环增益,β(=R2/(R1+R2))是反馈系数。

由(2)和(3)式可得低频段和高频段的总的传输函数可分别近似为:

低频情况下,由于误差放大器的增益Ae较大,式(4)的最后一项较小,即电源噪声通过路径三和四传送到输出端的噪声较小,主要是路径一和二限制了LDO的PSR,即由PSRbg和PSRRe决定,并被反馈电阻网络放大(1+R1/R2)倍,增大PSRbg和PSRRe即可提高低频段LDO的PSR。

中高频情况下,由于运算放大器有限的输出极点,通路一和二对PSR的影响相对较小,故主要是通路三和四限制了中高频情况下LDO的PSR。可通过减小路径三和四对输出的影响,从而提高中高频情况下的PSR。

由于Cgs的存在,调整管MP的栅端电压受电源噪声的影响,若调整管的栅源电压差变化ΔVgs,则输出电压变化为:

如果可以使ΔVgs=0,即调整管的栅源电压差不受电源噪声的影响,则可消除电源噪声通过路径三对输出的影响,提高LDO的PSR。

2 本文提出的LDO

2.1 LDO原理框图

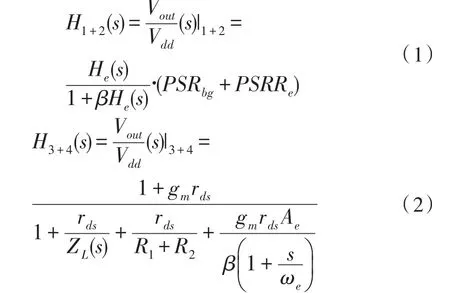

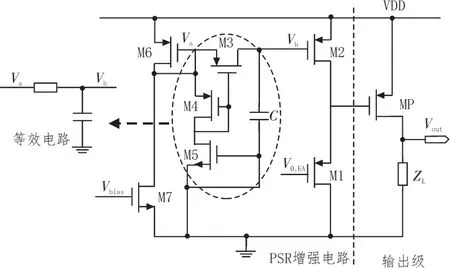

本文提出的LDO框图如图2所示,去掉了传统LDO中反馈电阻R1和R2,LDO的输出直接反馈回误差放大器的输入端。在误差放大器和调整管之间引入了PSR增强电路,采用RC补偿网络保证电路稳定性,在反馈回路引入低通滤波器。

图2 本文提出的LDO框图

2.2 PSR增强电路

如图3所示,虚线左侧为PSR增强电路,虚线右侧为LDO输出级,去掉了传统LDO结构中的反馈电阻R1和R2,LDO的输出直接反馈回误差放大器的输入端。

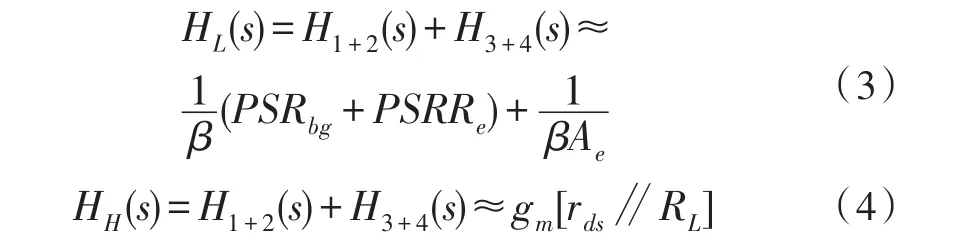

图3 PSR增强电路

M5的栅端和源端接地,产生极小的泄漏电流,使M4的栅端电压和源端电压几乎相等,则M3的栅端电压和源端电压也几乎相等,令M4的宽长比比M3大的多,此时M3的源漏端等效为一个GΩ级的电阻,与电容C构成截止频率极低的低通滤波器,如图3中等效电路所示。在10 Hz附近,M2栅端电压的大部分噪声被滤除,使其栅端交流小信号等效接地。此种方法构成的低通滤波器,不仅滤波效果很好,而且降低了对电容C值的需求,减小了片上电容和电阻所需的版图面积,适合片上集成。

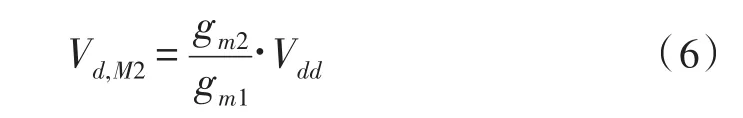

对于电源噪声Vdd,管子M2相当于一个共栅极放大器,则电源噪声Vdd传递到M2的漏端的小信号为:

其中,gm1和gm2分别为M1和M2的跨导。

本文提出的LDO中,误差放大器采用的是NMOS管输入的折叠共源共栅结构的差分放大器,根据文献[13]的分析可知,该结构对电源噪声有一定的屏蔽作用,使误差放大器的输出端几乎不受电源噪声的影响。故运放输出端,即M1的栅端不受电源噪声的影响,即电源噪声不会通过源跟随器M1传送到调整管的栅端。

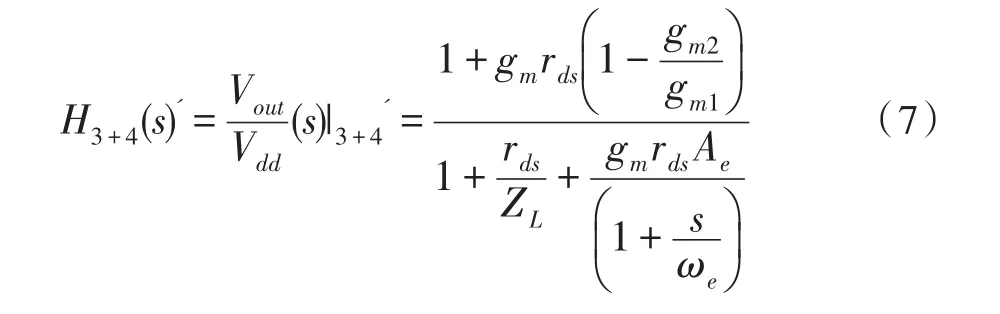

输出端的噪声通过反馈回路,误差放大器,M1传至调整管的栅端,从而进一步稳定输出电压。综上可得加入PSR增强电路结构后,路径三和四的传输函数为:

根据第一节的分析,可推得无PSR增强电路和反馈电阻结构的LDO中,路径三和四的传输函数如下:

比较式(8)和式(9)可知,PSR增强电路的引入使LDO的PSR显著提高。由式(8)可知,若分子为零,即1+gmrds(1-gm1/gm2)=0,即gm2=(1+1/gmrds)gm1时,路径三和路径四的传输函数为零,即可得理想情况下无限大的PSR,故适当调整管子M1和M2的大小,使gm1和gm2接近上述关系,可以进一步优化LDO的PSR。

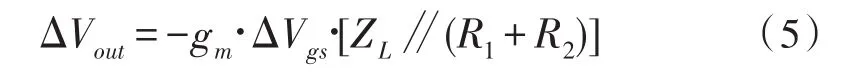

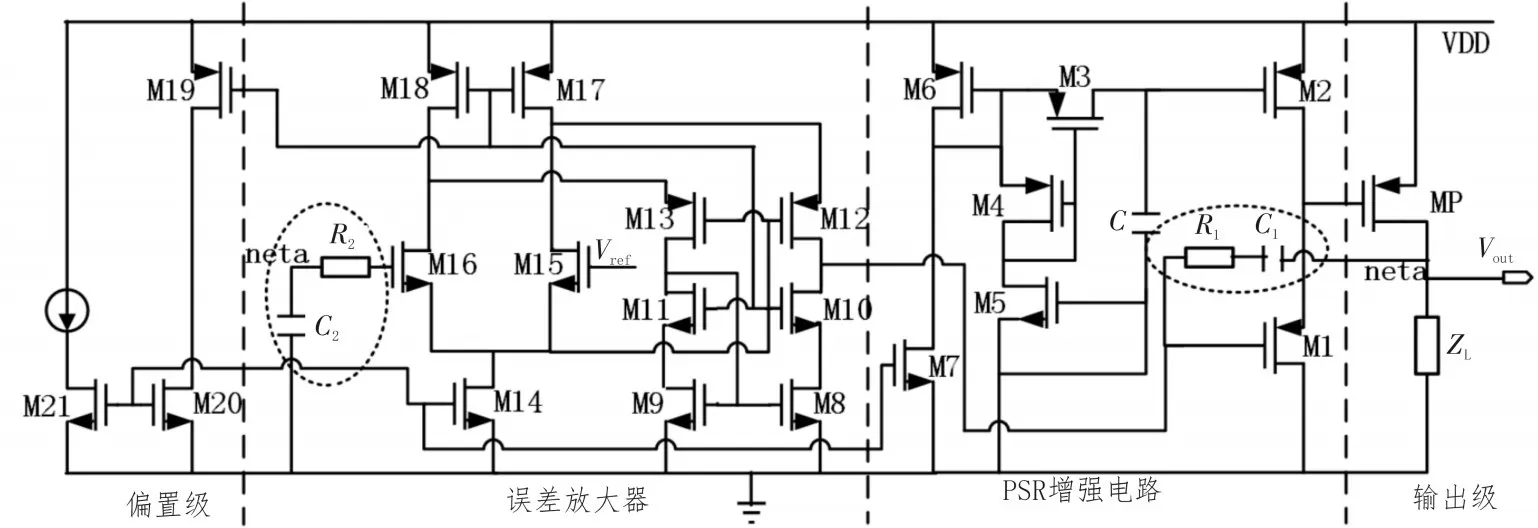

图4 本文提出的LDO电路图

2.3 LDO电路分析

本文提出的LDO具体电路如图4所示,包括偏置级,误差放大器,PSR增强电路,输出级,串联电阻电容补偿网络,反馈回路上的低通滤波器几个部分。

在误差放大器的输出端和功率调整管MP的漏端之间引入串联的电阻R1和电容C1构成的补偿电路,保证了系统的稳定性。

误差放大器为折叠共源共栅结构,可以提供较大增益,并且只引入一个极点,从而降低对补偿电路的要求。适当增大M8,M9,M17,M18的过驱动电压,可以有效降低误差放大器的等效输入噪声。去掉反馈电阻R1和R2,即消除了反馈电阻的热噪声,从而进一步降低了LDO的输出噪声。

LDO的输出至误差放大器的反馈回路加入了由R2和C2构成的低通滤波器,有效降低了由于输出端接不同负载以及后级震荡对LDO反馈回路的影响,其电容C2可以在版图面积允许的范围下,大量铺设,保证反馈回路的信号稳定。

3 仿真结果

基于UMC 65nm RF CMOS工艺,采用Cadence Spectre RF工具对本文提出的LDO进行仿真。电源电压为1.8 V,输出电压为1.2 V,负载电流为30 mA。

环路交流小信号特性仿真结果如图5所示,相位裕度为86.8°,增益裕度为33.4 dB,表明系统处于稳定状态。

图5 开环增益和相位频率响应仿真

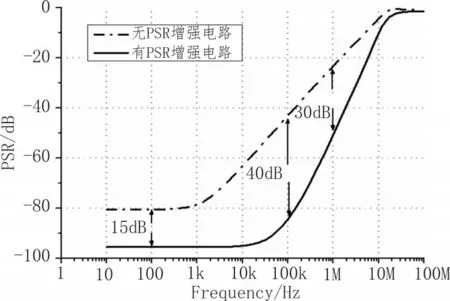

改进前后LDO的PSR仿真结果对比如图6所示,其中虚线为没有PSR增强电路的LDO的PSR仿真结果,实线为加入PSR增强电路的LDO的PSR曲线。可以看出,本文提出的LDO在10 kHz处,PSR为-95.2 dB,100 kHz处,PSR为-84.4 dB,在1 MHz处为-50.6 dB,相比无PSR增强电路的LDO,PSR分别提高了15 dB,40 dB和30 dB。

图6 有无PSR增强电路的LDO的PSR仿真

LDO的输出噪声曲线如图7所示,在100 kHz处的频点噪声为8.3 nV/√Hz,1 MHz处的频点噪声为6.9 nV/√Hz,结果表明该LDO具有较低的输出噪声,可以满足对噪声敏感的射频电路的需求。

图7 输出噪声仿真

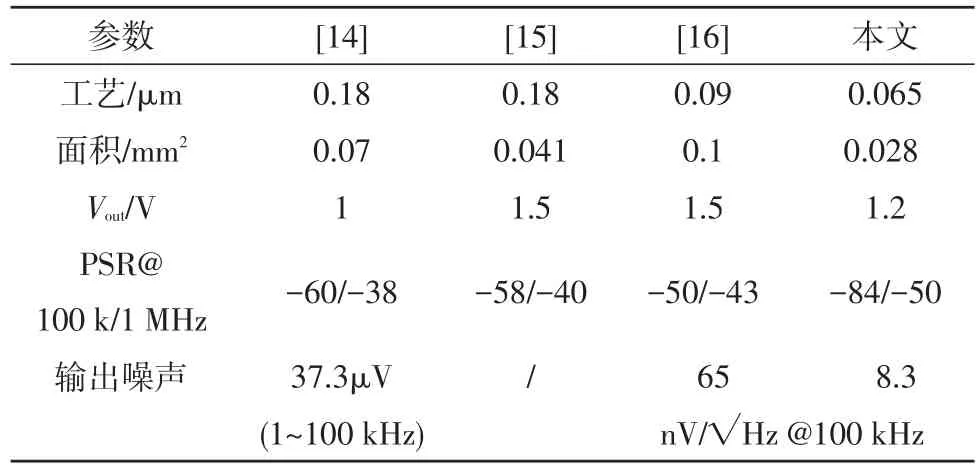

表1为本文设计的LDO与已发表文献中LDO的性能比较,由表可知本文LDO在具有较高PSR的同时,输出噪声很低,适合为射频芯片供电,且芯片面积较小,无片外电容,有利于片上集成。

表1 LDO性能的总结与比较

4 结 论

文中提出了一种带PSR增强电路的LDO,在1 MHz处,PSRR为-50.6 dB,输出噪声为6.9 nV/√Hz,相比无PSR增强电路的LDO,PSR提高了30 dB,可广泛用于对电源抑制比要求较高的射频电路中。并引入串联RC补偿网络,保证了电路的稳定性,除去了片外补偿电容,易于片上集成。相比现有文献中LDO的性能,本设计PSR相对较高,且芯片面积和输出噪声很小。

参考文献:

[1]Zhan C,Ki W H.An output-capacitor-free adaptively biased low-dropout regulator with subthreshold undershoot- reduction for SoC[C]//Circuits and Systems(ISCAS),2011 IEEE International Symposium on.IEEE,2011:45-48.

[2]王建伟,张启帆,张先仁,等.一种用于VCO供电的低噪声LDO[J].微电子学,2015(5):602-606.

[3]With Full-Spectrum Power Supply Rejection[J].Circuits& SystemsIRegularPapersIEEE Transactions on,2015,62(3):1-10.

[4]Gabriel A R.LDO模拟集成电路设计[M].谭旻等,译.北京:科学出版社,2011.

[5]Luo H,Siek L.An output-capacitor-less lowdropout voltage regulator with high power supply rejection ratio and fast load transient response using boosted-input-transconductance structure[C]//EDSSC 2015,Conference on Electron Devices and Solid-State Circuits,2015.

[6]Chong S S,Chan P K.A 0.9-uA quiescent current output-capacitorless LDO regulator with adaptive power transistors in 65-nm CMOS[J].Circuits&Systems I Regular Papers IEEE Transactions on,2013,60(4):1072-1081.

[7]温晓珂,谈熙,闵昊.用于射频SOC芯片的低噪声高电源抑制比LDO[J].固体电子学研究与进展,2011,31(3):274-279.

[8]Ho E N Y,Mok P K T.Wide-Loading-Range fully integratedLDRwithaPower-Supplyrippleinjection filter[J].Circuits&Systems II Express Briefs IEEE Transactions on,2012,59(6):356-360.

[9]Guo J,Leung K N.A 25mA CMOS LDO with-85dB PSRR at 2.5MHz[C]//Solid-State Circuits Conference.2013:381-384.

[10]王磊,杨云,许志斌,等.一种高电源噪声抑制比的LDO设计[J].微电子学,2015(5):590-593.

[11]EL-NOZAHI M,Amer A,Torres J,et al.High PSR low drop-out regulator with feed-forward ripple cancellation technique[J].IEEE J Sol StaCirc,2010,45(3):565-577.

[12]Park C J,Onabajo M.SILVA-Martinez J.External capacitor-less low drop-out regulator with 25dB superior power supply rejection in the 0.4-4MHz range[J].IEEE J Sol StaCirc,2014,49(2):486-501.

[13]Gupta V,Rincon-Mora G A,Raha P.Analysis and design ofmonolithic,high PSR,linear regulators for SoC applications[C]// SOC Conference,2004.Proceedings.IEEE

[14阴亚东,阎跃鹏.一种低噪声高电源抑制比CMOS低压差线性稳压器[J].固体电子学研究与进展,2013,33(6):571-577.

[15]Yang B,Drost B,Rao S,et al.A high-PSR LDO using a feedforward supply-noise cancellation technique[C]//Custom Integrated Circuits Conference.2011:1-4.

[16]Khadiri K E,Qjidaa H.A low noise,high PSR low-dropout regulator for low-cost portable electronics[C]//ComputerSystems and Applications(AICCSA).NY,USA:IEEE,2013:1-5.