基于TMS320F28035CLA的IIR低通滤波器设计

2012-09-22,

,

(华南理工大学 自动化科学与工程学院,广东 广州 510640)

1 引言

随着世界经济的发展,全球对绿色能源的呼声越来越高,作为绿色能源装置的一种——变频装置也适应时势发展,正在世界范围内大量投入使用。例如三相变频器、三相整流器、三相有源逆变器和三相有源滤波器的大量投入使用可以大大提高电能利用率,减少电能的浪费,实现节能的目的。但是在这些变频控制中,控制信号不可避免的要受到开关电源高频开关信号或者IGBT高频开关信号的影响,使ADC采样得到的信号夹带有高频信号干扰,从而导致控制算法得到错误的信号,产生误动作,使控制效果下降甚至失效。在Piccolo系列DSP芯片CPU中虽然可以设计滤波器,但是滤波器的运行会增加CPU开销,使CPU无暇处理其他诸如通信、诊断之类的系统任务。而TMS320F28035芯片的CLA是一个独立并行控制的单元,它能替CPU分担处理一些诸如滤波器算法的程序,减少CPU的开销,使CPU有更多时间去处理诸如通信、诊断之类的系统任务[1]。

基于上述原因,本文在TI公司Piccolo系列DSP芯片TMS320F28035的CLA硬件平台上设计出IIR低通滤波器,它能有效的滤除高频信号的干扰,解决三相变频控制信号受高频信号干扰的难题,提高控制系统的控制精度,同时减少CPU的开销。本文主要给出IIR低通滤波器的Matlab/Simulink仿真设计和在TMS320F28035芯片CLA硬件平台上的软件设计。最后通过实验验证IIR低通滤波器设计的正确性。

2 IIR低通滤波器的Simulink仿真设计

在三相变频控制系统中,和有效的控制信号频率相比,干扰信号的频率要高得多,比如开关电源的开关频率在50kHz以上,IGBT通常的开关频率在20kHz以下。所以根据变频控制的要求,本文设计的IIR低通滤波器的参数为:采样频率fsamp=200kHz,通带截止频率fp=20kHz,阻带下限截止频率fs=40kHz,通带允许最大衰减αp=3dB,阻带应达到的最小衰减αs=40dB,采用Butterworth低通滤波器设计[2]。

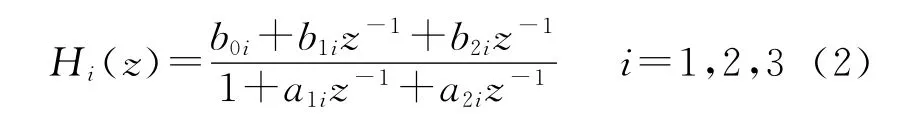

在Matlab中调用buttord函数计算Butterworth低通滤波器的阶数、调用butter函数计算零极点,调用zp2sos函数计算Butterworth低通滤波器转移函数的级联形式:

其中

a21=2.618 612e-001a11=-1.004 155

b21=4.066 330e-004b11=8.132 660e-004b01=4.066 330e-004a22=4.003 438e-001

a12=-1.114 355b22=1b12=2b02=1a23=7.289 975e-001a13=-1.375 889b23=1b13=2b03=1。

转移函数的频率响应曲线见图1。

图1 IIR低通滤波器的频率响应曲线Fig.1 The frequency response of IIR low-pass filter

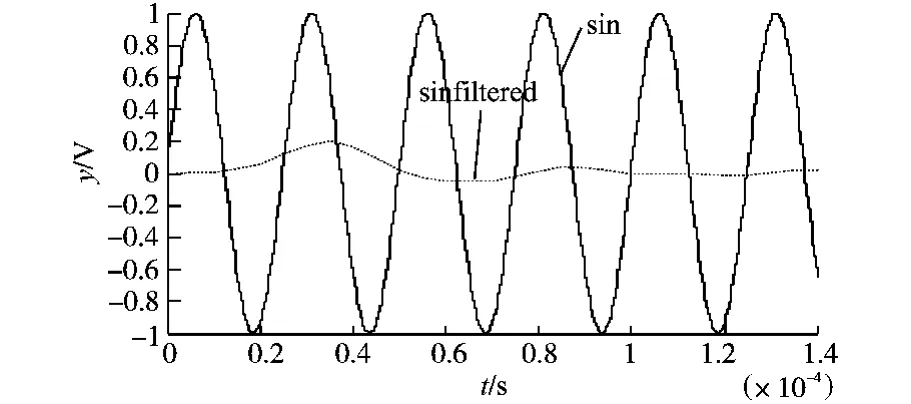

在Simulink[3]中 Butterworth低通滤波器的仿真如图2所示。分别将5kHz和40kHz的正弦波输入IIR低通滤波器仿真验证得到输出波形如图3和图4所示。

图2 IIR低通滤波器的仿真图Fig.2 The simulation of IIR low-pass filter

图3 5kHz正弦波仿真验证Fig.3 5kHz sine waves simulation validation

由图3和图4仿真可知,5kHz的正弦波可以完全通过IIR低通滤波器,只是相位有延时,这是IIR滤波器本身的特点决定的。40kHz的正弦波通过IIR低通滤波器后则可以完全滤除,满足设计的要求。

图4 40kHz正弦波仿真验证Fig.4 40kHz sine waves simulation validation

3 CLA中IIR低通滤波器的软件设计

3.1 CLA硬件触发机制的设计

TI的TMS320F28035芯片中的CLA是一个独立、完全可编程的32位浮点数字处理器,它将并行控制执行功能引入到C28x系列芯片中。CLA的低中断延迟使得它能即时读取ADC采样的结果。这就极大降低了ADC采样到输出的延时,实现了更快的系统响应和更高频率的控制回路。通过利用CLA来服务对时间要求严格(time-critical)的控制回路,主CPU就能自由地处理其他诸如通信、诊断之类的系统任务[1]。CLA在芯片中的结构见图5。

图5 CLA硬件触发机制结构图Fig.5 CLA hardware trigger mechanism structure

根据TMS320F28035芯片的硬件特点和CLA的结构框架,本文选择PWM4硬件中断触发ADC转换,在ADC模块中选择ADCINT4连续中断触发CLA运行IIR低通滤波器的程序。最后由CPU读取滤波的结果。由于CLA和CPU同步而且都是60MHz的时钟频率,每一路IIR低通滤波器大概需要运行1.5μs的时间(90条汇编指令运行所需要的时间),本文需设计3路IIR低通滤波器,则3路IIR低通滤波器运行最少需要4.5μs的时间。所以采用5μs(200kHz中断频率)的PWM硬件中断频率触发ADC转换,ADCINA3通道每转换完成一次,就触发一次CLA运行IIR低通滤波器,这就保障了IIR低通滤波器的采样频率为200kHz,同时保障了3路IIR低通滤波器有足够的时间运行完毕,如图5所示。

如果这3路IIR低通滤波器程序用CPU来执行,即CPU需采用200kHz(5μs)中断频率运行IIR低通滤波器的程序,每次运行需消耗4.5 μs的时间,这就极大地增加了CPU的开销,使CPU无暇处理其他诸如通信、诊断之类的系统任务。用CLA处理IIR低通滤波器的程序则可克服这一致命的缺点,这正是CLA能减少CPU开销的原因。

3.2 IIR低通滤波器的软件设计

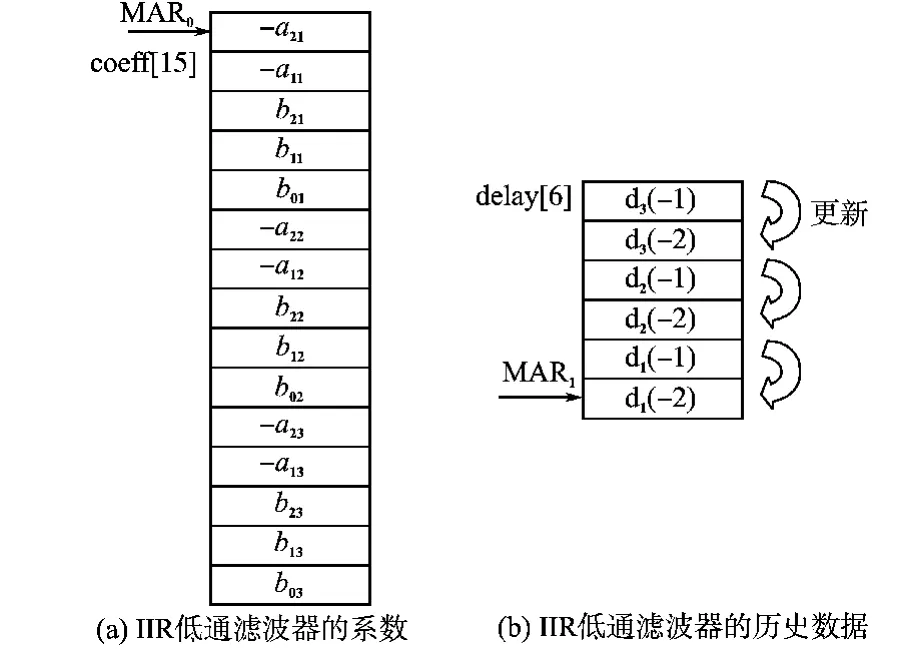

IIR的直接实现存在系数的量化误差及乘法器的舍入误差对输出都将有积累效应的缺点,致使输出误差偏大;CLA中程序的执行是基于时序和跳转机制进行的,所以本文采用级联的形式来编程实现IIR低通滤波器。IIR的级联实现[4]见图6。

图6 IIR的级联实现Fig.6 The cascade realization of IIR

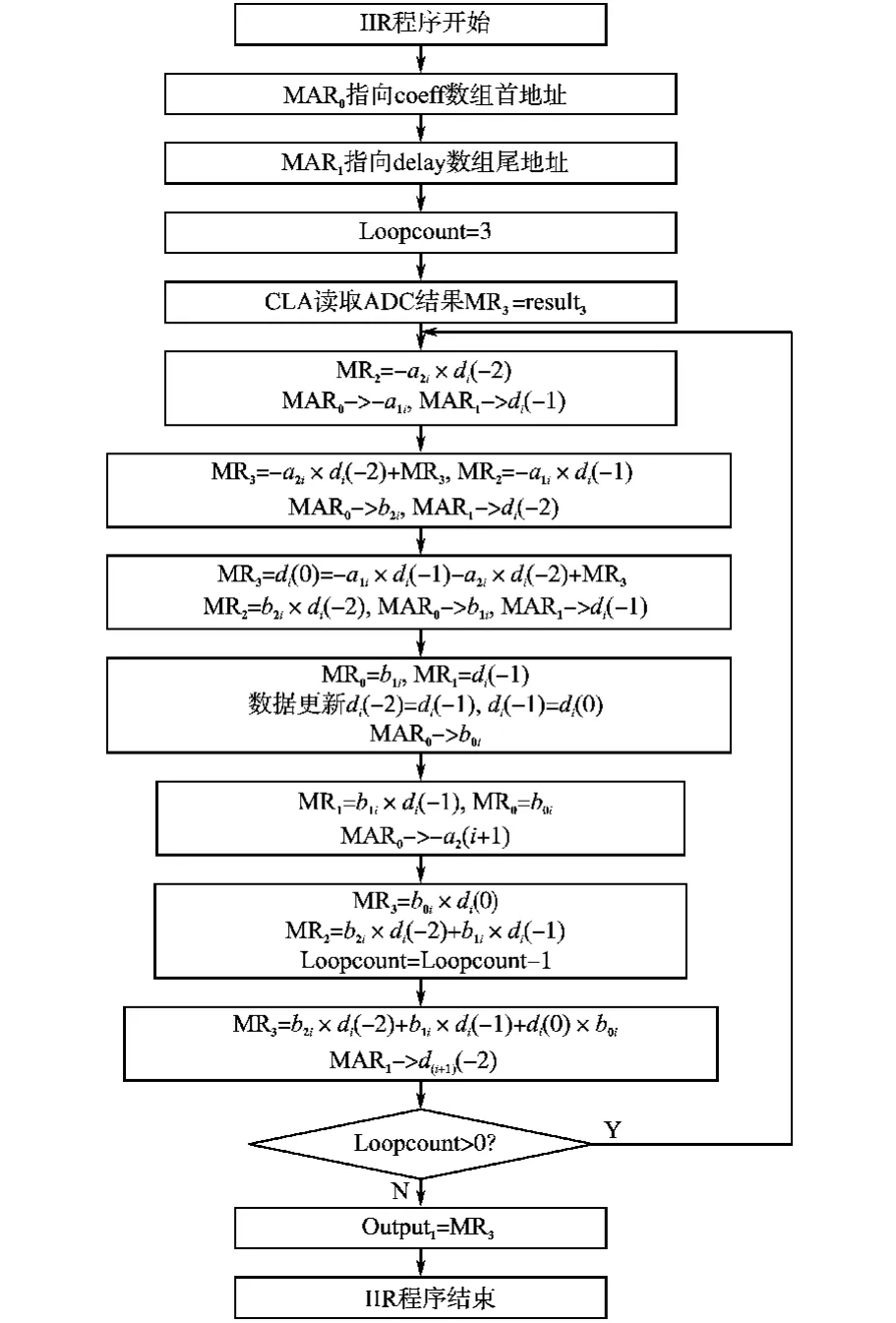

由图6、式(1)和式(2)可知,本文设计的IIR低通滤波器是由3个二阶子系统级联实现的,第1个二阶子系统的输出作为第2个二阶子系统的输入,第2个二阶子系统的输出作为第3个二阶子系统的输入,程序需要执行2次循环才能完成。CLA中IIR的汇编程序[1,5]流程图见图7和图8。

图7 IIR滤波器的系数结构和历史数据结构Fig.7 IIR filter coefficient and history data structure

图7和图8中MAR0和MAR1为CLA的辅助寄存器,在此当成指针来使用;MR0,MR1,MR2和MR3为CLA的浮点32位结果寄存器。

图8 IIR低通滤波器的汇编程序流程图Fig.8 The IIR low-pass filter assembly program flow

4 IIR低通滤波器的实验测试

对本文设计的IIR低通滤波器进行测试。

图9~图11分别为在TMS320F28035芯片CLA硬件平台上输入50Hz,5kHz和40kHz的正弦波测试图,其中通道1为信号波形,通道2为经过IIR低通滤波器的输出波形。由图可知50 Hz的正弦波可以完全通过;5kHz的正弦波可以通过只是相位有延时,和图3仿真结果一致;40 kHz的正弦波则完全被滤除,和图4仿真结果一致。从而验证了在CLA上设计IIR低通滤波器的正确性。

图9 50Hz正弦波验证测试Fig.9 50Hz sine waves validation test

图10 5kHz正弦波验证测试Fig.10 5kHz sine waves validation test

图11 40kHz正弦波验证测试Fig.11 40kHz sine waves validation test

5 结论

在TMS320F28035芯片CLA硬件平台上设计的IIR低通滤波器,可以有效地滤除变频控制系统中高频信号的干扰,解决三相变频控制信号受高频信号干扰的难题,提高控制系统的控制精度。同时,在CLA中设计IIR低通滤波器,替CPU分担处理了滤波器的程序,减少了CPU的开销,使CPU有更多时间去处理诸如通信、诊断之类的系统任务。最后通过实验验证了IIR低通滤波器设计的正确性。

[1]Texas Instruments Incorporated.TMS320x2803xPiccolo Control Law Accelerator(CLA)Reference Guide[Z].Texas Instruments,2009.

[2]丁玉美,高西全.数字信号处理[M].西安:西安电子科技大学出版社,2005.

[3]林飞,杜欣.电力电子应用技术的 MATLAB仿真[M].北京:中国电力出版社,2009.

[4]胡广书.数字信号处理理论、算法与实现[M].第2版.北京:清华大学出版社,2003.

[5]汪安民,程昱.DSP应用开发实用子程序[M].北京:人民邮电出版社,2005.