基于并行Flash的USB3.0中扰码-解扰码器的设计与实现∗

2018-03-20尹旭东

尹旭东

(合肥工业大学电子科学与应用物理学院 合肥 230009)

1 引言

USB3.0的最大传输带宽是5Gbps,如果进行一位的串行扰码与解扰码,就要求电路的工作频率能够达到5GHZ,这对硬件的速度来说是个很大的挑战,明显不符合实际应用。当系统对数据的扰码与解扰码是按照一个字节8bits进行并行处理,由5Gbps/8bits=625MB/s可得电路的工作频率要达到625MHz,这个速度对于硬件也具有较高要求,使开发设计成本增高。所以对并行处理的数据位宽做进一步扩展,一次处理2个字节也就是16bits,这时的硬件速度要求是625MHz/2=312.5MHz,一般的FPGA开发板就能满足要求,降低了开发的难度和成本[6]。因此,我们应该对USB3.0中的扰码-解扰码器进行多数位的并行处理。

如今的FPGA开发板含有并行flash结构,随着技术的进步,flash的容量不断扩大,使得留给用户使用的空间越来越多。本文拟基于FPGA开发板中的并行flash实现USB3.0中的扰码-解扰码器的并行设计,虽然需要占用一定的存储资源,但其应用了扰码-解扰码器具有周期性的原理,将每个扰码状态的末位存储在flash中,再直接与待扰或者待解扰数据异或即可实现扰码或解扰码功能[4]。它不需要按照扰码的特征多项式进行不断的递推,不需要占用过多的硬件资源,只需要占用很小部分的并行flash存储空间。因而,该方法能快速、高效、简单可靠地设计出USB3.0中的扰码-解扰码器。

2 扰码/解扰码的作用与原理

在通信系统数据的传输过程中,数据信息序列中往往不可避免地会出现较长的连续“0”或者“1”序列,它将会影响接收端定时信号的恢复,致使接收端可能接收信息发生错误。

在实际应用中,常使用扰码器搅乱数据,它改变了数字信号的统计特性,使之变成近似于白噪声的数据序列。扰码后的数据序列中几乎不再有较长的连续“0”或者“1”,并且输出序列中“0”和“1”比较均衡。扰码与解扰码在通信系统中是成对出现的,解扰码器的作用是还原数据信息。

普遍的扰码方法是在输入数据序列上加一个最长线性反馈移位寄存器序列,数据序列按位依次与线性反馈移位寄存器的输出异或,相应地在接收端扰码后的数据序列按位依次与同样的线性反馈移位寄存器的输出异或进行解扰码,可还原出原数据序列[1]。

如图1所示是一个典型的n级线性反馈移位寄存器。它之所以能够完成扰码与解扰码的功能是与其几个重要性质密切相关的。1)它能够产生周期为2n-1的最长线性反馈移位寄存器序列。2)最长线性反馈移位寄存器序列具有均衡性,在其一个周期中,“1”的个数比“0”的个数多一个。3)最长线性反馈移位寄存器序列的游程分布具有规律性,游程数共有2n-1个,长度为k的游程数目占总数的2-k,而且在长度为k的游程中连“1”的游程和“0”的游程各占一半。4)在一定条件下最长线性反馈移位寄存器序列的功率谱密度近似于白噪声的功率谱。

图1 线性反馈移位寄存器

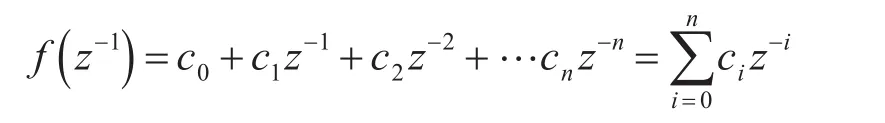

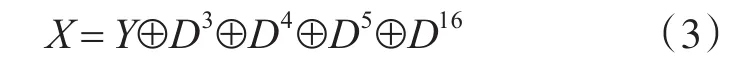

反馈移位寄存器n阶特征多项式为

其中z无实际意义,只起到表征作用。Ci(i=1,2,3…n)是线性反馈移位寄存器的反馈系数,当Ci取值为1时代表某一级D触发器输出参加反馈网络的异或运算,否则表示不参与运算,一般情况下C0和Cn总是为1。加扰和解扰均采用变形的m序列发生器,即根据应用的场合,Ci取值为1或者0[8]。

3 普通加扰器与解扰器设计

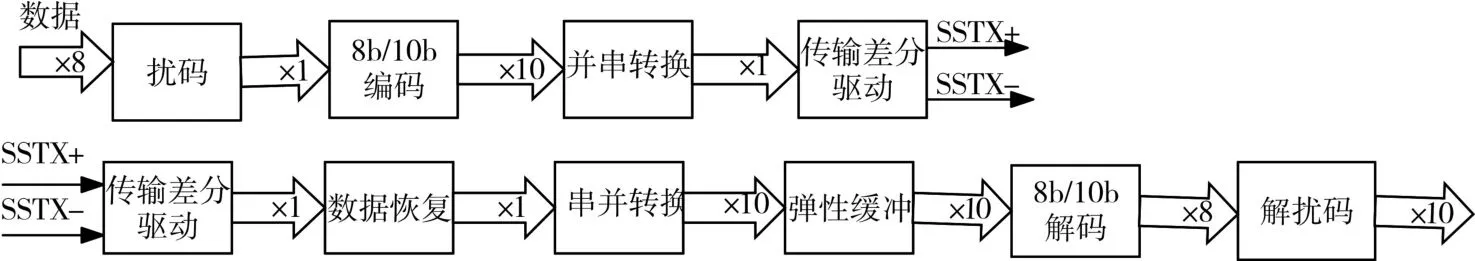

如图2所示,加扰器与解扰器应用于USB3.0通信系统的物理层的数据发送与接收流程中。

图2 数据发送/接收流程

在数据发送过程中,从链路层接收数据进行扰码、8b/10b编码、并串转换后经差分传输驱动端送到物理线路上。在数据接收过程中,数据经差分传输驱动接收后进行数据与时钟恢复,然后串并转换,经过弹性缓冲器进行时钟匹配,再进行8b/10b解码,最后解扰码后将数据送到系统其他部分。由此可见,扰码与解扰码在USB3.0通信系统中起到重要作用[7]。

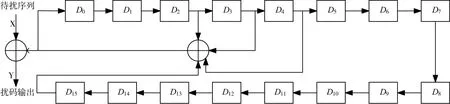

USB3.0通信协议对加扰和解扰做了具体的要求,加解扰都是以双字的形式进行处理,产生m序列的线性反馈移位寄存器要求采用生成多项式:G(X ) =X16+X5+X4+X3+1。扰码的其他的规则如下:1)除了SKP,其他数值在线性反馈移位寄存器中要串行步进8个移位;2)除了在训练序列集中的数据码不需要进行扰码处理,其他的8b/10b数据码要被扰码;3)K(控制)字符不进行扰码处理;4)线性反馈移位寄存器的初始值是FFFFh,在COM字符离开发送端的线性反馈移位寄存器后,发送端的线性反馈移位寄存器要进行初始化;每当COM字符进入接收端的线性反馈移位寄存器,接收端的线性反馈移位寄存器要进行初始化[5]。数据加扰器和解扰器的结构分别如图3和图4所示。

图3 数据加扰器结构

图4 数据解扰器结构

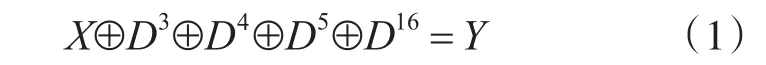

图3中的数据每经过一次移位,在时间上就会延迟一个码元时间,时间延迟用运算符号D表示,设X和Y分别表示待扰序列输入和扰码序列输出,由图3可得

用 D3⊕D4⊕D5⊕D16对式(1)两边同时进行异或运算:

由于序列自身异或等于0,可得:

根据图4的数据解扰过程,很明显可以看出:

式(4)与式(3)是相同的,这也表明解扰器能成功恢复出原待扰序列。如果直接用上述方法进行加扰与解扰,明显效率很低,所以需要对其改进。

4 改进的加扰器与解扰器电路设计

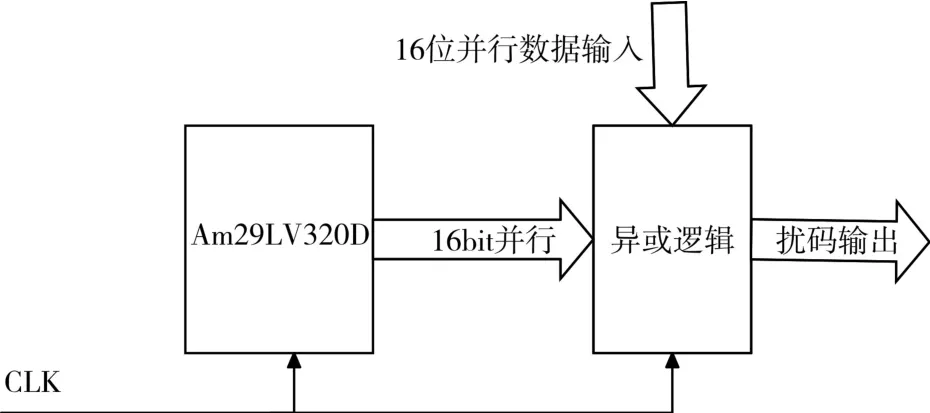

本设计采用EP4CE15F17C8N型号FPGA开发板,开发板中嵌入了一个32M的并行FLASH,其名为Am29LV320D,它可以同时进行8位或者16位数据的并行处理,并且具有安全可靠,高性能,低功耗的特点[9]。16位的移位寄存器共有216=65536个状态,我们将每个状态的最后一位取出存储在FLASH中,所需要的存储空间为65536/1024=64kbit。如图5所示,64kbit的数据固定存储到Am29LV320DFLASH中,将待扰的数据进行串并转换成16位并行数据,按照时钟的节拍,两者进行异或,即可完成16位的并行加扰。从之前所述可知,数据流进入线性反馈移位寄存器中进行加扰和解扰的算法相同,因此把加扰后的数据经过同样的电路就可以解扰出原始的输入数据。

图5 16位并行扰码结构示意图

5 仿真结果

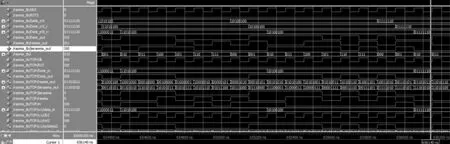

基于以上所述,本设计采用Verilog硬件编程语言编写测试文件,并结合Modelsim工具对电路进行功能仿真。电路仿真结果如图6所示,其中,clk5表示时钟信号,rst5表示复位信号。USB3.0协议中,规定线性反馈移位寄存器的初始值为OxFFFF。图6的仿真实验波形显示,电路的信源输入为Date_in5,经过两个时钟的缓冲后进行扰码,raoma_out为扰码后的输出,jieraoma_out为解扰码后的输出。观察仿真波形图可以看出,数据经过扰码后再通过解扰码又恢复成了原来的信源数据,而且数据扰码器的采用减少了信道中可能出现的连续“0”或连续“1”和短周期序列,这样就使数据频谱中有更多幅度较大的离散线谱,有利于串行通信中数据接收过程的数据定时恢复。

图6 扰码与解扰码电路仿真结果

6 结语

本文介绍了USB3.0中扰码器与解扰码器的技术,着重介绍了如何用一种更高效的方法去设计与实现,本文所阐述的基于并行flash的方法经验证是能够成功做到快速、高效、可靠、低功耗地实现USB3.0中的扰码与解扰码。扰码技术在现实应用中广泛而重要,并行处理是必要的手段,将来的并行处理一定会更快,这样也才能满足大数据时代的需求。

[1]沈泊,温涛,孙承绶.M序列伪随机码发生器的低功耗实现[J].微电子学,1999,29(1):2-3.

SHEN Po,WEN Tao,SUN Chengshou.The low power con⁃sumption of M sequence pseudo random code generator[J].Journal of Microelectronics,1999,29(1):2-3.

[2]李永忠.现代通信原理与技术[M].北京:国防工业出版社,2010:273-279.

LI Yongzhong.Modern Communication Principle and Technology[M].Beijing:National Defence Industry Press,2010:273-279.

[3]赵光.USB3.0物理层发送端的研究与设计[D].成都:电子科技大学,2009.

ZHAO Guang.The Research and Design of The Sending on The USB3.0 Physical Layer[D].Chengdu:University of Electronic Science and Technology,2009.

[4]LEE S H,LEE P J.高速传输系统集成并行扰码器设计[C]//电气工程师学会,1988:361-364.

LEE S H,LEE P J.Integrated parallel scrambler design for high-speed transmission systems[C]//IEE,1988:361-364.

[5]USB3.0规范[S].英特尔公司,2008:60-61.Universal Serial Bus3.0 Specification[S].Intel Corpora⁃tion,2008:60-61.

[6]张羿猛,黄芝平,毕占坤,等.并行帧同步扰码器的扩充比特设计法[J].光子学报,2006,35(7):1048-1051.

ZHANG Yimeng,HUANG Zhiping,BI Zhankun,et al.The Method of Bit Expansion Design on Parallel Frame Synchronization Scrambler[J].Journal of Photons,2006,35(7):1048-1051.

[7]段俊红,韩冰,王松,等.USB3.0数据传输协议分析及实现[J].信息安全与保密,2013,12(3):124-126.

DUAN Junhong,HAN Bing,WANG Song,et al.The Data Transmission Protocol Analysis and Realization of USB3.0[J].Information Security and Secrecy,2013,12(3):124-126.

[8]陈顺林,杨万全,董庆蓉.M序列在移动通信扰码中的应用及仿真[J].现代电子技术,2002(3):27-28.

CHEN Shunlin,YANG Wanquan,DONG Qingrong.The Applicationg and Simulation of M Sequence in The Mobile Communication Scrambler[J].The Modern Electronic Technology,2002(3):27-28.

[9]付少忠,杨家韦.并行扰码和解扰的实现[J].无线电工程,2004,34(2):61-63.

FU Shaozhong,YANG Jiawei.The Implementation of Par⁃allel Scrambler and Descrambler[J].The Radio Engineer⁃ing,2004,34(2):61-63.

[10]易茂祥,章浩,郭红卫,等.m-序列扰码技术及其在SATA中的应用[J].微电子学,2012,42(4):502-505.

YI Maoxiang,ZHANG Hao,GUO Hongwei,et al.M-se⁃quence Scrambler Technology and Its Application in SA⁃TA[J].Journal of Microelectronics,2012,42(4):502-505.

[11]林浒,张荣茂.FPGA的设计与开发[J].小型微型计算机系统,1992,13(12):10-15.

LIN Hu,ZHANG Rongmao.The Design and Develop⁃ment of FPGA[J].The Small Microcomputer System,1992,13(12):10-15.