一种管用分离的实时性在线硬盘加密系统设计与实现∗

2018-03-20赵光东易子林张建国

徐 渊 赵光东 易子林 张建国 谢 刚

(1.深圳大学信息工程学院 深圳 518060)(2.深圳市振华微电子有限公司 深圳 518000)

1 引言

不安全的信息是危险的。21世纪是信息的社会,保护好内部敏感信息才能避免个人、公司、企事业单位、政府部门以及军队遭受重大损失,不失去竞争优势。因此,信源保密方向的课题具备了广泛的应用领域和市场适应性。目前,防病毒、防火墙等产品确实占据了中国本地信息安全市场90%的份额,但这些产品都有一个共同的缺点:防外不防内。内部信息如何进行保密,也即信源的保密,已经成为信息安全管理的难题。文献[1~2]提出完善管理和相关的政策来提高信息的安全性,文献[3]中提到不能忽略人为因素在信息安全中的影响,虽然威胁信息安全的方式多种多样,但是文献[4]中指出攻击类型仍然是极其相似的。为了确保信息的安全,文献[5]直接把加密模块嵌入到存储器中,这种方式占用太多的逻辑资源,而且存储效率太低。

信息安全保密需求也是多样化的,很多单位处于这样一种管理模式:使用计算机的人不管理计算机,管理计算机的人不使用计算机,希望达到管用分离的效果,并且要使用方便,这类产品也是市场上所缺失的。为了能满足这样的一种信息安全管理需求,本文提出了一种基于FPGA的管用分离的实时性在线硬盘加密系统(以下简称加密系统),系统由整机加密卡和电子钥匙两个子系统组成。受益于FPGA的高性能数据加解密处理,以及硬件系统本身难于破解的特征,整机加密卡能够快速地对写入硬盘的信息进行全硬件的加密保护,用户在使用过程中必须要插入和整机加密卡相配套的电子钥匙,才允许访问硬盘内的信息,否则系统将不能工作。该系统已经获得中国国家密码管理局授予的商用密码产品型号证书,证书编号:SXH2016085。

2 加密系统的方案设计

2.1 安全模型

在现有的电脑架构中,硬盘是本地计算机信息存储的介质,硬盘数据的保护是关系到内部信息安全的核心问题[6]。本地信息软件安全管理工具所有运算都是基于算法密钥的[7],密钥的保护是关系到加密设备核心的问题,有非法使用者会专门针对密钥实施监控、跟踪、拦截破解、硬件克隆等暴力手段,这些非法攻击会造成密钥泄露。本文在设计加密系统时主要从以下三个问题进行考虑:

问题1:如何确保正确的启动系统。对使用者,采用物理的key进行授权,没有key不能开机。

问题2:使用中,确保key被拔走之后,计算机立刻不能工作。

问题3:关机后,保护计算机信息,确保计算机拆机后硬盘中所有数据以密文形式存在,保证信息安全,即使将硬盘挂到其他计算机下也不能被读取。所以本文采用了FPGA在线硬盘加密系统,加密处理示意图如图1右所示。

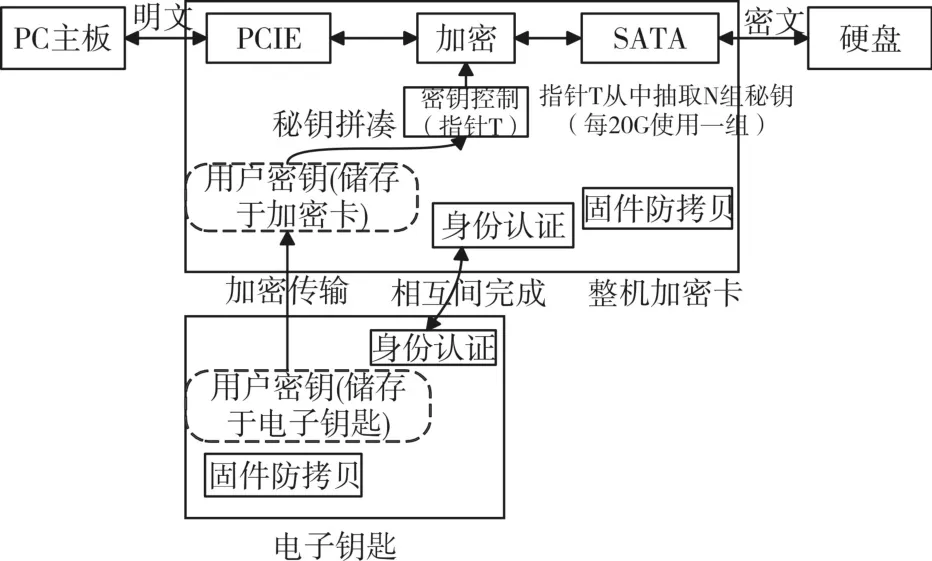

图1 硬盘数据加密示意图

该模型中包含有整机加密卡和电子钥匙,加密系统实现对PCI-E总线上传输的数据进行加密或解密操作,保证硬盘中的信息包括操作系统以密文的形式存在,并且只有在电子钥匙和整机加密卡相配合的时候该加密系统才能正常工作,功能图如图2所示。该加密系统具有安全性高、处理速度快和管理方便等多种优点,在军事单位、科研机构、金融银行系统等都有很好的应用前景。

图2 加密系统的功能原理图

2.2 身份认证

系统启动首先是整机加密卡与电子钥匙完成身份认证,身份认证在系统的工作过程中不断进行,每完成一次认证,即开始新一轮的认证。

如图3认证开始时,加密芯片A1生成的随机数A使用随机数密钥B公钥(随机数密钥B:出厂前,由电子钥匙的加密芯片B的加密算法模块生成,私钥存储在电子钥匙的加密芯片B,公钥存储到整机加密卡的加密芯片A1)加密后,以密文的形式发送到电子钥匙,并在电子钥匙的加密芯片B使用随机数密钥B私钥恢复出随机数A的明文。

加密芯片B生成随机数B,附加在随机数A的明文后面组成(随机数A+随机数B),(随机数A+随机数B)使用随机数密钥A公钥(随机数密钥A:出厂前,将私钥存储在电子钥匙的加密芯片A1,公钥存储到整机加密卡的加密芯片B内)加密后,以密文形式发送到整机加密卡,整机加密卡的加密芯片A使用随机数密钥A私钥恢复出(随机数A+随机数B),整机加密卡恢复出的随机数A明文对比自身生成随机数A是否一致。

图3 系统逻辑框图

对比一致后,(随机数A+随机数B)使用随机数密钥B公钥加密后,以密文形式发送到电子钥匙上,电子钥匙使用随机数密钥B私钥恢复出(随机数A+随机数B),电子钥匙恢复出的随机数B明文对比自身生成的随机数B是否一致,一致则认证通过。身份认证通过后,在电子钥匙的用户密钥才会进行加密传输及拼凑。

2.3 用户密钥的生成、存储、传输与拼凑

处理进出硬盘数据的密钥称为用户密钥,同一套系统中的用户密钥有M组,系统工作时只选用其中的N组(N的大小取决于硬盘空间大小):以20G的硬盘存储容量为一个区间大小划分整个硬盘,分成N个区间,每一区间使用不同的密钥(共N组),加密模块根据物理地址(扇区地址)落在的区间而选择启用对应的密钥处理数据。每套系统在出厂时由厂家的密钥管理系统生成M组Pbit的密钥组成一个密钥列表,为了解决重放攻击问题,密钥管理系统加密M组用户密钥后,将密文拆分成5部分并分发到电子钥匙FPGA FLASH、电子钥匙加密芯片B内部FLASH、整机加密卡FPGA FLASH、加密芯片A1,A2内部flash上存储。

整机加密卡与电子钥匙认证通过后,加密芯片A1接收其余4部分的用户密钥(列表)密文并合并成完整的用户密钥列表(Pbit×M)密文后。使用用户密钥(列表)分发密钥恢复出用户密钥(列表)明文,然后使用A1存储的用户密钥(列表)传输密钥,加密用户密钥(列表)的明文,用户密钥(列表)以密文方式传输给FPGA。FPGA从各个芯片接收用户密钥(列表)传输密钥分量并拼凑出完整的用户密钥(列表)传输密钥,恢复出从加密芯片A1传输过来的用户密钥(列表)明文。明文加密获取指针T作为一个索引,从M组密钥列表中获取得到N组用户密钥,供加密模块处理硬盘数据:加密模块根据硬盘的物理地址所落在区间而选择对应的用户密钥处理数据(用户密钥列表的加密传输、拼凑,每次上电只进行一次,发生在整机加密卡与电子钥匙第一次身份认证通过后)。

2.4 固件防拷贝

在整机加密卡及电子钥匙的FPGA内各自完成;产品在出厂前会将自身的DNA写在FPGA程序上并存储在SPI Flash。产品上电时,DNA是FPGA内上电后从自身内部电路获取的一个ID。在FP⁃GA开发过程中将当前FPGA的DNA嵌入到FPGA的代码中,作为硬件代码的一部分(一个常量);FP⁃GA每次上电后都从DNA模块读取当前FPGA的DNA,与硬件中的DNA常量进行对比,即可判断当前的FPGA固件是否是针对当前这片FPGA的,即每套产品的FPGA固件都是不一样的,只针对当前FPGA。这是FPGA内自身固件防拷贝检测。

在本加密系统中利用加密芯片的安全性以及FPGA的DNA、eFuse[8]技术设计了固件不可复制功能。其中加密芯片A1的功能是生成随机数握手认证、储存、恢复密钥和作为随机数源,加密芯片A2功能是储存密钥,加密芯片B功能主要是实现加密密码算法,进行身份认证,以及储存部分用户密钥。

3 加密系统的具体实现

本加密系统是在硬盘和电脑主板通信的过程中嵌入加解密处理器,该加解密处理器由整机加密卡和电子钥匙组成,系统的框架图如图3所示。

3.1 整机加密卡的实现

整机加密卡的设计包括AES加密模块的设计、SATA HOST及PCIE×1控制器的设计、PCIE与SA⁃TA的协议转换模块设计、分扇区加解密体系的设计、整机加密卡与电子钥匙之间的身份认证设计和固件防拷贝设计。

由于SATA和PCIE都是高速需要高速串行的物理接口,选用Xilinx的Spartan6 XC6SLX150T-3FGG484芯片;该芯片具有高速的串口接收和发送器GTP,可以为该设计提供单片化低成本解决方案。

整机加密卡上的FPGA设计资源使用情况如表1所示,在消耗下述资源的情况下,FPGA芯片内的设计的主频可达到124MHz。

表1 整机加密卡上FPGA芯片内设计消耗的资源

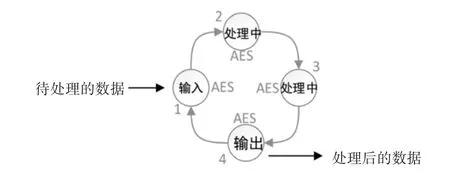

3.1.1 AES加解密模块设计

当数据在计算机其他部分和硬盘之间交互时,采用 AES[5,9~10]算法对数据进加解密处理,为了保证整机加密的吞吐量能满足要求,AES算法被设计成多核并行流水线模式。AES对SATA主设备写入SATA从设备的数据进行加密操作和对SATA主设备读取SATA从设备的数据进行解密操作。加解密处理器的结构包含了4个基于AES算法的硬核,并基于4个硬核实现了对数据进行流水线处理,提高了整机加密速率。AES流水线结构实例化了4个AES算法核,如图4所示,在当前时刻,输入Pbit的数据给核1(AES),核2及核3正在整机加密中,核4正在输出处理完毕的数据。当核1输入完毕数据后,即达到核2的位置进行整机加密,原来核2的位置就会达到核3的位置仍然进行整机加密,而核3达到核4的位置输出处理完毕的数据,原来核4就会回到核1的位置进行数据输入,以上4个核的位置变化是同步的,可以做到连续地输入数据、输出数据,从而达到流水的效果。

图4 AES流水线结构

把硬盘数据给AES的流水线结构进行处理,是两种类型的状态机联动的结果,如图5所示;左边的状态机是“整机加密状态机器”,是主状态机,主要功能是获取命令地址、选择相应的用户密钥、判断数据流向即确定加密或解密,以及把数据按照一定的规则传送给AES进行处理;右边的状态机是AES“流水线结构内的状态机”,是从状态机,其主要功能是根据“数据处理状态机器”的AES_slect控制信号,选择把数据给到相应的AES运算核。

图5 整机加密主、从状态机

3.1.2 SATA HOST及PCIE×1控制器的设计

通常,SATA协议的整体结构由物理层,链路层,传输层和应用层组成[11~12],在整机加密系统的整体结构设计中对SATA的四层体系结构进行优化后,只保留了物理层和链路层,没实现传输层及应用层,这两个简化的控制器最关键的功能是实现对命令、命令反馈的传递,SATA命令及命令反馈只需原封不动在FPGA内的主机及设备之间传输,数据则需要先被加/解密处理在主机及设备之间传输。SATA信号经过物理层及链路层两个协议层的解便可以被识别为命令或数据,所以适配于本加密系统的SATA控制器只需要链路层及物理层。这样设计提高FPGA资源的利用率,以及最大限度地增强本加密系统的兼容性,因为兼容性的关键在于对命令的响应上,而此处直接把命令及命令反馈传递不作处理。

PCIE×1控制器亦是在FPGA内实现的满足PCIE协议的控制器,在本系统中,调用第三方IP实现[13]。

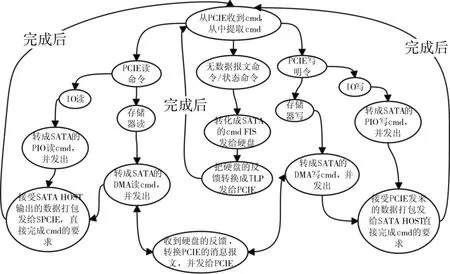

3.1.3 PCIE与SATA的协议转换模块设计

根据本加密系统的方案,PC读写硬盘的命令、数据,是在PCIE与SATA控制器之间进行传递的,因此,在FPGA内PCIE发送给 SATA HOST、SATA HOST发给PCIE的数据或命令都需要经过这两种协议之间的相互转换。在整机加密卡的FPGA内实现了PCIE与SATA协议之间的转换,其状态转换图如图6所示。

图6 PCIE与SATA协议转换模块的状态机

由于PCIE包含了读写存储器、I/O读写、配置读写、消息请求等,所以在PCIE协议转到SATA协议过程中按照表2所示进行转换。

表2 PCIE与SATA之间的协议转换

3.1.4 分扇区加解密体系的设计

分扇区加解密体系的内容包括:根据硬盘物理地址选择相应的密钥;用户密钥列表的生成、存储、传输及拼凑。详见2.3节。

AES算法模块根据硬盘的物理地址落在的范围从而选择相对应的密钥;在本系统中硬盘的物理地址从0开始,每20G使用一个密钥,因此系统中的用户密钥个数跟硬盘的大小有关。

用户密钥的使用:当整机加密卡FPGA恢复出从加密芯片A1传输过来的用户密钥(列表)明文时,由指针T从这M组密钥中提取N组密钥中的第一组,然后按顺序从密钥列表中获取剩下的N-1组用户密钥,如果到了密钥列表的结尾还没获取完毕N组,则循环到密钥列表的第1组中获取;其中指针T是用户在全盘格式化时由随机数模块提供的随机数,指针T将会作为FPGA的一个参数被eFuse加密存储到SPI flash中,以后每次上电FPGA都会从SPI flash中获取T的值,从而可以从密钥列表(Pbit×M)中找到用户密钥的N组用户密钥,T值在用户全盘格式化时更新。

3.1.5 整机加密卡与电子钥匙之间的身份认证设计

系统的使用需要整机加密卡与电子钥匙通讯[14]完成身份认证,其原理详见2.2节,其设计流程如图7所示。

图7 身份认证设计流程

3.1.6 固件防拷贝

每一片FPGA的DNA都是57bit的,两片FP⁃GA的DNA拼凑在一起也只有114位,而系统中需要的是Pbit的DNA,因此在本系统中按照这样的规则进行拼凑:假如整机加密卡的DNA是K1、K2、…、K57,钥匙的DNA是 L1、L2、…、L57,那么Pbit的DNA按照如下规则来组织:

K1、L1、K2、L2、…、K57、L57、K1、L1、K2、L2、…、K7、L7。

3.2 电子钥匙控制器的实现

电子钥匙作为管用分离的计算机加密系统的信息准用凭证,电子钥匙首先接收整机加密卡的信息,然后电子钥匙生成不可复制的认证信息,回传给整机加密卡进行身份认证。在与整机加密卡完成认证后,电子钥匙对存储于电子钥匙内的用户密钥列表进行加密,密文发送给整机加密卡。其功能原理图如图3所示,上电后整机加密卡主动将数据传输至电子钥匙的USB device并完成数据的交互。

电子钥匙上的FPGA芯片选用的是Xilinx的Spartan6 XC6SLX16-3CSG324,在该芯片上实现的FPGA设计,FPGA芯片的内部资源使用情况如表3所示,在消耗下述资源的情况下,FPGA芯片内的设计主频可达到140MHz。

表3 电子钥匙上的FPGA芯片内设计消耗资源

4 加密系统的测试

本加密系统是专门加密硬盘的,系统部署在PC主板与硬盘之间,在完成了整机加密卡和电子钥匙的设计后,需要对本加密系统的功能和性能进行测试,本系统的测试环境配置如表4所示。

表4 测试环境配置

4.1 系统功能测试

测试系统是否正常工作,包含了在没有电子钥匙的情况、硬盘被盗取到其他电脑的情况下加密系统是否能保障硬盘信息的安全;以及硬盘作为附盘放到其他计算机的情况下硬盘中的数据安全性。

如图8(e)为整机加密系统,8(a)为在缺少电子钥匙时,仅依靠整机加密卡,无法访问加密硬盘的数据内容,将整机加密卡插入PC的PCIE插槽中,不插入电子钥匙,连接好硬盘和PC主板,开机上电后,发现PC的BIOS程序没有正确找到硬盘,并提示用户没有接入硬盘。加密系统装载完成后,插有电子钥匙的情况下能正常进入系统的画面,正常进入系统后可像往常一样操作电脑,无其他区别。可见本加密系统能正常的工作,如图8(b)。当被加密的硬盘直接插到电脑主板,开机时会显示找不到操作系统,如图8(c)。图8(d)如果把被加密的硬盘作为附盘连到其他计算机,那么可以在PC的“磁盘管理”或“我的电脑”会显示这个被加密的硬盘是一个未格式化的盘,需要被格式化才能使用。

图8 加密系统的功能测试图

因此通过以上的几种测试结果可知本加密系统的功能达到了预期:实现了对硬盘的数据的加密,并且达到管用分离的效果。

4.2 系统性能测试

4.2.1 系统的数据吞吐量测试

系统数据吞吐量的是指,加密系统在正常工作时,PC读写硬盘的速率。测试工具为CrystalDisk⁃Mark,是一个测试电脑硬盘检测工具,测试存储设备大小和测试数字都可以选择,还可测试可读和可写的速度。测试结果如图9所示,其中左图为没有进行加解密时的速度,右图为在加密系统中的测试速度。由图可看出硬盘的读写速率基本没有受到加解密处理器的影响。

图9 硬盘在加密系统中的测试

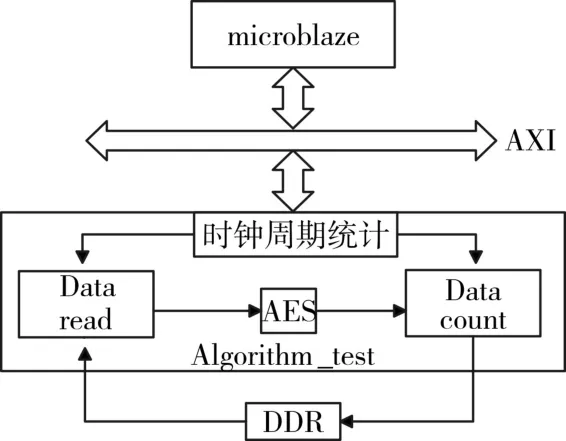

4.2.2 加密算法性能测试

此处所述加密算法性能是只在FPGA内实现的、能实际影响到产品的用户体验的算法性能,即AES算法的性能,此处只验证算法模块的性能,不包含SATA接口的性能。测试软件使用的Xilinx公司的Xilinx Software Development Kit软件,简称SDK,即软件开发套件,可以对在FPGA内实现的SOC系统进行编程、下载程序、调试程序等。测试平台如图10所示。

图10 算法测试框图

在测试系统中,把AES算法模块集成在一个叫Algorithm_test的IP里,此IP再和Microblaze组成一个SOC系统。加解密测试数据为240M byte,测试结果结果如表5所示。

表5 加密算法加解密测试

AES加解密算法,在系统时钟为150MHz的情况下,其流水线理论速率为600Mbyte,但此平台的数据不但需要从DDR读取出来,也需要把数据存进DDR,DDR的读写耗费了一些时间,所以实测性能为读写在560Mbyte左右。

4.2.3 身份认证速率测试

身份认证在本加密系统中是很重要的一个功能,其原理是电子钥匙以及整机加密卡都各自生成一个认证信息,且电子钥匙的认证信息会传输到整机加密卡内与卡里的认证信息进行对比。身份认证一次花费时间应当是两次认证之间的时间间隔。测试工具为Xilinx公司的chipscope,此工具是在线抓取、观察FPGA内部的任何信号,可设置触发条件进行抓取。

本测试的平台即是加密系统本身,为了更精确地统计到两次身份认证之间的时间间隔,身份认证模块工作在100MHz的时钟下,在身份认证模块内部嵌入一个32位宽的计数器identify_cnt,identi⁃fy_cnt的计数的开始即是一次认证信息的完成。在测试中identify_cnt统计的设计两次身份认证之间的时钟周期个数,因此每次认证时间为:时钟周期个数×10ns。

为了统计每次认证时间是否有差距,测试了50次,平均速率为55.43ms/次,1s的认证速率为18.04次。

4.3 分扇区加密功能测试

把被加密系统加密的硬盘,直接连接到第三台PC机主板上,通过winhex直接看硬盘的里面的数据,是无法看出数据是否被加密的,因为无法检测PC的操作系统到底写了一些什么或数据到硬盘的哪些地址,所以硬盘中无法判别是否启用了分组加密的功能,因此在此项测试过程中,用仿真的方式进行测试,仿真工具为modelsim,测试方式是:给AES加密模块输入连续相同的数据进行加密,并且变动不同的硬盘物理地址,判别所输出的密文是否有了变化,因而判断分扇区的加密功能是否启用。

图11中当SATA_addr变化时关于用户密钥部分的仿真结果,当硬盘物理地址由0x00000000变成0x08500000时,可以看到会导致AES加密模块的复位即core_rst=1,key_s也会根据物理地址的范围从400组用户密钥列表中获取新的用户密钥存到key_s中,图中的仿真,物理地址落在的范围是密钥的第4组,因此密钥指T即key_pointer_T=4。然后ka_key及usb_key密钥中的第4组(第0组在最前面)更新到中key_s,key_s更新完毕后即把这组新密钥输入到AES模块中更新密钥。

图11 硬盘物理地址变化造成密钥的更新

图12是另一组硬盘物理地址变化造成的密钥更新,当地址由0x08500000变成0x0E500000,AES模块会进行复位,然后更新密钥,密钥指针T即key_pointer_T=7。

图12 硬盘物理地址变化造成密钥的更新

由图11、12的仿真结果可知,当硬盘物理地址变化时,首先就会复位AES加密模块,然后根据地址范围确定指针T,由指针T从用户密钥列表中获取对应的密钥输入到AES模块。

图13 不同扇区地址加密功能仿真

如图13所示,在同一次仿真中,硬盘的物理地址变化了两次,第一次是由0x00000000变成0x08500000,第 二 次 是 由 0x08500000变 成0x0E500000,这两次的地址变化都导致AES模块重新载入相应的密钥。表6为两次不同地址数据加密的情况。

由表6可以看出在不同的硬盘物理地址情况下,会有不同的用户密钥对硬盘数据进行处理,因此达到分扇区加密的功能,同时防止了重放攻击的问题。

表6 两次不同地址数据加密的情况

5 结语

本文设计的管用分离的实时性在线硬盘加密系统,采用整机加密卡与电子钥匙两部分分离设计的办法,成功实现了管理和使用分离的设计,保证了信源信息的安全;全硬件的实现方式提高了系统的安全性,分体式存放用户密钥防止了信息安全里的重放攻击的问题,同时流水线处理进出硬盘的数据加快了系统的吞吐量,本加密系统单芯片实现,使用简单。

[1]Yang M,Zhou X,Zeng J,et al.Challenges and Solutions of Information Security Issues in the Age of Big Data[J].Wireless Communication Over Zigbee for Automotive Incli⁃nation Measurement China Communications,2016,13(3):193-202.

[2]Carcary M,Renaud K,Mclaughlin S,et al.A Framework for Information Security Governance and Management[J].It Professional,2016,18(2):22-30.

[3]Thompson H.The Human Element of Information Security[J].IEEE Security&Privacy Magazine,2013,11(1):32-35.

[4]Kessler G C.Information Security:New Threats or Famil⁃iar Problems[J].Computer,2012,45(2):59-65.

[5] Yuhao Wang,Leibin Ni,Chip-Hong Chang,Hao Yu.DW-AES:A Domain-wall Nanowire Based AES for High Throughputand Energy-efficientDataEncryption in Non-volatile Memory[J].IEEE Transactions on Informa⁃tion Forensics and Security,2016:1.

[6]谷双双,夏鲁宁,贾世杰,等.一种加密硬盘的身份鉴别和密钥保护方案[J].密码学报,2016(2):126-136.

GU Shuangshuang,XIA Luning,JIA Shijie,et al.A Pro⁃gram of Authentication and Key Protection for Hard Disk Encryption[J].Journal of Cryptologic Research,2016(2):126-136.

[7]黄志荣,范磊,陈恭亮.密钥管理技术研究[J].计算机应用与软件,2005,22(11):112-114.

HUANG Zhirong,FAN Lei,CHEN Gongliang.The re⁃search of key management technology[J].Computer Appli⁃cations And Software,2005,22(11):112-114.

[8]C.othandaraman,Sundar K.Iyer;Subramanian S.Iyer.Electrically programmable fuse(eFUSE)using electromi⁃gration in silicides[J].Electron Device Letters,IEEE,2002,23(9):523-525.

[9]Liu B,Baas B M.Parallel AES Encryption English for Many-core Process Arrays[J].Computers IEEE Transac⁃tions on,2013,62(3):536-547.

[10]Chang C J,Huang C W,Chang K H,et al.High through⁃put 32-bit AES implementation in FPGA[C]//Circuits and Systems,2008.APCCAS 2008.IEEE Asia Pacific Conference on.IEEE,2008:1806-1809.

[11]贾效玲,张刚,张博.SATA硬盘控制器的FPGA实现[J].火力与指挥控制,2016(9):182-184,188.

JIA Xiaoling,ZHANG Gang,ZHANG Bo.FPGA Imple⁃mentation of SATA Hard Disk Controller[J].Fire Con⁃trol&Command Control,2016(9):182-184,188.

[12]陈序,杨龙,孟勇,等.基于SATA接口的并行扰码实现[J].电视技术,2013,37(19):71-73.

CHEN Xu,YANG Long,MENG Yong.Implementation of Parallel Scramble Based on SATA Interface[J].Vedio Engineering,2013,37(19):71-73.

[13]Li Jun,Wang Wei,“PCI Express Interface Design and Verification Based on Spartan-6 FPGA”[C]//The Ninth International Conference on Electronic Measurement&Instruments,2009.

[14]李耀齐,蒋存波,吕鑫,等.USB总线的初始化分析[J].自动化与仪表,2007,22(3):51-54,64.

LI Yaoqi,JIANG Cunbo,LV Xin,et al.Analysis of Bus Initialization[J].Automotion&Instrumentation,2007,22(3):51-54,64.