数字化干涉仪测角技术

2018-01-30丁孝永

丁孝永 童 琼

(北京无线电计量测试研究所,北京 100039)

1引言

干涉仪测角技术具有测角范围宽、精度高、适应信号能力强、校准方便等优点,是无线电测角的重要技术之一,可将其延伸为瞬时测频技术,在无线测角领域有广泛的应用[1]。传统的干涉仪测角通常采用模拟器件,其鉴相精度由于受到器件限制普遍不高,数字式干涉仪测角采用了数字鉴相技术,较模拟器件而言,鉴相精度得到大大提高,从而提高干涉仪测角的性能。

2 相位干涉仪测角原理

干涉仪测角原理如图1所示,信号从与天线视轴夹角为θ的方向入射到天线A、E两端,电磁波达到两个天线的波程差为Dsin(θ),则由波程差引起的相位差为:

不考虑接受信道对信号的附加相移,则两个信号最后经过鉴相器就可以测出这个相位差Φ,进而可以通过角度变换得到目标信号的到达方位θ。传统的鉴相器采用模拟器件,精度差,数字干涉仪鉴相算法基于中频信号处理,相比模拟器件而言提高鉴相精度。本文采用时域数字鉴相算法。

设相邻天线接收到的信号经过解析变换后A路信号为s(t)、E路信号为s(t+τ),其中:

式中:f0——信号载频。

A路信号和E路信号的共轭相乘得:

式中:*——取共轭;Φ——相邻通道的相位差。

通过一定时间的相位累积N,可以得到精确的相位差信息。其中解析信号为Φ的离散表示为:

式中:N——信号采样点数。

对信号进行累积平均,通常直接求angle[Φ(n)],再求其平均值,如果采样为2048个点,则需分别求2048次的angle()值,然后进行平均,此方法运算量较大,通常工程上采用向量累积平均,只需要做N次向量加法,做一次angle()运算就可以了,即:

3 数字干涉仪测角的总体方案

通过对数字鉴相算法的理论分析,数字鉴相原理如图2所示。高速A/D对模拟中频信号直接进行采样,采样后的信号功分两路分别与数字本振产生的正交信号进行相乘,得到正交下变信号,分别经数字低通滤波和R倍抽取后送至数字鉴相器进行鉴相,得到所需的相位差值。

3.1 数字鉴相器的FPGA实现

文中采用Xilinx的XC6VLX240T芯片实现数字干涉仪测角,该芯片资源丰富,可满足需求。数字鉴相系统实现中,采样输入2路信号,经过正交变频,低通滤波,送入cordic IPcore计算测量两路之间的相差值,累计平均即可。实现过程中,利用了FPGA的IP Core:DDS Complier(正交本振产生),Multiplier(乘法器),FIR Complier(低通滤波器),Cordic[2]。

信号经AD采集后,在FPGA中与本地数字正交信号混频,经过低频滤波处理后,送入FPGA的cordic IP core模块,得到输入信号与本振信号的相位差。具体实现的原理框图如图3所示。

假设一路输入载波信号为 f=Asin(w0t+φ1),则其与数字正交本振混频后结果,通过积化和差公式计算可得式(7)和式(8)。对正交混频信号进行低-φ0),送入Cordic模块后,可得到相位差 φ1-φ0。FPGA实现时设置IP core属性为tan模式,可忽略幅度的影响,输出范围是[-180o180o]。

假设另一路输入载波信号为 f=Asin(ω0t+φ2),则同理可得相差φ2-φ0。将上述两路输出结果相减,可得输入回波信号的相差φ2-φ1。

同理可增加外部输入源,测量两路之间相差值。

3.1.1 采样数据处理

模拟信号经过ADC器件采样后转为数字信号,若选择采样率为1.6GHz,可对输入<800MHz的信号进行处理(若要提高输入信号的频率,可提高ADC器件的采样率)。ADC器件本身有1:2降速功能,可以将单路数据率降为800Msps,分两个端口以DDR模式输出,因此ADC向FPGA提供的源同步时钟频率为200MHz。在FPGA内,使用自带的DDR接收模块,设计约束使数据同步,以满足建立保持时间。

3.1.2 数字下变频

数字下变频实现中,采用Xilinx公司的DDS IP-core生成两路互相正交的数字本振信号,可以通过修改参量改变输出的信号频率,以适用于不同输入信号频率。乘法器选用12bit宽的multiply IPcore来实现。低通滤波器选用FIR IP core,可在matlab中设计实现滤波器系数,生成.coe文件。在IPcore的属性设置中调用此文件即可。经由滤波后输出的正交信号送入cordic模块,计算相差值。

如若改变载波频率 fc时(需满足耐奎斯特采样定理条件 fs≥2fc),可通过控制更改数字鉴相模块中正交本振信号的频点输出,这样鉴相系统可适用于不同的载波输入频率。

3.1.3 改进Cordic算法

Cordic模块的相角输出设置为25位宽的带符号浮点数,一位符号位,22位小数位,相角使用以π为单位的补码表示,理论精度可达π/222。

噪声的影响可能导致测量结果有一定的偏差,故可将Cordic模块输出的相差进行累计平均,提高算法的抗噪性,如式(6)所示。但Cordic模块输出的相角是在±π之间,由于信号的周期性,多个相角累计求和时存在一定的模糊度。比如-179°/π与179°/π之间相差2°,而在累计取平均进行相加运算时,结果为0,影响了正确测量。为解决跨周期的模糊问题,我们采用比较方式,将需要累计的数据Pi都与第一个数据P1相减求差,若差值大于π,则将其Pi减去2π;若差值小于-π,则将其Pi加上2π。通过上述处理后的Pi值再进行累计取平均运算,得到精确的相角值。将得到的相角值,进行相减运算,可得到输入信号载波的相差值。

FPGA系统时钟采用200MHz,整个过程的流水延迟59级,速度快且精准,将FPGA中获取的相差值φ2-φ1,由式(1)可计算干涉仪信号入射角度θ。

3.2 扩展应用

数字鉴相器不仅可以处理连续的信号波形输入,而且可以适用于脉冲调制信号,且可以实现与上位机实时通信,进行数据处理。只需要在FPGA系统中增加数字检波模块和接口通信模块。信号经AD采集后,变成数字信号,在FPGA中进行数字检波处理可得到脉冲包络,检测到脉沿后实时进行数字鉴相,并将结果回传给上位机进行数据处理。为提高干扰性能,可在FPGA内部将实时获取的多个鉴相结果累计取平均。实现框图如图4所示。

3.2 测试结果

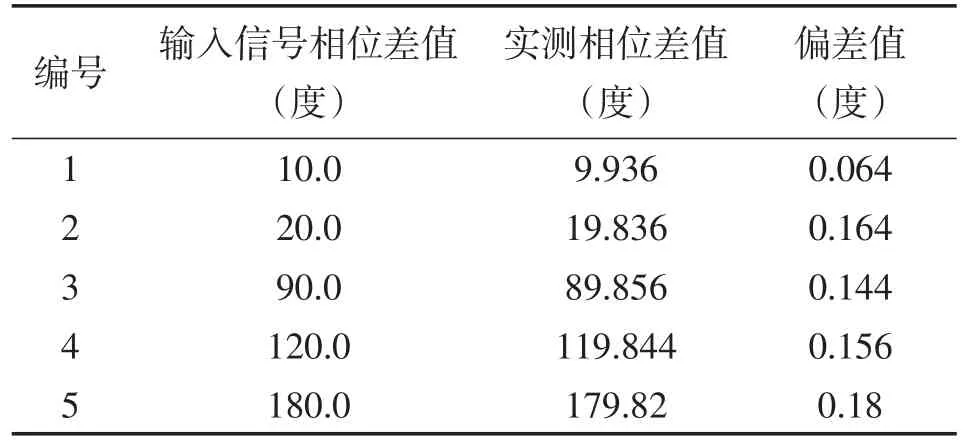

将实现的鉴相系统,应用于某被动导引头项目,以校准的方式测量相差结果,因为外部输入到鉴相系统存在固有相差,测量时需要校准。改变输入信号的相位差,鉴相系统计算获得相位差后,回传给上位机,可显示在软件界面。实际测量的相位差与理论值偏差小于0.2°。测试结果见表1。

表1 实测结果表

4 结束语

通过数字鉴相算法实现的数字式干涉仪测角[4,5]是数字接收机的关键技术,本文采用时域数字鉴相算法,在Xilinx公司的FPGA芯片上实现了双路数字鉴相,其鉴相误差小于0.2°,具有较高的鉴相精度,与传统模拟鉴相系统相比,其鉴相精度高,系统处理时间快,能够满足实时性要求,该方法可以扩展到多通道的数字鉴相系统,对多通道数字式干涉仪测角系统的研制具有重要的意义。

[1] 何晓明,赵波.基于数字干涉仪的无源测向技术研究[J].中国电子科学研究院学报,2008(05):460~463.

[2] 胡宗恺,饶志宏.高精度数字鉴相技术的FPGA实现[J].通信技术,2010,12(43):177~179.

[3] 史毅俊,朱杰.CIC滤波器的优化设计及FPGA实现.电子测量技术[J].2007,30(3):88~90.

[4] 秦明伟,李德建,姚远程.软件无线电数字下变频及抽取技术研究[J].通信技术,2008,41(09):84~88.

[5] 王雷,李玉柏,潘军.CORDIC算法在跟踪环中的应用与FPGA 实现[J].通信技术,2010,43(07):8~10.