基于FPGA的波特率连续可调的UART接口设计*

2018-01-19吴志勇郭元兴刘雨沁

吴志勇,郭元兴,刘雨沁

(中国电子科技集团公司第三十研究所,四川 成都 610041)

0 引 言

UART(Universal Asynchronous Receiver Transmitter,通用异步收发器)是一种广泛使用的低速串行接口,遵循的协议是RS-232C标准。该标准规定的典型数据传输速率为300 b/s﹑1 200 b/s﹑2 400 b/s﹑9 600 b/s﹑38 400 b/s﹑115 200 b/s等。尽管市场上有专用的UART接口芯片和IP核,但部分接口芯片和IP核仅能支持几种固定的传输速率,无法覆盖RS-232C标准规定的所有传输速率。同时,随着外接设备的日益丰富,部分设备可能具有非标准速率的UART接口,而专用的UART接口芯片及IP核无法与这些设备通信。因此,设计一种波特率连续可调的UART接口具有较高的实用价值。

1 UART原理

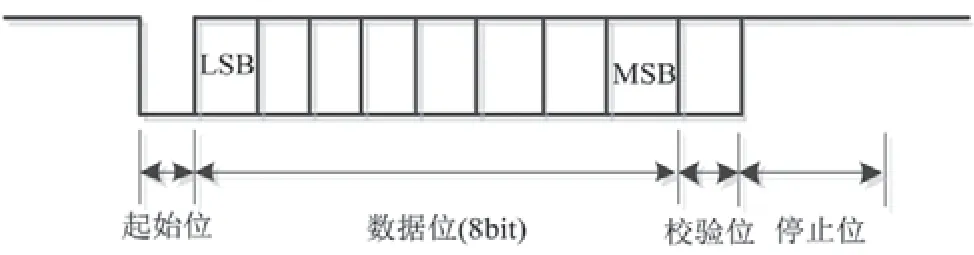

UART的具体帧格式如图1所示。每帧数据由起始位﹑数据位﹑校验位和停止位四部分组成。其中,起始位为低电平,持续一个比特时间,数据位长度可为5 bit﹑6 bit﹑7 bit﹑8bit;校验位的模式有无校验﹑奇校验和偶校验;停止位为高电平,持续时间可为1 bit或2 bit。当没有数据发送时,发送和接收引脚都保持高电平[1]。

图1 UART帧格式

发送端有数据发送时,先发送一个比特的起始位,以表示通信的开始,然后发送有效数据。有效数据的低位在前,高位在后,之后再传送校验位,最后发送停止位。

接收端处于监听状态,当监听到低电平的起始位后,就按照约定的波特率接收数据。

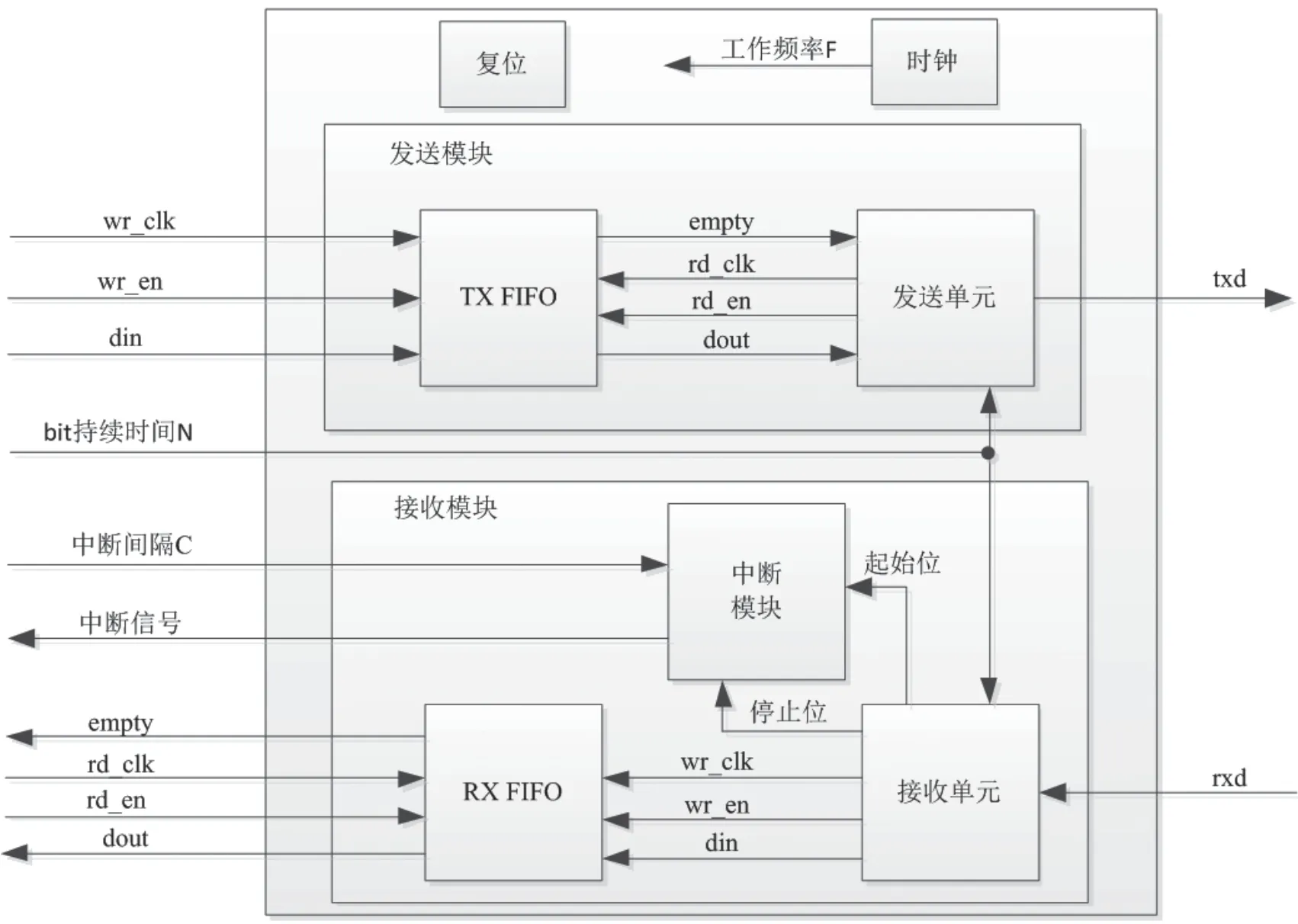

2 UART接口的FPGA实现

FPGA具有设计灵活﹑可自行定制各种电路的特点,其内部丰富的逻辑资源可让设计者充分发挥设计理念,并在设计过程中可使用VHDL语言灵活修改[2]。本设计采用Verilog HDL语言,并在Xilinx的XC6SLX150T-3FGG676I FPGA上进行验证。本设计主要包含发送模块﹑接收模块和中断模块,系统框图如图2所示。

图2 系统示例

部分UART接口的实现方式是由给定波特率来计算工作时钟频率[3-5],利用时钟频率的改变来实现波特率的切换。这种方式仅能实现有限种波特率的切换,无法实现波特率的连续可调。本设计在固定工作时钟频率下,由用户以参数的形式改变比特持续时间来实现波特率的连续可调。

比特持续时间是指在指定波特率下,传输线上单个比特持续的时钟周期数。根据波特率的定义:每秒传输字符的个数,即可计算比特持续时间N。假设UART接口的工作时钟频率为F,指定波特率为B,则可计算出比特持续时间:通过改变比特持续时间来调节波特率具有以下优点:

(1)FPGA的工作时钟频率单一,时序收敛性更好;

(2)UART接口的工作时钟频率F越高,数据传输速率的精度就越高;

(3)在UART工作频率保持不变的条件下,通过改变参数N的值就能得到连续可调的波特率;

(4)接收模块在接收每个比特时可以计数当前接收到的0和1的个数,并进行大数判决,以过滤接收线上的毛刺,提高UART接口的抗干扰能力。

2.1 发送模块

发送模块主要包含TX FIFO和发送单元。TX FIFO采用Xilinx的IP Core Generator生成,用户将待发送的数据写入TX FIFO。发送单元采用有限状态机来设计,其状态转换如图3所示。

当检测到TX FIFO非空时,发送模块从IDLE状态进入transmit状态,并读取TX FIFO中的待发送数据,在transmit状态发送一个比特数据。当处于transmit状态时,计数器count计数当前比特的持续时钟周期数。当count的值大于等于比特持续时间N时,表示当前比特发送完毕,进而判断当前数据帧是否发送完毕。如未发送完毕,则进入shift状态,将待发送数据移位,进行下一个比特发送,直到当前数据帧的停止位发送完毕,回到IDLE状态。

2.2 接收模块

接收模块主要由RX FIFO和接收单元组成。RX FIFO用于存放接收到的串口数据,采用Xilinx的IP Core Generator生成。接收单元采用有限状态机来设计,其状态转换如图4所示。

接收单元处于监听状态,当检测到接收线上的下降沿后,由IDLE状态进入start状态。在start状态中,计数器count计数时钟周期数,并统计信号线上0和1的个数。当时钟周期数大于等于比特持续时间N时,表示当前比特接收完毕,进而通过大数判决确定接收到的比特值是否为数据帧的起始位。如果是,则进入receive状态,以接收数据帧的剩余比特值;如果不是,则表示接收单元监听到的下降沿是由干扰信号引起的,将重新回到IDLE状态监听。

在receive状态接收一个比特数据,在接收每个比特值时都统计0和1的个数,并进行大数判决,以提高抗干扰能力。每接收完一个比特值就转移到shift状态,对接收到的比特值进行移位,并判断当前数据帧是否接收完毕。如接收完毕,则回到IDLE状态;否则,重新进入receive状态继续接收。

图4 接收模块状态转换

2.3 中断模块

为了避免CPU以查询方式读取RX FIFO﹑减小CPU的消耗,同时为了减少中断次数﹑提高CPU的中断效率,本设计向用户开放了中断间隔参数C。中断间隔C表示从接收完毕当前字符开始到下一个字符起始位到来之间的最小时间间隔。中断模块的流程图如图5所示。

图5 中断模块流程

假设当前字符接收完毕为t1时刻,下一个字符的起始位到来为t2时刻,计数器在t1时刻开始计数。如果t2-t1≥C,则中断模块给出中断信号,否则清零计数器。CPU接收到UART接口的中断信号后,便可连续读取RX FIFO中的数据,直到将RX FIFO读空。

3 设计验证

本文在Xilinx的XC6SLX150T-3FGG676I FPGA上进行验证,将UART接口的数据帧格式设置为8 bit数据位﹑无校验位﹑1 bit停止位,波特率为38 400 Baud,利用FPGA的时钟管理单元产生200 MHz时钟提供给UART接口工作。根据式(1)可计算得到比特持续时间N的值为5 208,即数据帧中的每个比特将持续5 208个时钟周期。设置中断间隔C的值为68 000,即从当前字符帧接收完毕开始,如果在68 000个时钟周期内仍无新的字符帧到来,则UART接口给出中断信号。采用将PC机的串口与FPGA的UART接口对接的方式来验证。

3.1 发送模块的验证

往TX FIFO写入指定数据0xAA,利用示波器抓取发送管脚上的时序,得到如图6所示的波形。

图6 发送波形

可以看出,发出数据的波特率为38 400 Baud,数据值为0010101011,即发送线上的数据为0xAA,与写入TX FIFO中的数据相符。

3.2 接收模块的验证

利用PC机上的串口工具发送数据0xAA给FPGA,同时在FPGA中利用ChipScope抓取写入RX FIFO中的数据,得到如图7所示的波形图。

图7 接收波形

从图7可以看出,写入RX FIFO中的数据为0xAA,即FPGA的UART接口接收到的数据与PC机发送的数据相同。

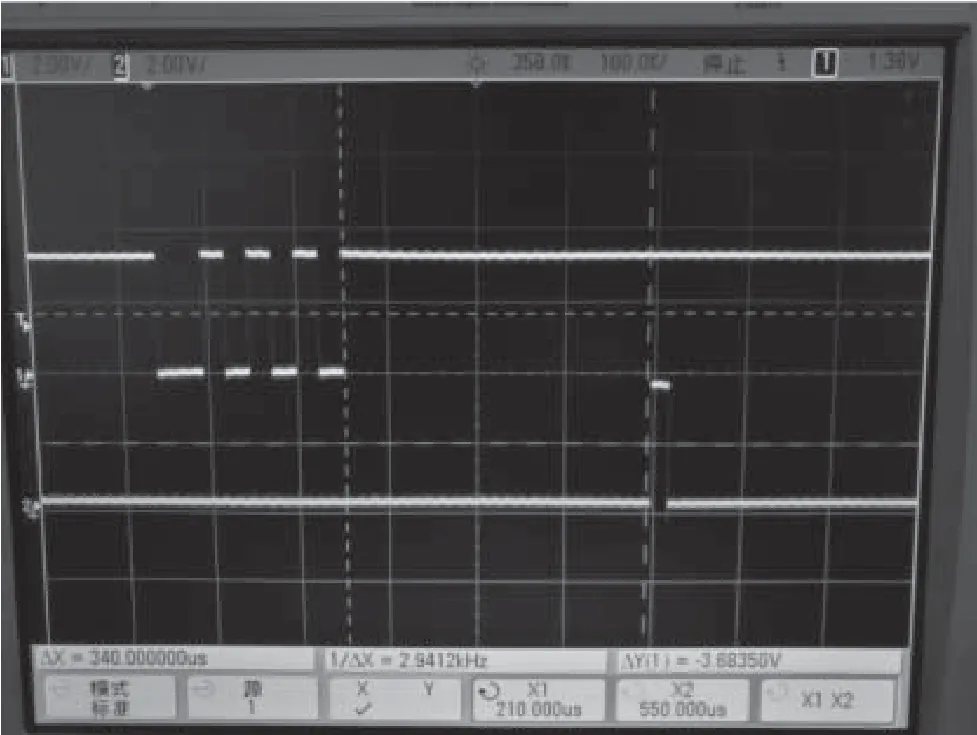

3.3 中断模块的验证

利用示波器同时抓取FPGA的接收和中断管脚的信号,得到如图8所示的波形图。

图8 中断信号波形

从图8可以测量出,中断信号在接收完毕当前字符帧的340 μs后即68 000个时钟后给出,与设定的参数值相符。

4 结 语

本文设计了一种波特率连续可调的UART接口,特点如下:

(1)固定UART接口的工作频率,通过改变字符帧的比特持续时间实现波特率的改变,并将比特持续时间作为接口参数开放给用户,设计的UART接口具有连续可调的波特率,既能产生RS-232C标准中指定的波特率,又能与具有非标准速率的UART接口通信;

(2)通过高频计数每个比特持续期间0和1的个数,采用大数判决的方式确定当前比特值,能够有效过滤信号线上的毛刺,提高UART接口的抗干扰能力;

(3)将中断间隔参数开放给用户,使用户得以自行设定UART接口中断CPU的频率,降低CPU的中断响应次数,提高了CPU的运行效率。

此外,该模块可移植到多个FPGA平台上,具有良好的推广应用价值。

[1] 赵延,葛利嘉,双涛.基于FPGA的UART设计实现及其验证方法[J].现代电子技术,2008,280(17):162-164.

ZHAO Yan,GE Li-jia,SHUANG Tao.Design and Realization of UART and Its Verification Based on FPGA[J].Modern Electronics Technique,2008,280(17):162-164.

[2] 郭晓明,张德.基于FPGA的UART设计与实现[J].电声技术,2010,34(06):31-37.

GUO Xiao-ming,ZHANG De.UART Design and Realization Based on FPGA[J].Audio Engineering,2010,34(06):31-37.

[3] 牛涛,吴斌,焦风川等.基于FPGA的UART电路的设计[J].电子测量技术,2006,29(03):73-75.

NIU Tao,WU Bin,JIAO Feng-chuan,et al.Design of a Kind of UART Circuit based on FPGA[J].Electronic Measurement Technology,2006,29(03):73-75.

[4] 何慧珠,秦丽,张会新.基于FPGA的UART IP核设计与实现[J].微计算机信息,2008,24(01-02):223-224.

HE Hu-zhu,QIN Li,ZHANG Hui-xin.Design of a UART IP Core Based on FPGA[J].Microcomputer Information,2008,24(01-02):223-224.

[5] 蒋艳红.基于FPGA的UART设计与应用[J].计算机工程,2008,34(21):225-229.

JIANG Yan-hong.Design and Application of UART Based on FPGA[J].Computer Engineering,2008,34(21):225-229.