一种通用宽带锁相频率源的设计

2018-01-05代传堂崇毓华

张 杰,代传堂,崇毓华

(中国电子科技集团公司第三十八研究所,合肥 230088)

一种通用宽带锁相频率源的设计

张 杰,代传堂,崇毓华

(中国电子科技集团公司第三十八研究所,合肥 230088)

设计了一种基于HMC833LP6GE的通用宽带锁相频率源,在25~6 000 MHz频率范围内实现输出信号频率、功率可调。该锁相环设计简洁,集成度高,功耗低,成本低,可满足多方面的需求。测试数据表明该锁相环具有优秀的杂散抑制和相噪性能。

锁相环;HMC833;宽带;单片机

0 引 言

频率源是雷达、通信、信息对抗和仪器仪表等电子系统的核心,其好坏直接影响了系统性能。[1]随着电子技术的发展,雷达等电子设备对频率源的要求越来越高,引导着频率源向宽频带、小体积、低相噪、低杂散的方向发展。本文介绍一种基于HMC833LP6GE的通用宽带锁相环。该锁相环输出频率范围为25~6 000 MHz,具有宽频带、小体积、低相噪和低杂散的特点。

1 锁相环设计

1.1 HMC833介绍

HMC833LP6GE是由Hittite公司开发的一款低噪声、宽频带的小数分频锁相环芯片[2],鉴相频率可达100 MHz,其内部集成压控振荡器(VCO),VCO输出频率范围为1 500~3 000 MHz,利用片内集成的分频器和倍频器,输出频率可扩展到25~6 000 MHz,具有极好的宽带性能。该芯片有着业界领先的相噪性能,带内典型相噪为-110 dBc/Hz,最大输出功率为3 dBm,并有9 dB的程控调节范围(3 dB步进)。

图1所示为HMC833LP6GE的功能框图。从图中可以看到该芯片的各个功能模块。参考信号由管脚XREFP输入芯片,经过R分频器,然后送到鉴频鉴相器(PFD)与来自VCO的反馈信号进行鉴相。鉴相器的输出经过电荷泵后由管脚CP输出至外部的环路滤波器,环路滤波器的输出再由管脚VTUNE输入来控制VCO。VCO的输出信号经过一个N分频器反馈到鉴频鉴相器形成锁相环路。

外部控制信号通过SCK、SDI和SEN管脚以SPI总线的形式写进芯片内部的寄存器。管脚LD_SDO为多功能管脚,可以输出内部寄存器的值,也可以配置为锁定监测输出等信号。当配置为锁定监测输出时,高电平表示环路锁定,低电平表示环路失锁。锁相环的输出频率可表示为

图1 HMC833功能框图

(1)

fout=fVCO/K

(2)

其中,fout为锁相环的输出频率;fVCO为压控振荡器的输出频率;Nint为整数部分的分频比;Nfrac为小数部分的分频比;R为输入参考信号的分频比;K是由位于VCO输出端的分频器和倍频器共同决定的一个系数,其作用在于扩展锁相环输出频率范围。

根据锁相环相位噪声理论[3],环路带宽内的相位噪声可由以下公式计算得出:

PNtotal=PNsysth+10logFpfd+20logN

(3)

其中,PNtotal为锁相环的带内相位噪声,PNsysth为锁相环的归一化相位噪声基底,Fpfd为鉴相频率,N为VCO反馈信号的分频比。对于小数分频的锁相环,分频比N等于整数部分分频比Nint与小数部分分频比Nfrac的和。以100 MHz晶振的输出信号为参考,分频比R设置为1,分频比N设置为30,系数K设置为1,此时锁相环输出3 GHz,带内相位噪声计算约为-117 dBc/Hz。

1.2 整体设计

在现代雷达系统中,有时需要的本振源数量较多,有时需要本振源具有自主跳频功能,有时需要本振源根据外部输入控制码进行跳频,造成的结果就是很多个本振源核心模块差别不是很大,但必须根据个体需求重新设计局部电路,加大了设计工作量。针对这个问题,本文对基于HMC833LP6GE的锁相环进行了一些通用性的设计,让一个模块兼顾多方面的需求。

通用锁相模块的整体框图如图2所示。除HMC833LP6GE芯片外,模块主要包括单片机、环路滤波器和放大滤波链路。单片机主要用于对锁相环芯片内部的寄存器进行配置,设置N分频比、R分频比、电荷泵电流等参数。环路滤波器对鉴频鉴相误差脉冲信号进行低通滤波处理,滤除高频分量输出直流信号,即为VCO的调谐电压。该调谐电压决定了VCO输出的信号频率。放大滤波链路对锁相环输出的信号进行放大,并对不需要的高频谐波信号进行一定程度的抑制,满足输出信号的功率电平需要。

图2 通用锁相模块整体框图

1.3 单片机设计

在本设计中,锁相环芯片内部寄存器的配置是由单片机完成的。单片机选用的是Microchip公司生产的PIC16F684ST。该单片机为14引脚,数据位宽为8位,具有2 KB的程序存储器和128字节的数据存储器。模块中预设了3个I/O端口(EN,CLK,DATA),只需进行适当的程序编写就可对输入的频率码进行译码,然后通过SPI总线对锁相环芯片内部的寄存器进行配置,达到跳频的目的。不需要跳频时,亦可以适当地编写程序来控制锁相环输出稳定的信号。总体来说,面对不同的需求,都可以通过编写程序来灵活地控制锁相环,通过两个管脚就可方便地实现在线串行编程。

1.4 环路滤波器设计

由于HMC833LP6GE内部集成了VCO,因此只需设计一个外部的环路滤波器就可正常工作。环路滤波器其实是一个低通滤波器。[4]它决定了锁相环输出信号的杂散抑制、相位噪声、锁定时间和稳定性等指标,因此设计时需综合考虑各项指标的要求。

环路滤波器分为无源滤波器和有源滤波器。无源滤波器受锁相环芯片电荷泵供电电压所限,输出的VCO调谐电压不高于电荷泵供电电压,因而无源滤波器适合VCO调谐电压较低的应用。[5]在VCO的调谐电压较高时,需使用有源滤波器。在对输入的鉴相误差信号进行滤波的同时,有源滤波器还能提供一定的增益,将调谐电压调整到合适的使用范围。有源滤波器通常需要使用运算放大器。运放会引入一定的外部噪声,从而对信号的相位噪声造成不利影响。相比之下无源滤波器全部由无源器件组成,不会影响信号的相噪。在本设计中,电荷泵和VCO的供电电压均为5 V。为了不影响相噪,利用ADS2008软件设计了一种四阶无源滤波器,如图3所示。

图3 环路滤波器

1.5 放大滤波设计

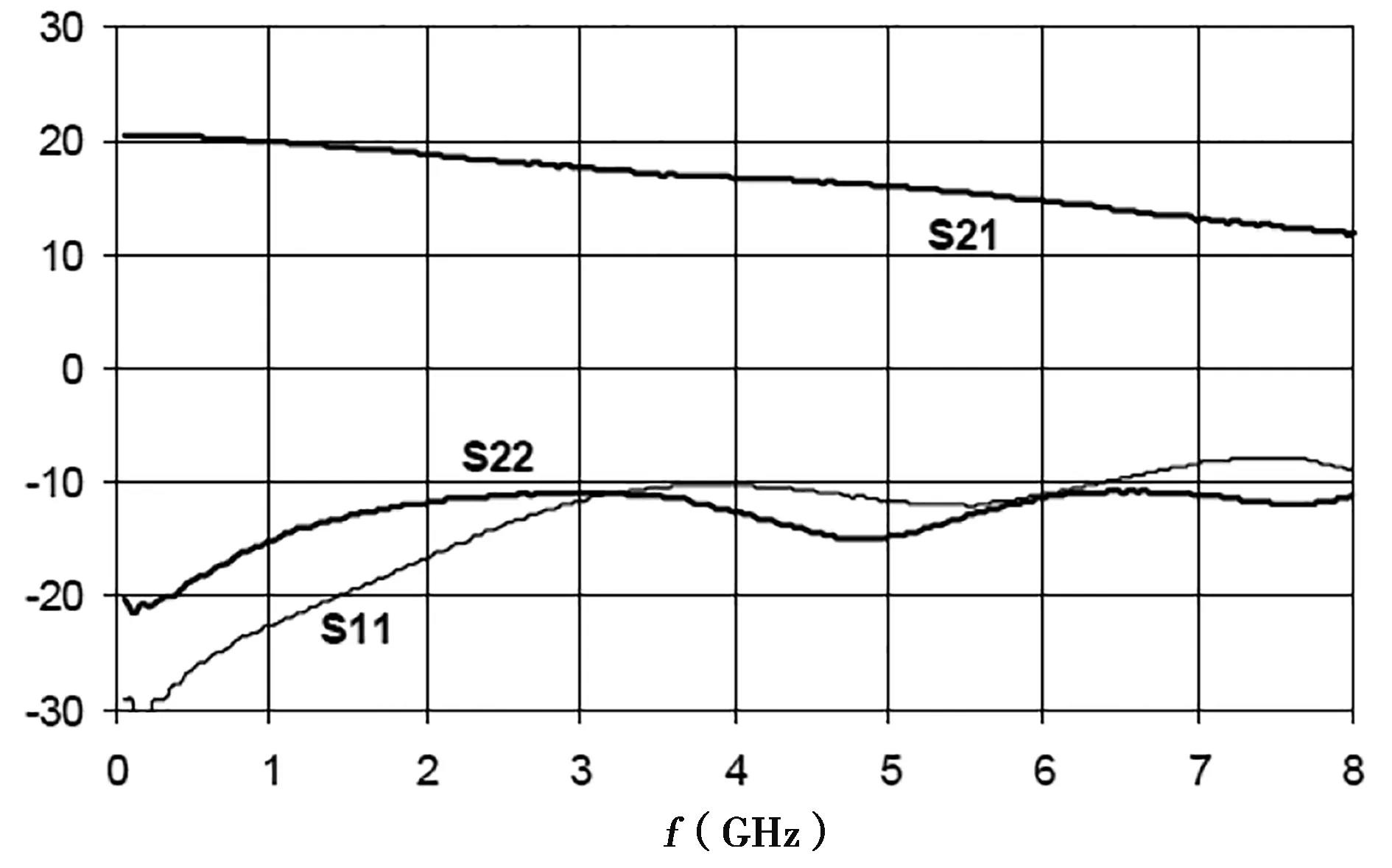

HMC833LP6GE锁相环的输出信号功率一般不超过5 dBm,往往达不到作为本振时的功率需求,因此需要对输出的信号进行放大。在本设计中,放大器选择的是Sirenza Microdevices公司生产的SBW-5089。这是一款宽带中等功率输出的放大器,工作频率范围为DC~8 GHz,在6 GHz工作频率处仍然有15 dB的增益,如图4所示。该放大器在6 GHz频率处的-1 dB压缩点功率值约为12 dBm。这就可以保证在锁相环的整个输出频率范围内信号功率可以满足中等功率本振的要求。放大器的输入端设置了衰减网络,再加上片内的9 dB衰减范围,可灵活地调整输出信号功率。在放大器的输出端还使用了一个Mini公司生产的LFCN系列低通滤波器,以滤除不需要的高次谐波。

图4 放大器SBW-5089增益曲线

2 测试结果

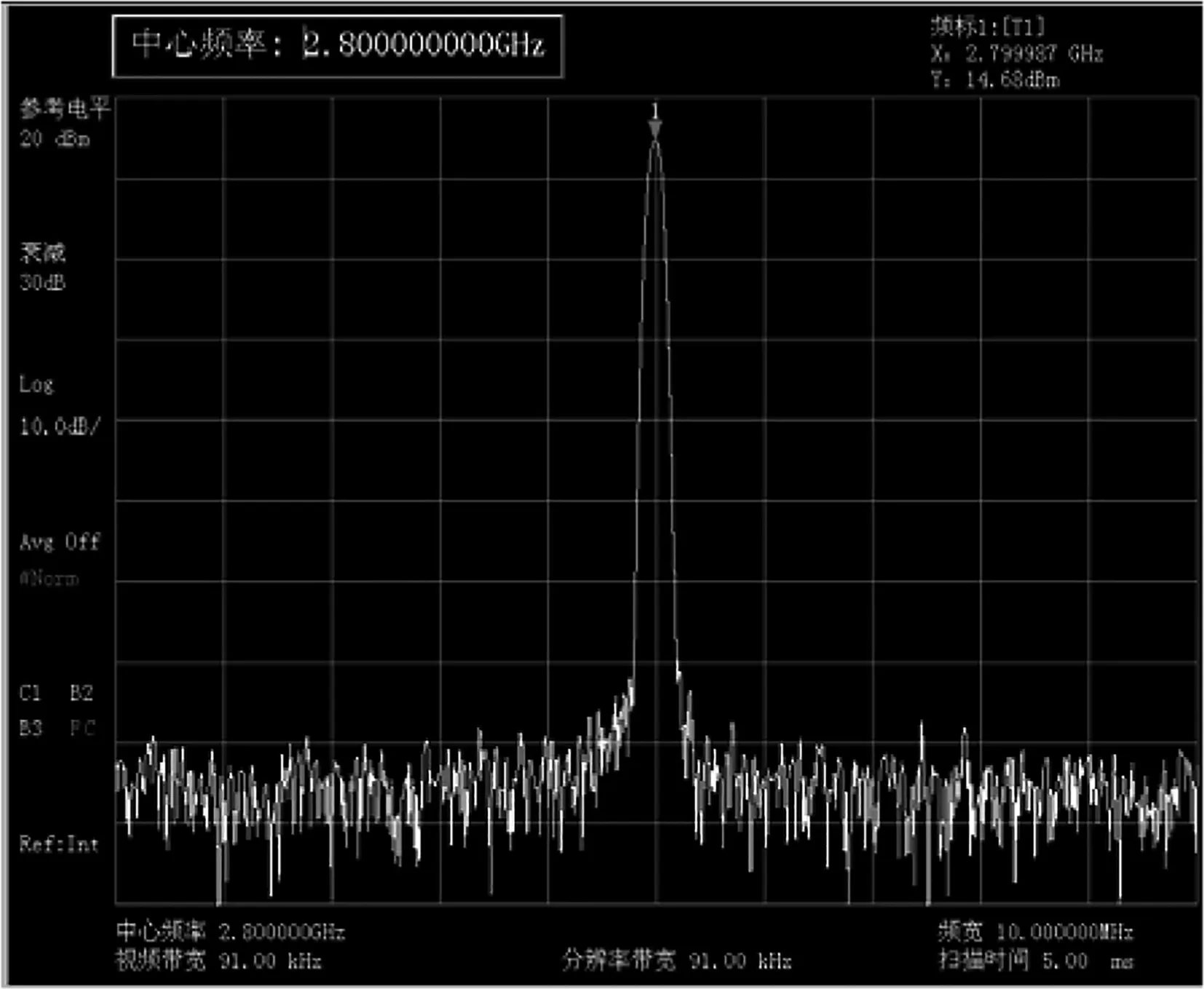

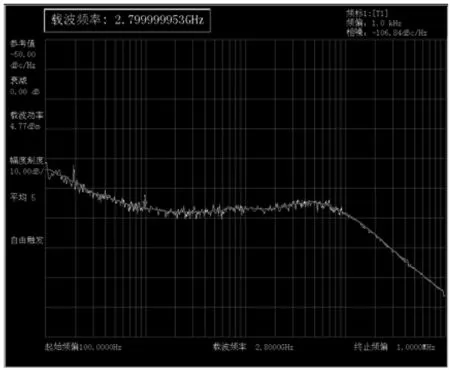

宽带锁相频率源的实物图如图5所示。根据前文的设计,利用中电四十一所生产的带相噪测试功能的频谱仪(AV4036E)对通用锁相环模块进行了相关测试。图6显示的是输出频率为2.8 GHz时的频谱图,易见该频点的杂散抑制指标优于60 dBc。图7和图8分别显示的是输出频率为2.8 GHz时的相噪仿真图和相噪实测图,在1 kHz频偏处的实测相位噪声约为-106 dBc/Hz,与仿真值-108 dBc/Hz相比恶化了2 dB,符合预期。

图5 锁相频率源实物图

图6 2.8 GHz输出频谱图

图7 2.8 GHz输出相噪仿真图

图8 2.8 GHz输出相噪实测曲线

3 结束语

本文采用内部集成VCO的锁相环芯片,设计了一种通用宽带锁相频率源。该锁相环设计简洁,集成度高,功耗低,成本低,可满足多方面的需求。测试数据表明该锁相环具有优秀的杂散抑制和相噪性能。

[1] Vadim Manassewisch. 频率合成原理与设计[M]. 何松柏, 宋亚梅, 鲍景富, 等译. 3版. 北京:电子工业出版社, 2008.

[2] Hittite Microwave Corporation. HMC833LP6GE Da-tasheet.V01.1012.

[3] Dean Banerjee. PLL Performance, Simulation and Design[M]. Santa Clara City: National Semiconductor, 2003.

[4] 远坂俊昭. 锁相环(PLL)电路设计与应用[M]. 何希才译. 北京:科学出版社,2005.

[5] 代传堂,柴文乾. 基于小数分频锁相的X波段频率合成器设计[J]. 雷达与对抗,2012,32(4):52-55.

Design of a universal wideband PLL frequency source

ZHANG Jie, DAI Chuan-tang, CHONG Yu-hua

(No. 38 Research Institute of CETC, Hefei 230088)

A universal wideband PLL frequency source is designed based on the HMC833LP6GE, with the frequency and power of the output signals adjustable from 25MHz to 6 000MHz. The PLL features simple design, high integration, low power consumption and low cost, being able to satisfy a variety of requirements. The test results indicate that the PLL has excellent phase noise and spurious suppression performance.

PLL; HMC833; wideband; MCU

TN74

A

1009-0401(2017)04-0026-04

2017-08-10;

2017-08-22

张杰(1987-),男,工程师,研究方向:频率合成器和雷达接收系统;代传堂(1981-),男,高级工程师,研究方向:频率合成器和雷达接收系统;崇毓华(1985-),男,高级工程师,研究方向:雷达接收技术与微波光子技术。